(2J) 40J3908/24-24 (22) J6.0,86 (46) 07.10.88, Бюл. № 37 (72) С.В. Казинов и А.А. В ляпло i(53) 681.325 (088.8) (56) Авторское сввдетельство СССР № 1182539, кл. G 06 F 15/31, 1984.

Авто15ское свидетельство СССР № 1241257, кл. G 06 F 15/353, 1984,

(54) МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

(57) Изобретение относится к вычислительной технике, в частности к кусочно-ступенчатым функциональным преобразователяМо Цель изобретения - сокращение аппаратурных затрат, по- вьшение быстродействия преобразователя и расширение его функциональных возможностей за счет воспроизведения функций произвольного вида. Преобразователь содержит ре гистры 1, 2, блоки 3-6 памяти, счетчик 7, вычи- татель 8, триггер 9, элемент И 10, коммутатор П, блок 12 управления. 1 з,п. ф-лы, 2 ил.

ifi

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный преобразователь | 1986 |

|

SU1401479A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Устройство для определения среднего значения выборочного размаха | 1984 |

|

SU1363252A1 |

| Функциональный преобразователь | 1984 |

|

SU1241257A1 |

| Частотный дискриминатор | 1984 |

|

SU1241142A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Вычислительное устройство | 1980 |

|

SU1001090A1 |

| Генератор случайного процесса | 1983 |

|

SU1120323A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

4 N

СО

1чЭ

00

фуг,/.

11

Изобретение относится к вычисли- ельной технике, в частности к ку- (1очно-ступенчатым функциональным лреобразователям.

Цель изобретения - сокращение аппаратурных затрат, повышение быстро- |яействия преобразователя и расшире- ие его функциональных возможностей за счет воспроизведения функций произвольного вида.

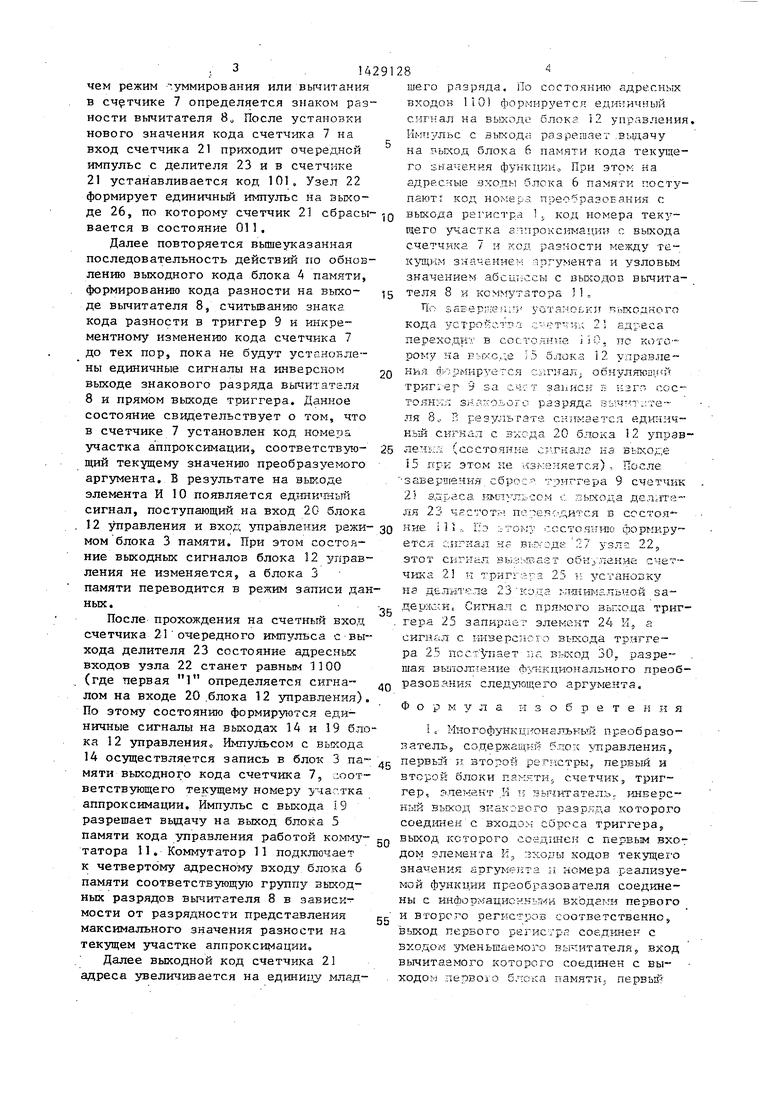

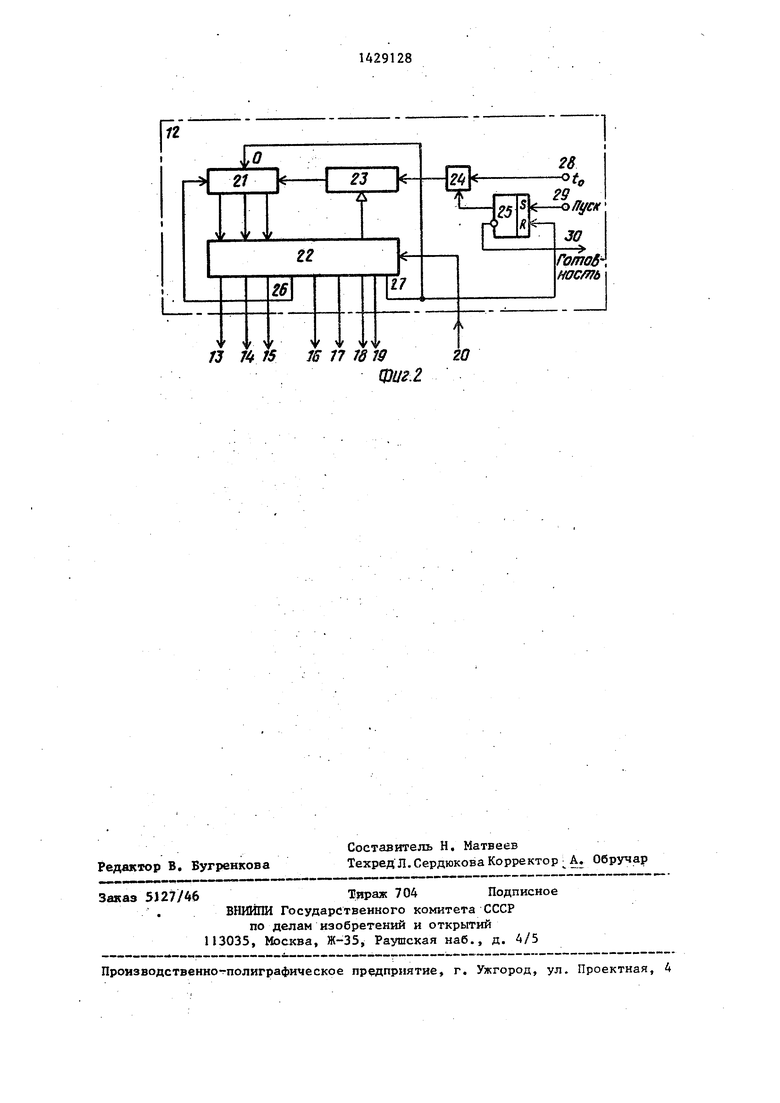

На фиг 1 приведена схема преобразователя; на фиг. 2 - возможный вариант вьшолнения блока управления.

Преобразователь (фиг.1) содержит регистры 1 и 2, блоки 3-6 памяти, счетчик 7, вычитатель 8, триггер 9, элемент И 10, коммутатор И, блок 12 управления, содержащий выходы 13- 19, вход 20, счетчик 21, постоянный запоминающий узел 22, управляемый делитель 23 частоты, элемент И 24, триггер 25, выходы 26 и 27 узла 22, тактовый вход 28, вход 29 запуска, выход 30 сигнала окончания преобразования.

Преобразователь работает следующи образом,

В исходном состоянии регистры 1 и 2, счетчики 7 и 21 и триггеры 9 и 25 обнулены, В .блок 4 памяти занесены коды узловых значений абсцисс участков аппроксимации, в блок 6 - коды выборочных значений ординат у функции на различных участках аппрок сймации, в блоке 5 - коды управления коммутатором 11 (блоки 5 и 12 памяти перепрограммируемого типа), В блок 3 памяти .занесены коды предварительной установки текущих номеров участков аппроксимации (например, нули),

Работа устройства начинается с подачи импульса запуска на вход 29 блока 12 управления. Этим импульсом триггер 25 устанавливается в единич- ное состояние и отпирает элемент И 24, Первый же импульс тактовой частоты fi проходит через элемент И 24, делитель 23 (на котором установлено минимальное время задержки) и устанавливает счетчик 21 в состояние 001 Узел 22 по состоянию адресных входов 0001 (где первый О - сигнал на входе 20, а 001 - состояния первых трех разрядов счетчика 21) формирует единичный сигнал на выходе 13 который поступает на синхровходы регистров 1 и 2, В .результате в регистр 2 заносится код текущего значения пре

0

5

0

5

91

е

j j

d

0

0

282

образуемого аргумента, а в регистр 1 (первое и второе поле данных регистра) - коды номера аргумента и номера функции.

По истечении времени записи данных в регистры 1 и 2 на выходе делителя 23 появляется импульс тактовой частоты, который переводит счетчик 21 в состояние 010. Снимается сигнал с выхода 13 и устанавливается единичный сигнал на выходе 14 блока 12 управления, поступающий на вход Выборка кристалла блока 3 памяти. Так как нулевым сигналом с выхода элемента И 10 блок 3 памяти установлен в режим чтения, то импульсом с выхода 14 блока 12 управления осуществляется считьшание кода предварительной установки номера участка аппроксимации в счетчик 7.

После установки кода в счетчике

7на вькоде делителя 23 появляется очередной импульс, которьй переводит счетчик 21 в состояние 011. По этому состоянию снимается сигнал с выхода 14 и формируется единичный сигнал на выходе 17 блока управления. Сигнал с висода 17 поступает на вход разрешения чтения блока 4 памяти.

8результате на выходе блока 4 памяти устанавливается код узлового значения абсциссы участка аппроксийации, Вычитатель 8 вычисляет разность между кодом текущего значения аргумента и кодом узлового значения абсциссы. Если эта разность отрицательная, то единица -устанавливается на прямом выходе знакового разряда вычитателя 8, если разность положительная, то единица устанавливается на инверсном вькоде, В обоих случаях состояние выходного сигнала элемента И 10 не изменяется, так как триггер 9 был обнулен перед началом цикла преобразования.

По завершении установки выходного кода вычитателя 8, счетчик 21 переводится в состояние 100 очередным импульсом с выхода делителя 23 частоты, В результате снимается сигнал с выхода 17 и фо.рмируются единичнью сигналы на выходах 16 и 15 блока 12 управления. Импульсом с выхода 15 осуществляется запись в триггер 9 состояния знака разности вьгчитателя 8, Одновременно с этим импульс с выхода 16 изменяет состояние счетчика 7 на единицу младшего разряда, при-

чем режим -.уммирования или вьгчитания в счетчике 7 определяется знаком раз нести вычитателя 8„ После установки нового значения кода счетчика 7 на вход счетчика 21 приходит очередной импульс с делителя 23 и в счетчике 21 устанавливается код 101. Узел 22 формирует единичный импульс на выходе 26, по которому счетчик 21 сбрасы вается в состояние 011 .

Далее повторяется вышеуказанная последовательность действий по обновлению выходного кода блока 4 памяти, формированию кода разности на выходе вычитателя 8, считыванию знака кода разности в триггер 9 и инкре- ментному изменению кода счетчика 7 до тех пор, пока не будут устянонле- ны единичные сигналы на инверсном выходе знакового разряда вычитателя 8 и прямом выходе триггера. Данное состояние свидетельствует о том, что в счетчике 7 установлен код номера участка аппроксимации, соответствующий текущему значению преобразуемого аргумента, В результате на выходе элемента И 10 появляется ед шитяьга сигнал, поступающий на вход 20 блока

12 управления и вход управления режи мом блока 3 памяти. При этом состояние выходньк сигналов блока 12 управления не изменяется, а блока 3 памяти переводится в режим записи даных.

После прохождения на счетный вход счетчика 21 очередного импулвса с выхода делителя 23 состояние адресных входов узла 22 станет равным 1100 (где первая 1 определяется сигна™ лом на входе 20 .блока 12 управления) По этому состоянию формируются единичные сигналы на выходах 14 и 19 блка 12 управления Импульсом с вьоюда 14 осуществляется запись в блок 3 па мяти выходного кода счетчика 7, соответствующего текущему номеру участка аппроксимации. Импульс с выхода 19 разрешает вьщачу на выход блока 5

памяти кода управления работой , татора 11. Коммутатор 11 подключает к четвертЬму адресно му входу блока б памяти соответствующую группу выходных разрядов вычитателя 8 в зависимости от разрядности представления максимального значения разности на текущем участке аппроксимации.

Далее выходной код счетчика 21 адреса увеличивается на единит у млад

шего разряда. По состоян те адре.сньгх входов 1101 формирл втся едш-тичный сигнал на вькоде блока 52 управления. Кмгп/льс с выхода разрешает .выдачу на выход блоха 6 памяти кода теку1де- го зьгачския фуккциио При этом ка адресные зходы блока 6 памяти поступают код . преобразования с выхода регистра 1 код номера текущего участка annpoKcs fai K; с выхода счетчика 7 и код разности между те- куа ним значением -.ргумента и узловым значением абсшиссы с вь ходов вычитателя 8 и ксм тутзтора 1 1 ,

Пп завер; ;е};; уатаноьки выходного кода устройст за с -ет ;и:;; 21 адреса переходит в состолнпе ii-i), пс кото- на Еухс,..;е 55 олокз 12 управления ф ;фмируется с ;гнаЛ; обнуляюв ий триг1-ег 9 за счет заинси к состояния знакового разряда зыч - тите- ля So В результате снимается едш-1ич- ный сигнал с входа 20 блока 2 управ- ленкл (состояние ст .гналг нз вькоде 15 при этом не -:з)--:еияетс.я) , Лосле завершения сброс- триггера 9 счетчик 21 адреса импульсом с лыхода дел.гге- ля 23 чгс гот:- пе/ еяодится в состоя

состоянию формиру

етсл сигнал Нс Бъпгоде узла 22, этот сигнал вызывает обк члание счетчика 2 и триггйгз 25 i; установку на делителе 23 кода г-лшимальной за- дерхсчИ. Сигнал с прямого триггера 25 запирает элемент 24 К., а сигнал с инверсного выхода триггера 25 поступает пг, вькод 30. разрешая вьа юлианне ф;.л-1кционального преобразования следующего аргумента.

Формула изобретения

i t Многофункц тональньхй преобразователь, содержащий блок ттравления, первьй и второй регнстрЫу первый и второй блоки памяти, счетчик триггер, элемент ,И i; нычитатель,. гшверс- ный вькод зиакоЕого разряда которого соедхетен с входом сброса триггера выход которого сое,д1Шен с первым входом элемента PL, зходы кодов текущег о значения аргумемта li номера реализуемой функции преобразователя соединены с инфоркационкьмй вхЬдаг-;и первого и второго регистров соответственно, выход первого регистр, соединен с входом уменьшаемого вычитателя вход вычитаемого которого соед1шен с выходом первого блока памяти- nepBarf

а|дресный вход которого соединен с вы Цодом второго регистра и адресньм входом второго блока памяти, выход Которого соединен с входом начальной : становки счетчика, выход которого Соединен с вторым адресным входом |iepBoro блока памяти, отличаю- ц и и с я тем, что, с целью сокра- цения аппаратурных затрат, повьшения быстродействия преобразователя и рас |ширения его функциональных возможнос |тей за счет воспроизведения функций Iпроизвольного вида, в него введен I третий и четвертый блоки памяти и I ког мутатор, первый выход блока управ Iления соединен с синхровходами пер- Iвого и второго регистров, второй выход блока управления соединен с вхдом Выборка кристалла второго блока памяти, вход управления режимом которого соединен с одноименным входом блока управления и выходом элемента И, второй вход которого соединен с инверсным выходом знакового разряда вычитателя, прямой и инверсный выходы знакового разряда которого соединены с соответствующими входами управления реверса счетчика, выход которого соединен с входом данных второго блока памяти и первыми адресными входами третьего и четвертого блоков памяти, вторые адресные входы которьтх соединены с выходом второго регистра, третий выход блока управления соединен с тактовым входом триггера, вход установки которого соединен с прямым выходом знакового .разряда вь1читателя, вьхкоды разрядов кода разности которого соединены с информационными входами коммутатора и третьим адресным входом третьего блока памяти, выход которого является выходом преобразователя, с четвертого по седьмой выходы блока управления соединены с синхро

5

0

5

0

5

0

5

входами счетчика первого, третьего и четвертого блоков памяти соответственно , выход последнего соединен с управляющим входом коммутатора, выход которого соединен с четвертым адресным входом третьего блока памяти.

/J 74 /5 ЛГ 77 7,

.

Авторы

Даты

1988-10-07—Публикация

1986-01-16—Подача