4

(О

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный преобразователь | 1986 |

|

SU1429128A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Функциональный преобразователь | 1984 |

|

SU1241257A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

Изобретение относится к вычислительной технике, в частности к кусочно-линейным функциональным преобразователям. Цель изобретения - сокращение аппаратурных затрат, повышение быстродействия преобразования и расширение его функциональных возможностей за счет воспроизведения функций произвольного вида. С этой целью в преобразователе, содержащем регист-. ры 1, 2, 3, блоки 4, 5 памяти, счетчик 6, вычитатель 7, триггер 8, элемент И 9, множительно-суммирующий блок 10 и блок 11 управления, изменены связи. 1 з.п. ф-лы, 2 ил.

тг.

Изобретение относится к вычислительной технике, в частности к кусочно-линейным функциональным преобразователям.

Цель изобретения - сокращение аппаратурных затрат, повышение быстродействия преобразователя и расширение его функциональных возможностей за счет воспроизведения функций про- извольного вида.

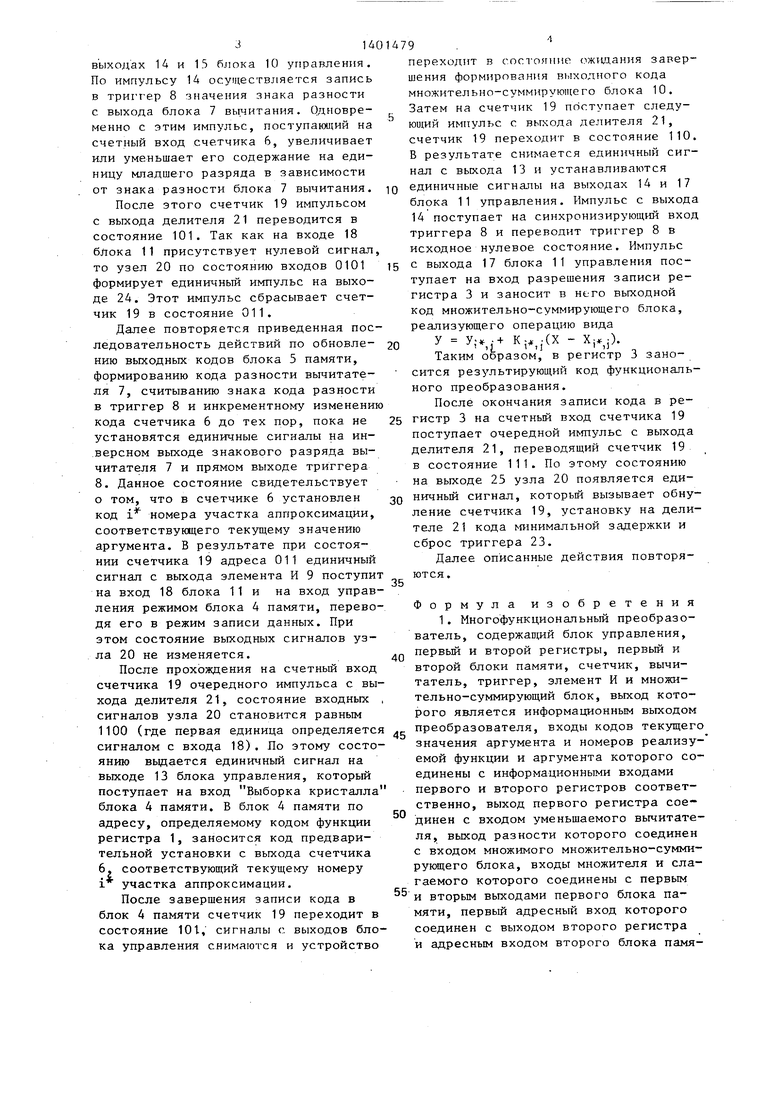

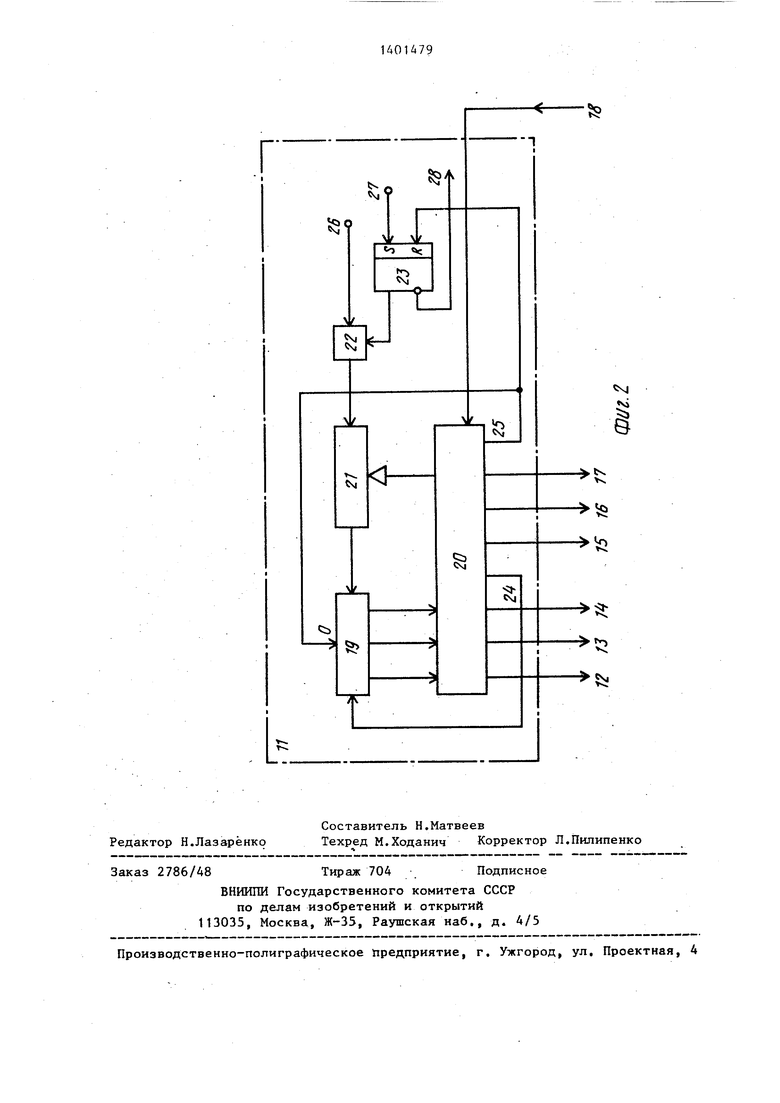

На фиг.1 показана схема преобразователя; на фиг.2 - блок управления, вариант выполнения.

Преобразователь (фиг.1) содержит первый, второй и третий регистры 1-3, блоки 4 и 5 памяти, счетчик 6, вычи- татель 7, триггер 8, элемент И 9, множительно-суммирующий блок 10, блок 11 управления, выходы 12-17 и вход 18 блока 11 управления, содержащего (фиг.2) счетчик 19, постоянный запоминающий узел 20, управляемый дели- . тель 21 частоты, элемент И 22, триггер 23, выходы 24 и 25 узла 20, так- товый вход 26, вход 27 запуска, выход 28 Признака конца работы преобразователя.

Преобразователь работает следующим образом.

В исходном состоянии регистры 1-3 и 17, счетчики 6 и 19 и триггеры 8 и 23 обнулены. В блоке 5 памяти (перепрограммируемого типа) записаны коды узловых значений абсцисс Xfj, op- динат y,- j и коэффициентов наклона Кдля различных участков аппроксимации (i -. номер участка аппроксимации) . . В блок 6 памяти (оперативного типа) занесены коды i, j - предварительной установки адресов счетчика 6 (в простейшем случае нули).

Работа преобразователя начинается с подачи импульса запуска 27. Этим сигналом триггер 23 устанавливается в единичное состояние, отпирающее элемент 22 для прохождения тактовых импульсов tg. Первьй тактовый импульс с выхода элемента И 22 проходит через делитель 21 частоты, на управляющем входе которого установлено минималь- нов время задержки, и переводит счетчик 19 в состояние 001 (здесь и далее указываются состояния первых трех разрядов счетчика 19). Поскольку в первых тактах работы преобразователя сигнал на выходе элемента И 9 отсутствует и на вход 18 блока 11 поступает логический нуль, то узел 20 по со

о

5 9 5

.

0 5

0

5

стоянию входов 0001 формирует единичный сигнал на выходе 12, длительность которого определяется кодом на управляющем входе делителя 21. Сигнал.с выхода 12 поступает на синхровходы регистров 1 и 2. В регистр 2 заносится код N текущего значения аргумента, подлежащего функциональному преобразованию, а в регистр 1 - код Nj номера реализуемой функции.

По истечении времени установления кодов в регистрах 1 и 2 на выходе делителя 21 частоты появляется импульс, переводящий счетчик 19 в состояние 010. По состоянию входов 0010 узел 20 обнуляет выход 12 и формирует единичный сигнал на выходе 13, который поступает на вход Выборка кристалла блока 4 памяти. Поскольку нулевым сигналом с выхода элемента И 9 блок 4 памяти установлен в режим чтения данных, то импульсом Выборка кристалла осуществляется считывание кода с выг хода блока 4 в счетчик 6.

По завершении установки кода в счетчике 6 счетчик 19 импульсом с выхода делителя 21 переводится в состояние 011. В результате сигнал с выхода 13 снимается и появляется единичный сигнал на выходе 15 блока 11. Этот сигнал поступает на вход разрешения чтения блока 5 памяти. На выходах блока 5 формируются коды узлового значения абсцисс Xjjf,, ординаты У jj и коэффициента наклона К -в соответствии со значениями кода адреса начальной установки i, поступающего с выхода счетчика 6, и кода номера функции j, поступающего с выхода регистра 1, вычитатель- 7 вычисляет разность между кодом текущего значения аргумента X и кодом узлового значения абсциссы X,. Если эта разность отрицательна, то единица устанавливается на прямом выходе знакового разряда вычитателя 7, если положительна - то - единица устанавливается на инверсном выходе знакового разряда. В обоих случаях на выходе элемента И 9 присутствует нулевой сигнал, так как триггер 8 обнулен по начальному состоянию преобразователя.

По завершении установки выходного кода вьп1итателя 7 счетчик 19 переводится в состояние 100 очередным импульсом с выхода делителя 2 1. В результате снимается сигнал с выхода 15 и формируются единичные импульсы на

314

выходах 14 и 15 блока 10 управления. По импульсу 14 осуществляется запись в тригг-ер 8 значения знака разности с выхода блока 7 вычитания. Одновременно с этим импульс, поступающий на счетный вход счетчика 6, увеличивает или уменьшает его содержание на единицу младшего разряда в зависимости от знака разности блока 7 вычитания.

После этого счетчик 19 импульсом с выхода делителя 21 переводится в состояние 101. Так как на входе 18 блока 11 присутствует нулевой сигнал то узел 20 по состоянию входов 0101 формирует единичный импульс на выходе 24. Этот импульс сбрасывает счетчик 19 в состояние 011.

Далее повторяется приведенная последовательность действий по обновлению выходных кодов блока 5 памяти, формированию кода разности вычитате- ля 7, считыванию знака кода разности в триггер 8 и инкрементному изменени кода счетчика 6 до тех пор, пока не установятся единичные сигналы на инверсном выходе знакового разряда вы- читателя 7 и прямом выходе триггера 8. Данное состояние свидетельствует

0том, что в счетчике 6 установлен код номера участка аппроксимации, соответствующего текущему значению аргумента. В результате при состоянии счетчика 19 адреса 011 единичный сигнал с выхода элемента И 9 поступи на вход 18 блока 11 и на вход управления режимом блока 4 памяти, переводя его в режим записи данных. При этом состояние выходных сигналов узла 20 не изменяется.

После прохождения на счетный вход счетчика 19 очередного импульса с выхода делителя 21, состояние входных сигналов узла 20 становится равньш 1100 (где первая единица определяетс сигналом с входа 18). Ло этому состоянию выдается единичный сигнал на выходе 13 блока управления, который поступает на вход Выборка кристалла блока 4 памяти, В блок 4 памяти по адресу, определяемому кодом функции регистра 1, заносится код предварительной установки с выхода счетчика 6, соответствующий текущему номеру

1участка аппроксимации.

После завершения записи кода в блок 4 памяти счетчик 19 переходит в состояние 101., сигналы с выходов блока управления снимаются и устройство

переходит в состо ние ожидания завершения формирования В11 ходного кода множительно-суммирующего блока 10. Затем на счетчик 19 поступает следующий импульс с выхода делителя 21, счетчик 19 переходит в состояние 110. В результате снимается единичный сигнал с выхода 13 и устанавливаются

единичные сигналы на выходах 14 и 17 блока 11 управления. Импульс с выхода 14 поступает на синхронизирующий вход триггера 8 и переводит триггер 8 в исходное нулевое состояние. Импульс

5 с выхода 17 блока 11 управления поступает на вход разрешения записи регистра 3 и заносит в него выходной код множительно-суммирующего блока, реализующего операцию вида

У У;,Г - i,i Таким образом, в регистр 3 зано- сится результирующий код функционального преобразования.

После окончания записи кода в ре- 5 гистр 3 на счетный вход счетчика 19 поступает очередной импульс с выхода делителя 21, переводящий счетчик 19 в состояние 111. По этоьгу состоянию на выходе 25 узла 20 появляется еди- 0 ничньй сигнал, которьй вызывает обнуление счетчика 19, установку на делителе 21 кода минимальной задержки и сброс триггера 23.

Далее описанные действия повторяются. 5

Формула изобретения 1. Многофункциональный преобразователь, содержащий блок управления, Q первый и второй регистры, первый и второй блоки памяти, счетчик, вычи- татель, триггер, элемент И и множи- тельно-суммирующий блок, выход которого является информационным выходом преобразователя, входы кодов текущего значения аргумента и номеров реализу- емой функции и аргумента которого соединены с информационными входами первого и второго регистров соответственно, выход первого регистра соединен с входом уменьшаемого вычитате- ля, выход разности которого соединен с входом множимого множительно-суммирующего блока, входы множителя и слагаемого которого соединены с первым и вторым выходами первого блока памяти, первый адресный вход которого соединен с выходом второго регистра и адресным входом второго блока памя0

514

ти, выход которого соединен с входом установки счетчика, выход которого соединен с вторым адресным входом первого блока памяти, третий выход которого соединен с входом вычитаемого вычитателя, выход инверсного разряда которого соединен с входом сброса триггера, выход которого соединен с первым входом элемента И, о т л и- чающийся тем, что, с целью сокращения аппаратурных затрат, повышения быстродействия преобразователя и расширения его функциональных возможностей за счет воспроизведения функций произвольного вида, выход элемента И соединен с входами управления, режимом второго блока памяти- и блока управления, первый выход которого соединен с синхровходами. пер- вого и второго регистров, второй выход блока управления соединен-с входом Выборка кристалла второго блока памяти, третий выход блока управления соединен с тактовым входом триггера, ,вход установки которого соединен с прямым и инверсным выходами знакового разряда вычитателя, прямой и ин- версньш выходы знакового разряда которого соединены с соответствующи1 и входами управления реверсом счетчика, выход которого соединен с входом данных второго блока памяти, четвертый и пятый выходы блока управления соединен с синхровходами счетчика и первого блока памяти, инверсный выход знакового разряда вычитателя соединен с вторым входом элемента И.

5 0 5 О

5

796

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Функциональный преобразователь | 1984 |

|

SU1241257A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-01-16—Подача