выход старших разрядов кода .адреса которого соединен с информационным входом буферного регистра, с первым информационным входом второго коммутатора адреса и с управляющим вхо дом второго мультиплексора, первый информационный вход которого подключен к входу логических условий устройства, выход второго мультиплексора соединен с информационным входом второго старшего разряда первой группы первого коммутатора адреса, информационный вход остальных старших разрядов первой группы которого соединен с выходом второго коммутатора адреса, второй информационный вход которого соединен с выходом буферного регистра, вход синхронизации которого соединен с выко дом четвертого элемента И, первый вход которого соединен с инверсным входом пятого элемента И, с управляющим входом второго коммутатора адреса и с нулевым выходом триггера условий, единичный выход которого соединен с прямым входом третьего элемента И, выход которого соединен со стробирующими входами первого и второго мультиплексоров, вторые информационные входы которых соединены соответственно с выходами первого и второго модифицируемых разрядов кода адреса блока памяти Микрокоманд, вход синхронизации триггера условий соединен с - и К-входами триггера условий, с выходом первого элемента И, с вторым входом четвертого элемента И и с прямым входом пятого элемента И, выход которого соединен с входом установки в ноль буферного регистра, выход элемента ИЛИ является выходом индикации ошибки устройства, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Программируемый контроллер | 1988 |

|

SU1624404A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1649539A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1280629A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1278847A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, первьй мультиплексор, первый коммутатор адреса, триггер пуска и генератор тактовых импульсов, причем вход пуска устройства соединен с входом установки в единицу триггера пуска, выход которого соединен .с входом запуска генератора тактовых импульсов, выход регист за адреса соединен с адресным входом блока памяти микрокоманд, выход кода микроопераций ко торого соединен с информационным входом регистра микрокоманд, выход кода микроопераций которого является управляющим выходом устройства, выход признака конца работы регистра микрокоманд соединен с входом установки в ноль триггера пуска, выход кода логических условий блока памяти микрокоманд соединен с управляющим входом первого мультиплексора, вход логических условий устройства соединен с первым информационным входом первого мультиплексора,выход которого соединен с информационным входом первого старшего разряда первой группы первого коммутатора адреса, входы младших разрядов первой группы которого соединены с выходами младших разрядов кода адреса блока памяти микрокоманд, выход первого коммутатора адреса соединен с информационным входом регистра адреса, выход признака конца команды регистра микрокоманд соединен с упо S равляющим входом первого коммутатора адреса, вторая группа информационных входов которого является группой входов кода команды устройства, отличающееся тем, что, с целью сокращения объема оборудования за счет снижения объема блока памяти микрокоманд, оно содержит буферный регистр, триггер 00 О2 условий, второй коммутатор адреса, второй мультиплексор, первый, втоQP 0 рой, третий, четвертый и пятый эле; менты И и элемент ШШ, причем первый выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд и с первым входом первого элемен. та И, второй вход которого соеди нен с инверсным входом третьего элемента И с выходом признака предшествующей ветвлению микрокоманды блока памяти микрокоманд и с первым входом второго элемента И, второй входкоторого соединен с вькодом элемента ШШ, вход которого соединен с выходом кода логических условий блока памяти микрокоманд,

1

Изобретение относится к автоматике и вычислительной .технике и может быть использовано при построении центральньк и периферийных устройств управления ЭВМ и вычислительных систем.

Цель изобретения - снижение объема оборудования за счет уменьшения объема памяти микрокоманд.

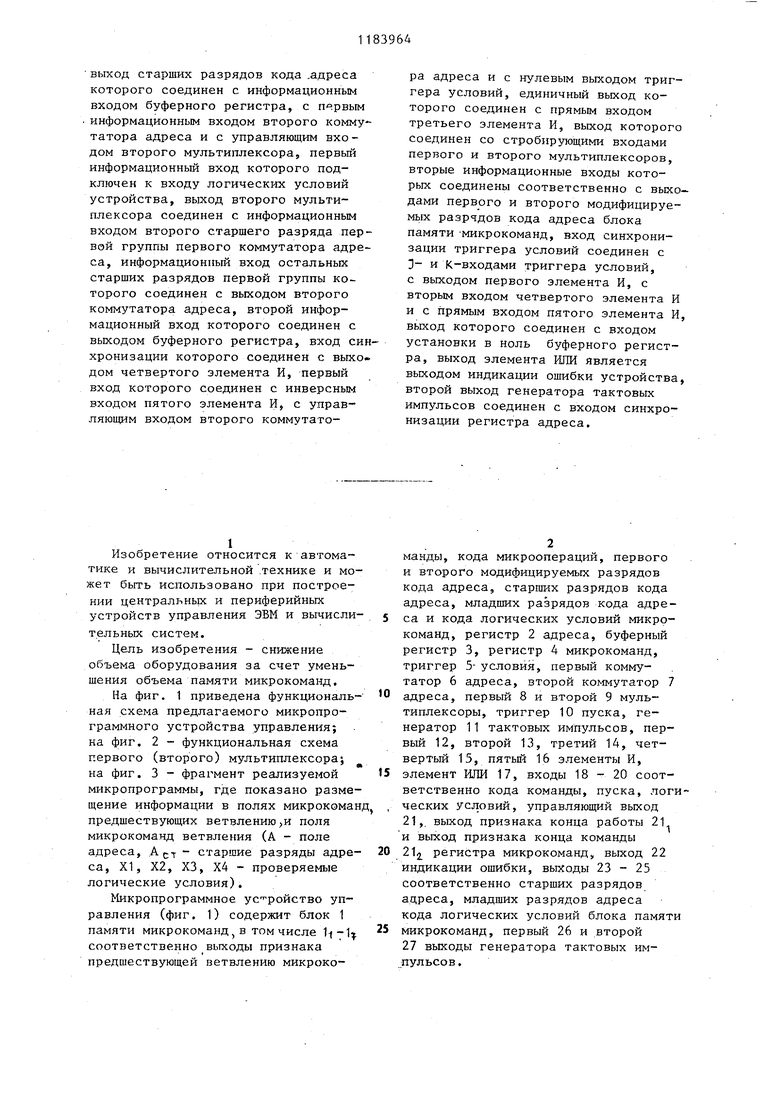

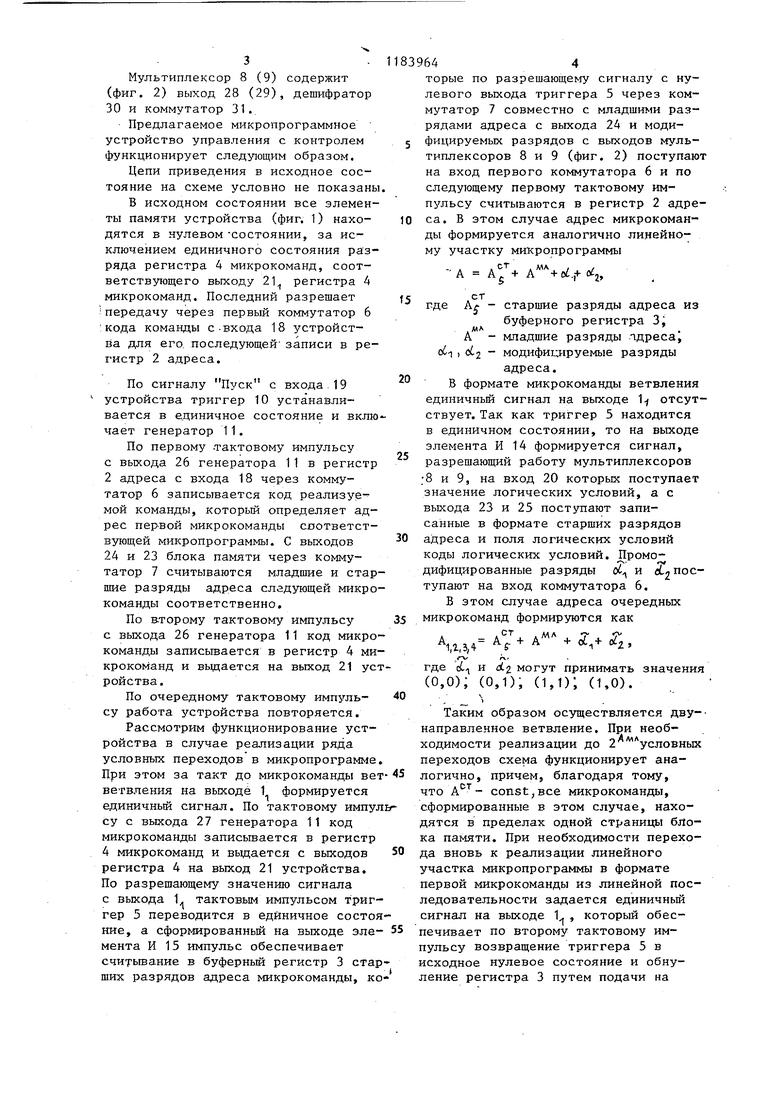

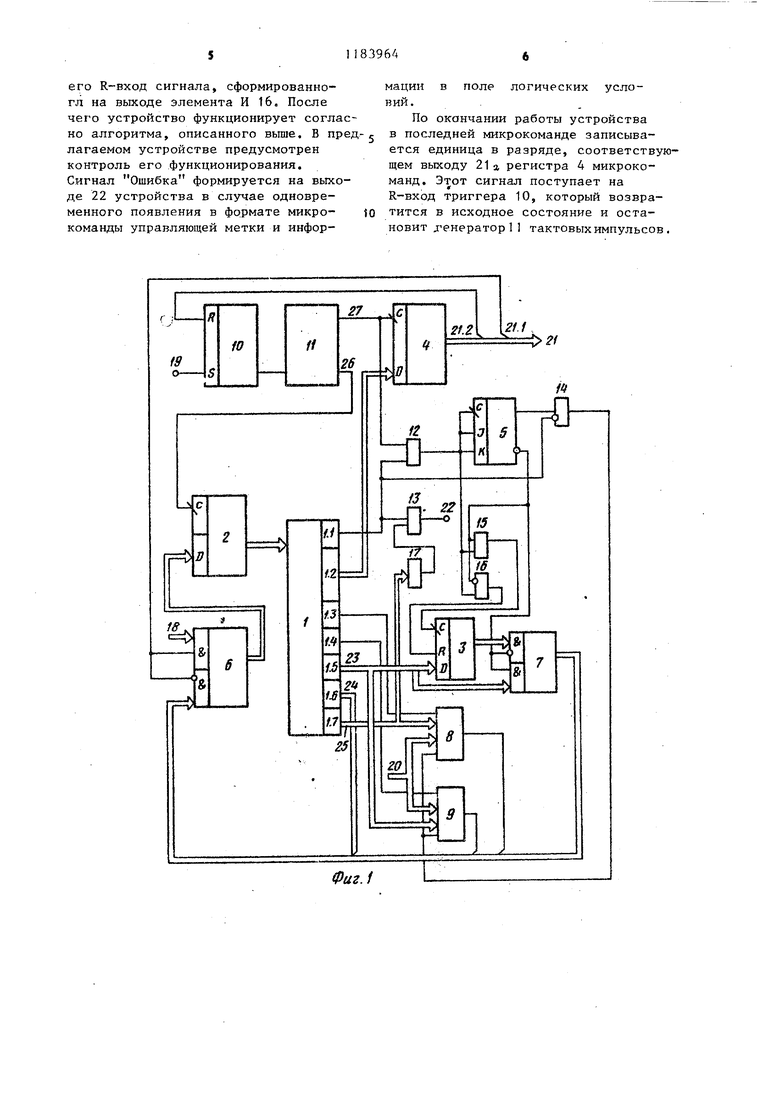

На фиг. 1 приведена функциональнал схема предлагаемого микропрограммного устройства управления; на фиг. 2 - функциональная схема первого (второго) мультиплексора на фиг. 3 - фрагмент реализуемой микропрограммы, где показано размещение информации в полях микрокоман предшествующих ветвлению,и поля микрокоманд ветвления (А - поле адреса, Aj..-y - старшие разряды адреса, XI, Х2, ХЗ, Х4 - проверяемые логические условия).

Микропрограммное ус ройство управления (фиг. 1) содержит блок 1 памяти микрокоманд в том числе 1-f-l соответственно выходы признака предшествующей ветвлению микрокоманды, кода микроопераций, первого и второго модифицируемых разрядов кода адреса, старших разрядов кода адреса, младших разрядов кода адреса и кода логических условий микрокоманд, регистр 2 адреса, буферный регистр 3, регистр 4 микрокоманд, триггер 5- условия, первый коммутатор 6 адреса, второй коммутатор 7 адреса, первый 8 и второй 9 мультиплексоры, триггер 10 пуска, генератор 11 тактовых импульсов, первый 12, второй 13, третий 14, четвертый 15, пятьй 16 элементы И, элемент ИЛИ 17, входы 18 - 20 соответственно кода команды, пуска, логческих условий, управляющий выход 21, выход признака конца работы 21 и выход признака конца команды 212 регистра микрокоманд, выход 22 индикации ошибки, выходы 23-25 соответственно старших разрядов адреса, младших разрядов адреса кода логических условий блока памят микрокоманд, первый 26 и второй 27 выходы генератора тактовых импульсов . Мультиплексор 8 (9) содержит (фиг. 2) выход 28 (29), дешифратор 30 и коммутатор 31. Предлагаемое микропрограммное устройство управления с контролем функционирует следующим образом. Цепи приведения в исходное состояние на схеме условно не показаны В исходном состоянии все элементы памяти устройства (фиг. 1) находятся в нулевом -состоянии, за исключением единичного состояния разряда регистра 4 микрокоманд, соответствующего выходу 21 регистра 4 микрокоманд. Последний разрешает передачу через первый коммутатор 6 кода команды с-входа 18 устройства для его. последующей записи в регистр 2 адреса. По сигналу Пуск с входа 19 устройства триггер 10 устанавливается в единичное состояние и вклю чает генератор 11. По первому тактовому импульсу с выхода 26 генератора 11 в регистр 2 адреса с входа 18 через коммутатор 6 записывается код реализуемой команды, который определяет адрес первой микрокоманды соответствующей микропрограммы. С выходов 24 и 23 блока памяти через коммутатор 7 считываются младшие и стар шие разряды адреса следующей микро команды соответственно. По второму тактовому импульсу с выхода 26 генератора 11 код микро команды записьшается в регистр 4 ми крокоманд и вьщается на выход 21 ус ройства. По очередному тактовому импульсу работа устройства повторяется. Рассмотрим функционирование устройства в случае реализации ряда условных переходов в микропрограмме При этом за такт до микрокоманды ве ветвления на выходе 1 формируется единичный сигнал. По тактовому импу су с выхода 27 генератора 11 код микрокоманды записывается в регистр 4 микрокоманд и выдается с выходов регистра 4 на выход 21 устройства. По разрешающему значению сигнала с выхода 1. тактовым импульсом триг гер 5 переводится в единичное состо ние, а сформированный на выходе эле мента И 15 импульс обеспечивает считывание в буферньй регистр 3 ста ших разрядов адреса микрокоманды, к торые по разрешающему сигналу с нулевого выхода триггера 5 через коммутатор 7 совместно с младшими разрядами адреса с выхода 24 и модифицируемых разрядов с выходов мультиплексоров 8 и 9 (фиг. 2) поступают на вход первого коммутатора 6 и по следующему первому тактовому импульсу считываются в регистр 2 адреса. В этом случае адрес микрокоманды формируется аналогично линейному участку микропрограммы -А .f-, сг где Ал - старшие разряды адреса из буферного регистра 3| . мл А - младшие разряды ядреса, od-i , 062 - модифицируемые разряды адреса. В формате микрокоманды ветвления единичный сигнал на вьгходе 1 отсутствует. Так как триггер 5 находится в единичном состоянии, то на выходе элемента И 14 формируется сигнал, разрешающий работу мультиплексоров ;8 и 9, на вход 20 которьк поступает значение логических условий, а с выхода 23 и 25 поступают записанные в формате старших разрядов адреса и поля логическ гх условий коды логических условий. Промодифицированные разряды oi и в(,2 поступают на вход коммутатора 6. В этом случае адреса очередных микрокоманд формируются как ...,, y-v f, где cL- и d2 могут принимать значения (0,0); (0,1), (1,1); (1,0). Таким образом осуществляется двунаправленное ветвление. При необходимости реализации до 2 условных переходов схема функционирует аналогично, причем, благодаря тому, что - const,все микрокоманды, сформированные в этом случае, нахоятся в пределах одной страницы блока памяти. При необходимости перехоа вновь к реализации линейного участка микропрограммы в формате первой микрокоманды из линейной последовательности задается единичньш сигнал на выходе Ь, который обесечивает по второму тактовому имульсу возвращение триггера 5 в сходное нулевое состояние и обнуение регистра 3 путем подачи на

его R-вход сигнала, сформированногл на вькоде элемента И 16. После чего устройство функционирует согласно алгоритма, описанного выше, В пред лагаемом устройстве предусмотрен контроль его функционирования. Сигнал Ошибка формируется на выходе 22 устройства в случае одновременного появления в формате микрокоманды управляющей метки и информации в поле логических условий.

По окончании работы устройства в последней микрокоманде записывается единица в разряде, соответствующем выходу 21 а регистра 4 микрокоманд. Этот сигнал поступает на R-вход триггера 10, который возвратится в исходное состояние и остановит д енераторП тактовых импульсов.

| Микропрограммное устройство управления | 1980 |

|

SU928356A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Хассон С | |||

| Микропрограммное управление | |||

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Майоров С.А., Новиков Г.И | |||

| Структура ЭВМ.-Л.: Машиностроение, 1979, с | |||

| Способ обработки шкур | 1921 |

|

SU312A1 |

Авторы

Даты

1985-10-07—Публикация

1984-04-25—Подача