1 1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройства контроля и управления технологическими процессами.

Целью изобретения является расширение области применения и повышение быстродействия устройства путем параллельного выполнения основных микропрограмм и контроля непрерывно контролируемых параметров технологических процессов.

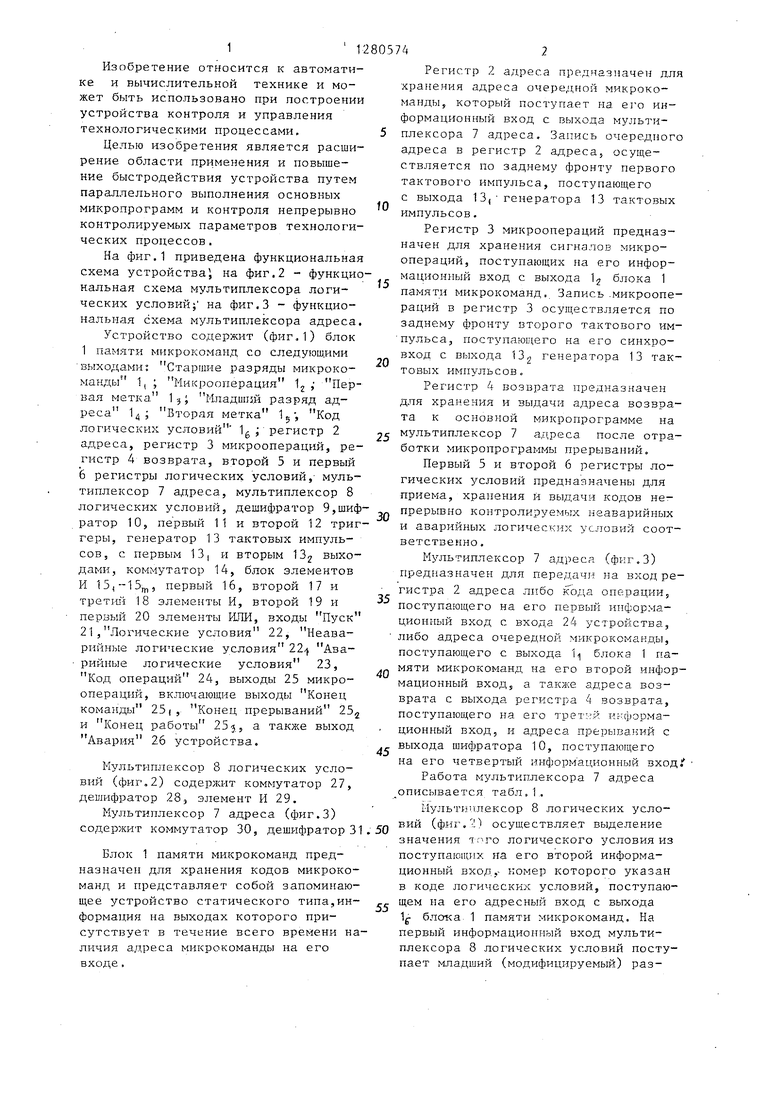

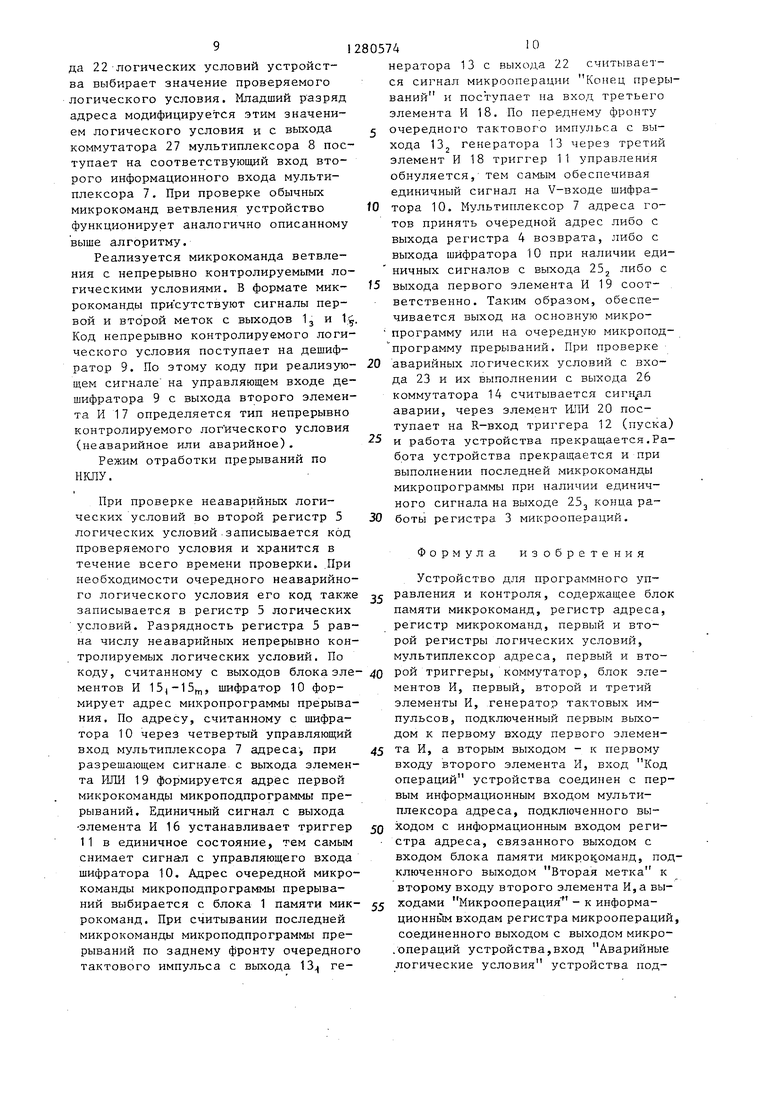

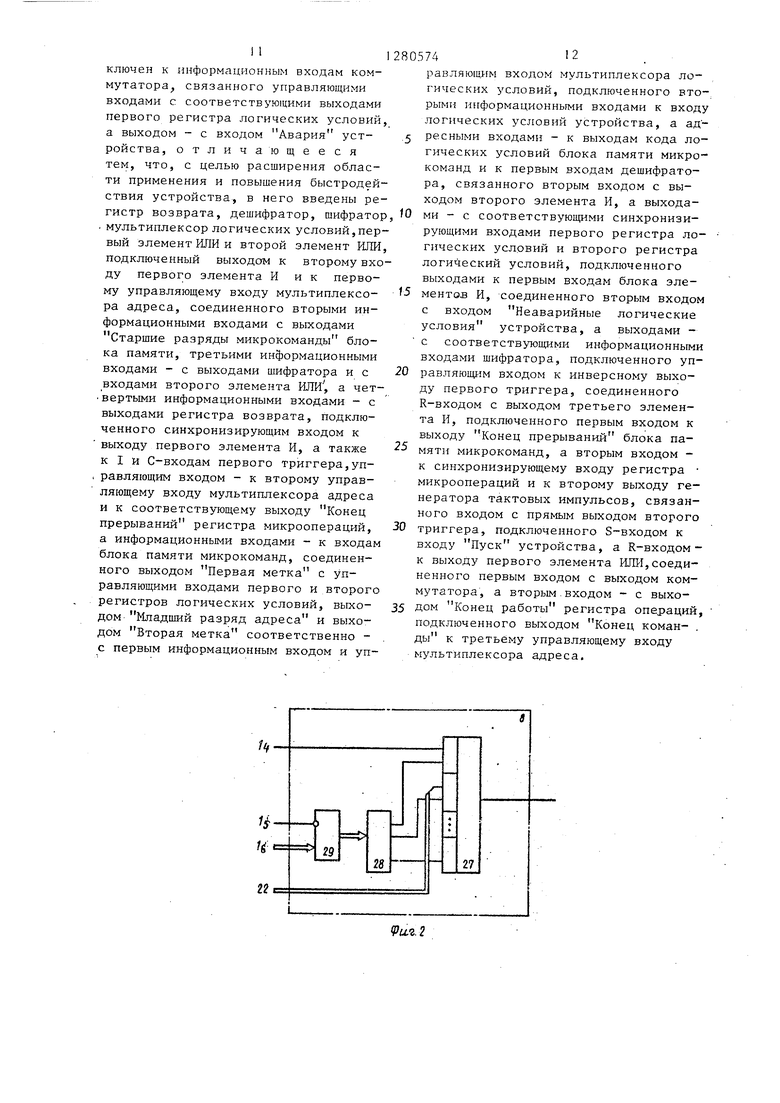

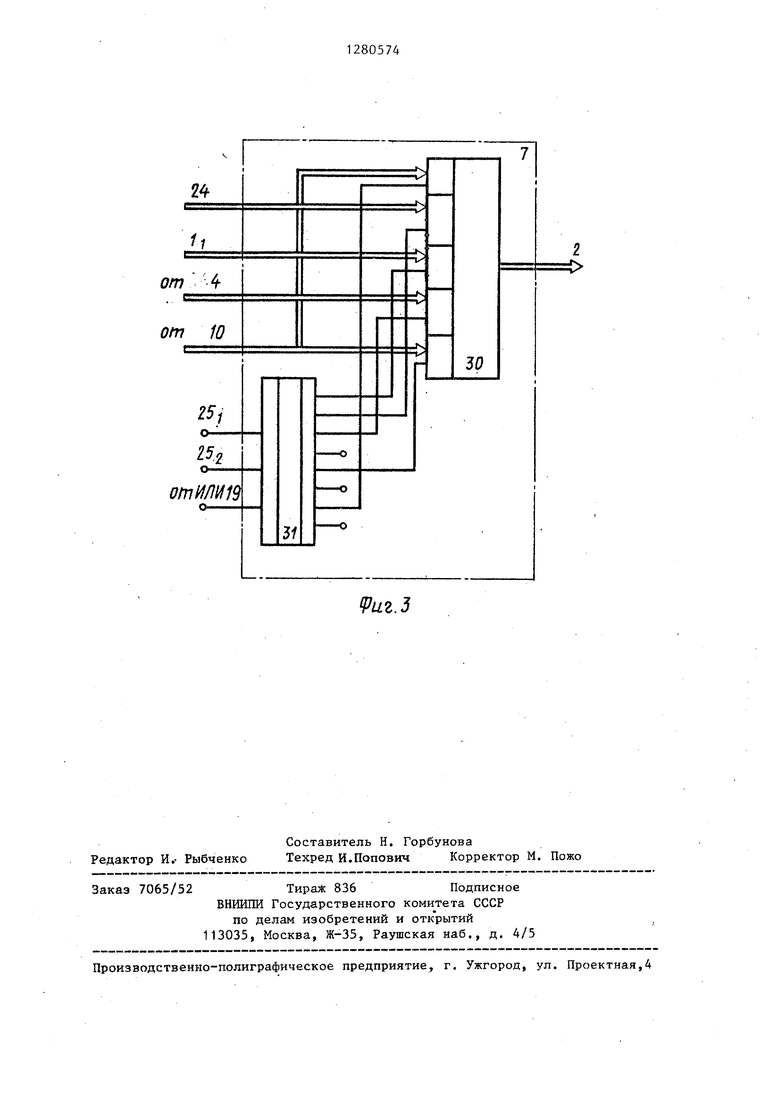

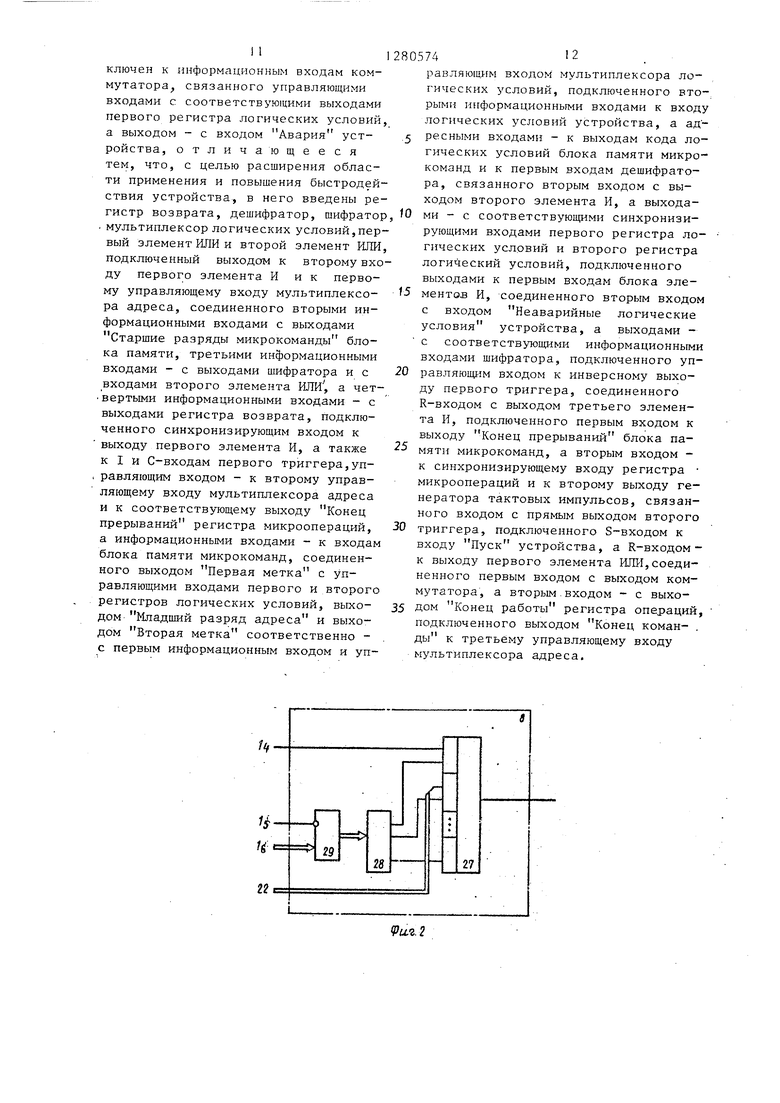

На фиг.1 приведена функциональная схема устройства , на фиг. 2 - функциональная схема мультиплексора логических условийj на фиг.З - функциональная схема мультиплексора адреса.

Устройство содержит (фигЛ) блок 1 памяти микрокоманд со следуюш.ими выходами: Старшие разряды микрокоманды 1, ; Микрооперация 1 , Первая метка 15; Младший разряд

14; Вторая метка 1, логических условий 1 ;

5 регистр 2

адреса, регистр 3 микроопераций, регистр 4 возврата, второй 5 и первый 6 регистры логических условий,- мультиплексор 7 адреса, мультиплексор 8 логических условий, дешифратор 9,шифратор 10, первый 11 и второй 12 триггеры, генератор 13 тактовых импульсов, с первым 13| и вторым 132 выходами, коммутатор 14, блок элементов И 15,--15 5 первый 16, второй 17 и третш 18 элементы И, второй 19 и первый 20 элементы ИЛИ, входы Пуск 21,Логические условия 22, Неаварийные логические условия 22- Ава- рийные логические условия 23, Код операций 24, выходы 25 микроопераций, включающие выходы Конец команды 251, Конец прерываний 252 и Конец работы 253, а. также выход Авария 26 устройства.

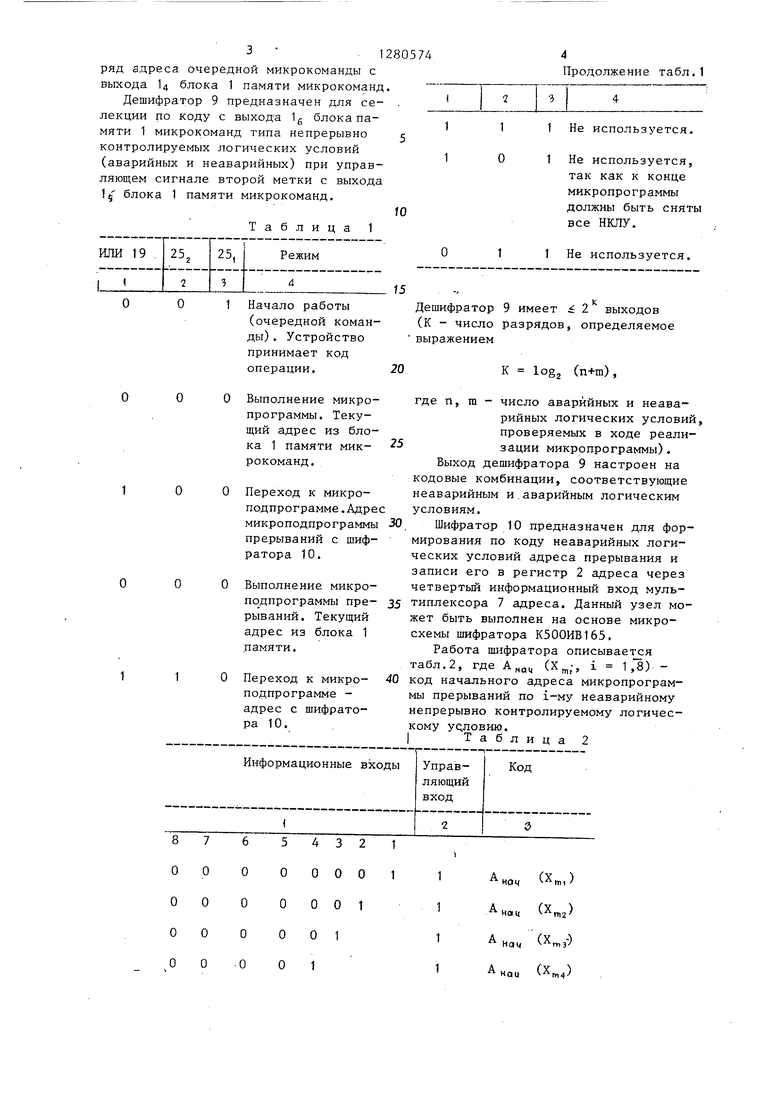

Мультиш шксор 8 логических условий (фиг.2) содерясит коммутатор 27, дешифратор 28, элемент И 29.

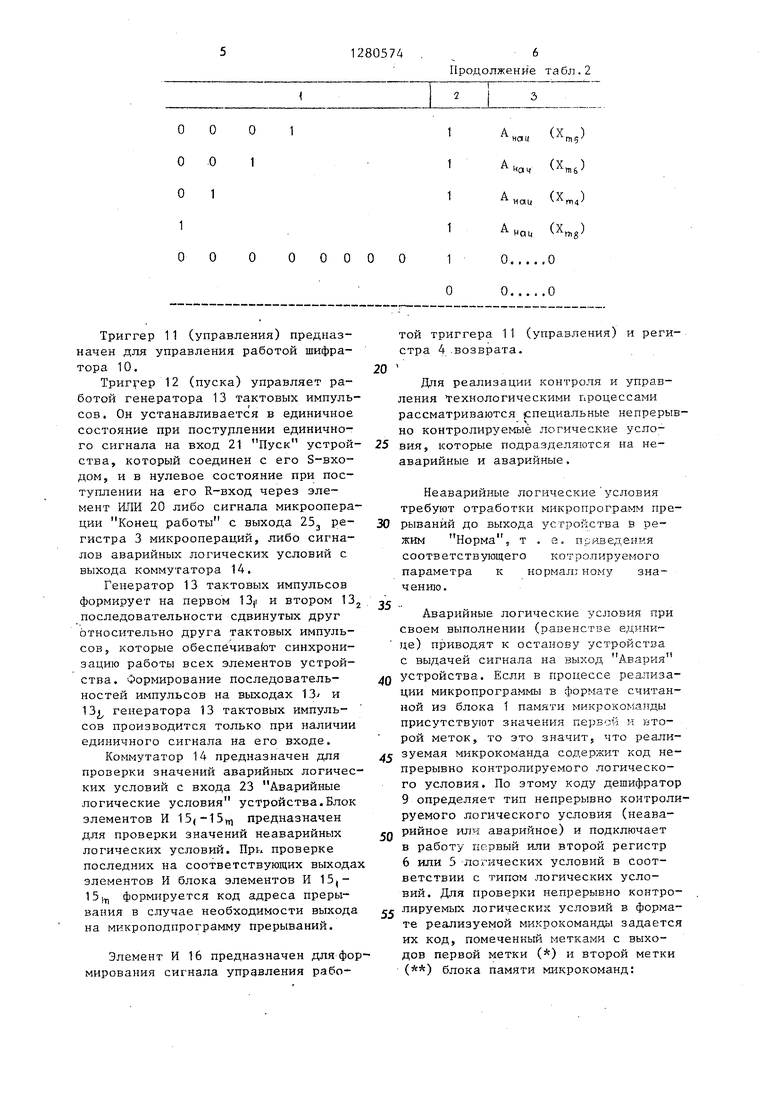

Мультиплексор 7 адреса (фиг.З) содержит коммутатор 30, дешифратор 3

Блок 1 памяти микрокоманд предназначен для хранения кодов микрокоманд и представляет собой запоминающее устройство статического типа,информация на выходах которого присутствует в течение всего времени наличия адреса микрокоманды на его входе,

0

5

0

Регистр 2 адреса предназначен для хранения адреса очередной микрокоманды, который поступает па его информационный вход с выхода мультиплексора 7 адреса. Запись очередного адреса в регистр 2 адреса, осуществляется по заднему фронту первого тактового импульса, поступающего с выхода 13, генератора 13 тактовых импульсов.

Регистр 3 микроопераций предназначен для хранения сигналов микроопераций, поступающих на его информационный вход с выхода 1 блока 1 памяти микрокоманд. Запись .микроопераций в регистр 3 осуществляется по заднему фронту второго тактового импульса, поступающего на его синхро- вход с выхода 13 генератора 13 тактовых импульсов о

Регистр 4 возврата предназначен для хранения и выдачи адреса возврата к основной микропрограмме на мультиплексор 7 адреса после отработки микропрограммы прерываний.

Первый 5 и второй 6 регистры логических условий предназна гены для приема, хранения и выдачи кодов непрерывно контролируемых неаварийных и аварийных логических условий соответственно.

Мультиплексор 7 адреса (фиг.З) предназначен для передачи на вход регистра 2 адреса либо к ода операции, поступающего на его первый информационный вход с входа 24 устройства, либо адреса очередной микрокоманды, поступающего с выхода блока 1 памяти микрокоманд на его второй информационный вход, а также адреса возврата с выхода регистра 4 возврата, поступающего на его третей информационный вход, и адреса прерываний с выхода шифратора 10, поступающего на его четвертый информационный вход.

Работа мультиплексора 7 адреса описывается табл,1.

Мультиплексор В логических условий (фиг. :) осуществляет выделение значения логического условия из поступающих на его второй информационный вход,- номер которого указан в коде логических условий, поступающем на его адресный вход с выхода

30

35

40

45

50

55

g бл(ука 1 памяти микрокоманд. На первый информационный вход мультиплексора 8 логических условий поступает младший (модифицируемый) раз3 12805

ряд адреса очередной микрокоманды с выхода 14 блока 1 памяти микрокоманд.

Дешифратор 9 предназначен для се- . лекции по коду с выхода 1g блока памяти 1 микрокоманд типа непрерывно .5 контролируемых логических условий (аварийных и неаварийных) при управляющем сигнале второй метки с выхода блока 1 памяти микрокоманд,

fO

Начало работы (очередной команды) . Устройство принимает код операции.

Продолжение табл.1

так как к конце микропрограммы должны быть сняты все НКЛУ.

Не используется.

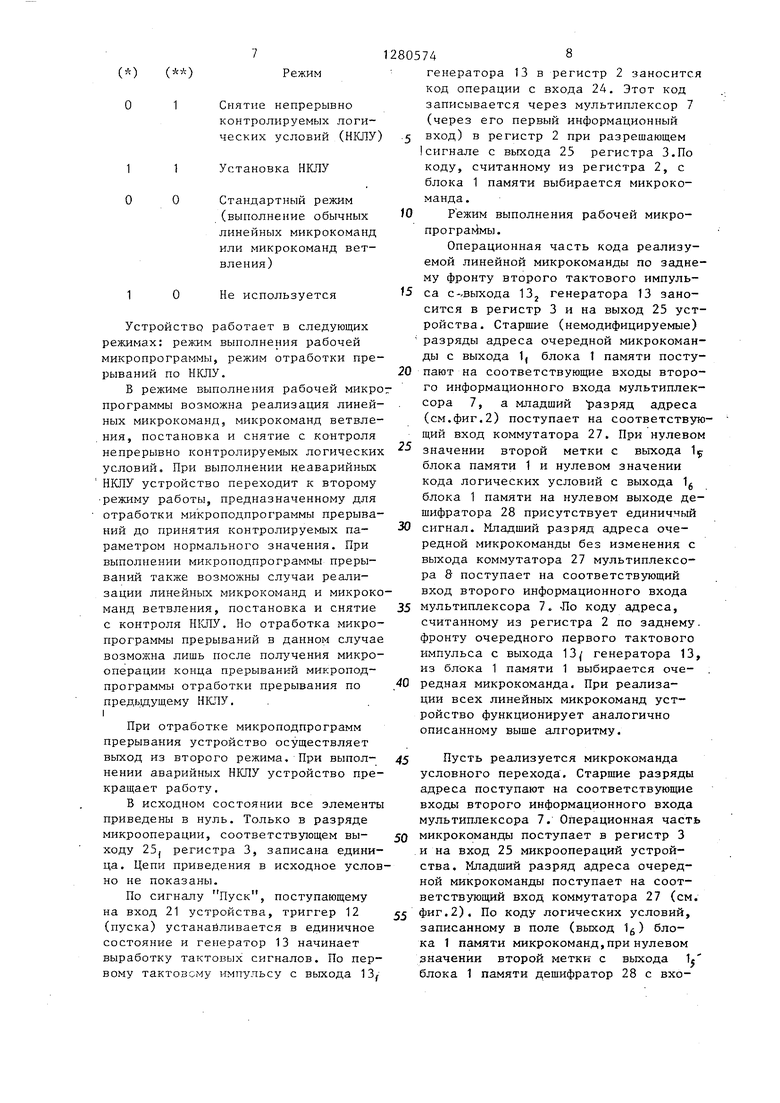

Дешифратор 9 имеет 2 выходов (К - число разрядов, определяемое выражением

К log (n+m),

Триггер 11 (управления) предназначен для управления работой шифратора 10.

Триггер 12 (пуска) управляет работой генератора 13 тактовых импульсов . Он устанавливается в единичное состояние при постурлении единичного сигнала на вход 21 Пуск устройства, который соединен с его S-вхо- дом, и в нулевое состояние при поступлении на его R-вход через элемент ИЛИ 20 либо сигнала микрооперации Конец работы с выхода 25,, регистра 3 микроопераций, либо сигналов аварийных лох ических условий с выхода коммутатора 14.

Генератор 13 тактовых импульсов формирует на первом 13|) и втором 13 последовательности сдвинутых друг относительно друга тактовых импульсов, которые обеспечивает синхронизацию работы всех элементов устройства. Формирование последовательностей импульсов на выходах 13 и 13 генератора 13 тактовых импульсов производится только при наличии единичного сигнала на его входе.

Коммутатор 14 предназначен для проверки значений аварийных логических условий с входа 23 Аварийные логические условия устройства.Блок элементов И 15(-15„1 предназначен для проверки значений неаварийных логических условий. Прк проверке последних на соответствующих выхода элементов И блока элементов И 15,- 1 5 , формируется код адреса прерывания в случае необходимости выхода на микроподпрограмму прерываний.

Элемент И 16 предназначен для фор мирования сигнала управления рабоПродолжение табл.2

той триггера 11 (управления) и регистра 4 .возврата,

Для реализации контроля и управления технологическими процессами рассматриваются специальные непрерывно контролируемые логические условия, которые подразделяются на неаварийные и аварийные,

Неаварийные логические условия требуют отработки микропрограмм прерываний до выхода устройства fi режим Норма, т.е. приведения соответствующего котролируемого параметра к нормалтному значению.

Аварийные логические условия при своем выполнении (равенстве единице) приводят к останову устройства с выдачей сигнала на выход Авария устройства. Е1СЛИ в процессе реализации микропрограммы в формате считанной из блока 1 памяти микрокомапкы присутствуют значения первой к второй меток, то это значит, что реализуемая микрокоманда содержит код непрерывно контролируемого логического условия. По этому коду дешифратор 9 определяет тип непрерывно контролируемого логического условия (неаварийное или аварийное) и подключает в работу первый или второй регистр 6 или 5 -логических условий в соответствии с типом логических условий. Для проверки непрерывно контролируемых логических условий в формате реализуемой микрокоманды задается их код, помеченньй метками с выходов первой метки () и второй метки () блока памяти микрокоманд:

Л) ()Режим

01 Снятие непрерывно

контролируемых логических условий (НКЛУ)

11 Установка НКЛУ

О О Стандартный режим

(выполнение обычных линейных микрокоманд или микрокоманд ветвления)

1

О Не используется

Устройство работает в следующих режимах: режим выполнения рабочей микропрограммы, режим отработки прерываний по НКЛУ.

В режиме выполнения рабочей микро программы возможна реализация линейных микрокоманд, микрокоманд ветвления, постановка и снятие с контроля непрерывно контролируемых логических условий. При выполнении неаварийных НКЛУ устройство переходит к второму режиму работы, предназначенному для отработки микроподпрограммы прерываний до принятия контролируемых параметром нормального значения. При выполнении микроподпрограммы прерываний также возможны случаи реализации линейных микрокоманд и микрокоманд ветвления, постановка и снятие с контроля HICny. Но отработка микропрограммы прерываний в данном случае возможна лишь после получения микрооперации конца прерываний микропод- программы отработки прерывания по

предыдущему НКЛУ. I

При отработке микроподпрограмм прерывания устройство осуществляет выход из второго режима. При выполнении аварийных НКЛУ устройство прекращает работу.

В исходном состоянии все элементы приведены в нуль. Только в разряде микрооперации, соответствующем выходу 25( регистра 3, записана единица. Цепи приведения в исходное условно не показаны.

По сигналу Пуск, поступающему на вход 21 устройства, триггер 12 (пуска) устанайливается в единичное состояние и генератор 13 начинает выработку тактовых сигналов. По первому тактовому импульсу с выхода 13f

2805748

генератора 13 в регистр 2 заносится код операции с входа 24. Этот код записывается через мультиплексор 7 (через его первый информационный

5 вход) в регистр 2 при разрешающем I сигнале с выхода 25 регистра З.По коду, считанному из регистра 2, с блока 1 памяти выбирается микрокоманда,

JO Режим выполнения рабочей микро- програймы.

Операционная часть кода реализуемой линейной микрокоманды по заднему фронту второго тактового импуль 5 са с--выхода 13 генератора 13 заносится в регистр 3 и на выход 25 устройства. Старшие (немодифицируемые) разряды адреса очередной микрокоманды с выхода 1, блока 1 памяти поступают на соответствующие входы второго информационного входа мультиплексора 7, а младший разряд адреса (см,фиг.2) поступает на соответствующий вход коммутатора 27, При нулевом значении второй метки с выхода 1 блока памяти 1 и нулевом значении кода логических условий с выхода 1 блока 1 памяти на нулевом выходе дешифратора 28 присутствует единичный

30 сигнал. Младший разряд адреса очередной микрокоманды без изменения с выхода коммутатора 27 мультиплексора 8 поступает на соответствующий вход второго информационного входа 35 мультиплексора 7. -По коду адреса, считанному из регистра 2 по заднему, фронту очередного первого тактового импульса с выхода 13 генератора 13, из блока 1 памяти 1 выбирается оче- 40 редная микрокоманда. При реализации всех линейных микрокоманд устройство функционирует аналогично описанному выше алгоритму.

20

25

Пусть реализуется микрокоманда условного перехода. Старшие разряды адреса поступают на соответствующие входы второго информационного входа мультиплексора 7, Операционная часть микрокоманды поступает в регистр 3 и на вход 25 микроопераций устройства. Младший разряд адреса очередной микрокоманды поступает на соответствующий вход коммутатора 27 (см.

фиг,2). По коду логических условий, записанному в поле (выход 1) блока 1 памяти микрокоманд,при нулевом значении второй метки с выхода блока 1 памяти дешифратор 28 с входа 22 логических условий устройства выбирает значение проверяемого логического условия. Младший разряд адреса модифицируется этим значением логического условия и с выхода коммутатора 27 мультиплексора 8 поступает на соответствующий вход второго информационного входа мультиплексора 7. При проверке обычных микрокоманд ветвления устройство функционирует аналогично описанному выше алгоритму.

Реализуется микрокоманда ветвления с непрерывно контролируемыми логическими условиями. В формате мик- рокоманды присутствуют сигналы первой и вто рой меток с выходов 1з и 1 Код непрерывно контролируемого логического условия поступает на дешифратор 9. По этому коду при реализующем сигнале на управляющем входе дешифратора 9 с выхода второго элемента И 1 7 определяется тип непрерывно контролируемого лог ического условия (неаварийное или аварийное).

Режим отработки прерываний по ИКПУ.

При проверке неаварийных логических условий во второй регистр 5 логических условий .записывается код проверяемого условия и хранится в течение всего времени проверки. Дри необходимости очередного неаварийного логического условия его код также записывается в регистр 5 логических условий. Разрядность регистра 5 равна числу неаварийных непрерывно контролируемых логических условий. По

коду, считанному с выходов блока эле- 0 Рой триггеры, коммутатор, блок элементов И 15,-15f, шифратор 10 формирует адрес микропрограммы прерывания. По адресу, считанному с шифратора 10 через четвертый управляющий вход мультиплексора 7 адреса-, при разрешающем сигнале с выхода элемента 1-иШ 19 формируется адрес первой микрокоманды микроподпрограммы прерываний. Единичный сигнал с выхода элемента И 16 устанавливает триггер 11 в единичное состояние, тем самым снимает сигнагл с управляющего входа шифратора 10. Адрес очередной микрокоманды микроподпрограммы прерываний выбирается с блока 1 памяти микрокоманд. При считывании последней микрокоманды микроподпрограммы пре- рыв-аний по заднему фронту очередного тактового импульса с выхода 13j ге

нератора 13 с выхода 22 считывается сигнал микрооперации Конец прерываний и поступает на вход третьего элемента И 18. По переднему фронту очередного тактового импульса с выхода ISj генератора 13 через третий элемент И 18 триггер 11 управления обнуляется, тем самым обеспечивая единичный сигнал на V-входе шифратора 10. Мультиплексор 7 адреса готов принять очередной адрес либо с выхода регистра 4 возврата, либо с выхода шифратора 10 при наличии единичных сигналов с выхода 25 либо с выхода первого элемента И 19 соответственно. Таким образом, обеспечивается выход на основную микропрограмму или на очередную микропод- программу прерываний. При проверке аварийных логических условий с входа 23 и их выполнении с выхода 26 коммутатора 14 считывается сигн/1л аварии, через элемент ИЛИ 20 поступает на R-вход триггера 12 (пуска) и работа устройства прекращается.Работа устройства прекращается и при выполнении последней микрокоманды микропрограммы при наличии единичного сигнала на выходе боты регистра 3 микроопераций,

25з конца раФормула изобретения

Устройство для программного управления и контроля, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, первый и второй регистры логических условий, мультиплексор адреса, первый и вто5

0

5

ментов И, первый, второй и третий элементы И, генератор тактовых импульсов, подключенный первым выходом к первому входу первого элемента И, а вторым выходом - к первому входу второго элемента И, вход Код операций устройства соединен с первым информационным входом мультиплексора адреса, подключенного выходом с информационным входом регистра адреса, связанного выходом с входом блока памяти микро1соманд, подключенного выходом Вторая метка к второму входу второго элемента И, а выходами Микрооперация - к информационным входам регистра микроопераций, со.единенного выходом с выходом микро- .операций устройства,вход Аварийные логические условия устройства подключей к информационным входам ком- мутатора, связанного управляющими входами с соответствующими выходами первого регистра логических условий, а выходом - с входом Авария устройства, отличающееся тем, что, с целью расширения области применения и повышения быстродействия устройства, в него введены регистр возврата, дешифратор, шифратор

мультиплексор логических условий,первый элемент ИЛИ и второй элемент ИЛИ, подключенный выходам к второму входу первого элемента И и к первому управляющему входу мультиплексора адреса, соединенного вторыми информационными входами с выходами Старшие разряды микрокоманды блока памяти, третьими информационными входами - с выходами шифратора и с входами второго элемента ИЛИ , а четвертыми информационными входами - с выходами регистра возврата, подключенного синхронизирующим входом к

выходу первого элемента И, а также к I и С-входам первого триггера,управляющим входом - к второму управляющему входу мультиплексора адреса и к соответствующему выходу Конец прерываний регистра микроопераций, а информационными входами - к входам блока памяти микрокоманд, соединенного выходом Первая метка с управляющими входами первого и второго регистров логических условий, выхоом Младший разряд адреса и выхоом Вторая метка соответственно - с первым информационным входом и упЧЧ

2

29

10

80574 2

равляющим входом мультиплексора логических условий, подключенного вторыми информационными входами к входу логических условий устройства, а ад - . ресными входами - к выходам кода логических условий блока памяти микрокоманд и к первым входам дешифратора, связанного вторым входом с выходом второго элемента И, а выходами - с соответствующими синхронизирующими входами первого регистра логических условий и второго регистра логи еский условий, подключенного выходами к первым входам блока эле- f5 ментов И, соединенного вторым входом с входом Неаварийные логические условия устройства, а выходами - с соответствующими информационными входами шифратора, подключенного управляющим входом к инверсному выходу первого триггера, соединенного R-входом с выходом третьего элемента И, подключенного первым входом к выходу Конец прерываний блока памяти микрокоманд, а вторым входом - к синхронизирующему входу регистра микроопераций и к второму выходу генератора тактовых импульсов, связанного входом с прямым выходом второго триггера, подключенного 8 входом к входу Пуск устройства, а R-входом- к выходу первого элемента ИЛИ,соединенного первым входом с выходом коммутатора, а вторым,входом - с выхо- 5 дом Конец работы регистра операций, подключенного выходом Конец коман- . ды к третьему управляющему входу мультиплексора адреса.

0

5

0

28

27

от 4от 10

о-

omHfl ig

о-Редактор И,- Рыбченко

Составитель Н. Горбунова

Техред И.Попович Корректор М. Пожо

Заказ 7065/52Тира 836Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

2 :(

.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1278846A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении устройств контроля и управления технологическими процессами. Цель изобретения - расширение области применения и повышение быстродействия устройства.Устройство содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микро- ёпераций, регистр 4 возврата, второй 5 и первый 6 регистры логических условий, мультиплексор 7 адреса, мультиплексор 8 логических условий, дешифратор 9, шифратор 10, первый 11 и второй 12 триггеры, генератор 13 тактовых импульсов, коммутатор 14, блок элементов И 15 -15 , первый 16, второй 17 и третий 18 элементы И, второй 19 и первый 20 элементы ШШ. 3 ил. 2 табл. с SS ел й/л/

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955057A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-08-16—Подача