2. Устройство по п. 1, отличающееся тем, что блок управления содержит первый и второй счетчики импульсов, два триггера,последовательно соединенные генератор импульсов первый элемент И,первый элемент ИЛИ, первьй элемент задержки, второй элемент И и второй элемент ИЛИ, а также последовательно соединенные третий элемент ИЛИ, первый триггер, третий элемент И, четвертый элемент ИЛИ, второй элемент эадержки и четвертый элемент И, выход которого соединен с третьим выходом блока управления и через первый счетчик импульсов - с вторым входом второго элемента ИЛИ, выход которого подключен к выходу блока управления и через второй „ счетчик импульсов - к первому входу второго триггера и к первому вход третьего элемента ИЛИ, вторым входом

подключенного к соответствующему первому входу блока управления, выход второго триггера подключен к второму входу первого элемента И, а второй вход - к входу блока управления, первый выход третьего триггера соединен с вторым входом второго элемента И, а второй выход - с вторым входом четвертого элемента И, а вход - с соответствующим первым входом блока управления, третий вход второго элемента ИЛИ соединен с соответствующим первым входом блока управления, вторые входы первого и четвертого элементов ИЛИ подключены к соответствующим первым выходам блока управления, а также к выходам третьего и первого элементов И соответственно, второй выход первого триггера подключен к второму выходу блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство оперативного контроля в системах автоматизированного управления | 1985 |

|

SU1422233A1 |

| Устройство для оперативного контроля в системах автоматизированного управления | 1984 |

|

SU1236505A1 |

| Устройство адресации для канала прямого доступа к памяти | 1985 |

|

SU1283763A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Устройство для считывания информации | 1989 |

|

SU1693617A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

1. УСТРОЙСТВО ДЛЯ ОПЕРАТИВНОГО КОНТРОЛЯ В CHCTEbiAX АВТОМАТИЗМ- РОВАННОГО УПРАВЛЕНИЯ, содержащее регистр, блок ввода информации, первые выходы которого соединены с первыми входами блока управления,-подключенного первыми выходами к блоку памяти, вторым вьпсодом - к первому входу блока индикации, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, в него введены два элемента ИЛИ, элемент ЗАПРЕТ, сумматор и счетчик.адреса, первые входы которого соединены с третьими выходами блока управления, второй вход - с вторым выходом блока ввода информации, а выход - с вторьм входом блока памяти и через первый элемент ИЛИ - с вторым входом блока индикации,- третий выход блока ввода информации подключен к третьему входу блока памяти и через второй элемент ИЛИ - к входу регистра, выход которого соединен с первым входом сумма(Л тора, подключенного вторым входом к выходу блока памяти, первым выходом к второму входу блока управления, а вторым выходом - к второму входу первого элемента ИПИ и через элемент ЗАПРЕТ - к второму входу второго элемента ИЛИ. 00 О9 СО 00 о

I

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства крнтрол технологических или производственных процессов, состояния оборудования, оперативного контроля в системе управления, в сфере управления транспортными перевозками, для управления ходом -работ по сетевым графикам, а также для отображения преобразования информации задач оптимального планирования.

Цель изобретения - упрощение устройства и повышение его быстродействия.

На фиг. 1 представлена функциональная схема устройства; на фиг.2 схема блока yпpaвлeния, на фиг. 3 блок ввода информации. Устройство содержит блок 1 ввода информации, счетчик 2 адреса, блок 3 управления, элементы ИЛИ 4 и 5, блок 6 памяти, регистр 7, сумматор 8, блок 9 индикации, элемент 10 запрета.

Блок управления (фиг. 2) содержит счетчики 11 и 12 импульсов, элементы ИЛИ 13-16, элементы И 17-20, триггеры 21-23, элементы задержки 24 и

25, генератор 26 импульсов, а также входы 27-31 и выходы 32-36.

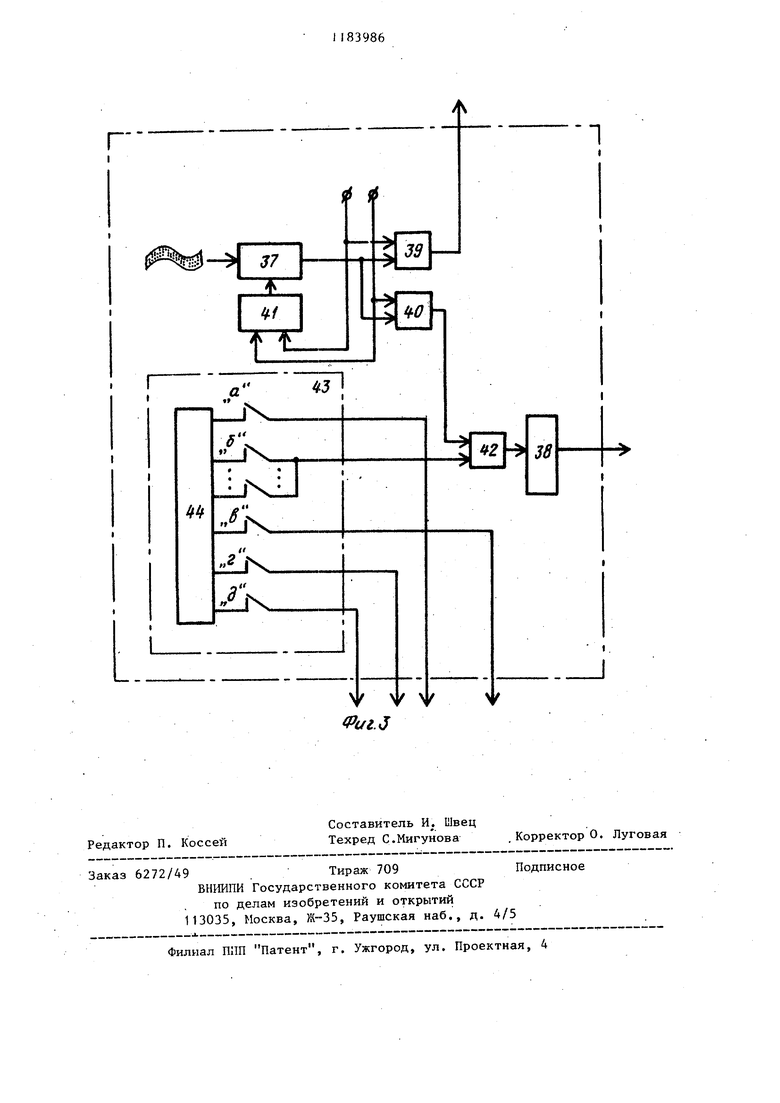

Блок ввода информации 1 (фиг. 3) . содержит фотосчитывающий блок 37, регистр 38 для кратковременного хранения адреса, элементы И 39, И 40, ИЛИ 41, ИЛИ 42, пульт 43 управления, формирователь 44 сигнала.

Назначение кнопок следующее: ч кнопка выбора режима прямой или транспонированной матрицы; 5 - набор кно- пок установки начального адреса, в кнопка записи начального адреса; г кнопка включения режима Запись в ЗУ 9 - кнопка включения режима Чтение .ЗУ.

Чтение информации из фотосчитывающего блока 37 синхронизируется сигналами тактового генератора. Элементы И 39, И 40 обеспечивают передачу считываемой информации в направлении одного из выходов, в зависимости от заданного режима.

Все указанные блоки и элементы реализованы на основе типовых. Например, в качестве запоминающего устройства, счетчиков, регистра, сумматора, триггеров, элементов И, ИЛИ могут 3 использоваться интегральные микросхе мы К565РУ2, К155ИЕ7, К155ИЕ5,К155ИР1 К155ИМЗ, К155ТМ2, К155ЛАЗ, К155ЛЕ1 и др. В устройстве может быть исполь зован блок индикации ИМГ-1-03. Блок ввода содержит пульт для ручного вво да информации, а также фотосчитывающее устройство FS-1501. Устройство работает следующим образом. В режиме записи показателей С-на адресные входы блока 6 памяти поступают адреса ячеек, формируемые счетчиком 2 адреса. Адресная информация поступает на вход счетчика 2 адреса из блока 1 ввода и записывается в счетчик адреса по сигналу, поступающему с выхода 32 блока управ ления. Этот сигнал формируется в блоке ввода, поступает на вход счетчика адреса через элемент ИЛИ 13 бло ка управления. Информация С- поступа ет из блока ввода на информационный вход блока 6 памяти в такт с сигналом записи, возникающим на выходе 34 блока управления. Если показатели должны быть представлены в виде прямой матрицы, то сначала в счетчик адреса записывается адрес первой страницы блока, а затем поочередно формируются адреса всех ячеек этой страницы добавлением в счетчик адреса единицы. При работе с прямой матрицей триггер 21 блока управления находится в нулевом состоянии, поэтому элемент И 17 закрыт, а элемент И 18 открыт. Сигнал записи с выхода блока ввода поступает на вход 29 блока управления, устанавливает триггер 22 этого блока в единичное состояние и открывает элемент И 19. Тактовые импульсы поступают с выхода 34 блока управления на вход записи блока 6 и одновременно через элементы ИЛИ 15, задержки 25, И 18 поступают на вход прибавления единицы счетчика адреса и вход счетчика 12. Каждый тактовый импульс записывает показатель С;.- в выбранную ячейку блока 6 памяти и формирует адрес следующей ячейки, т.е. добавляет единицу в счетчик адреса. Заполнение счетчика 12 происходит одновременно с перебором всех ячеек указанной страницы. При заполнении счетчика 12 сигнал с его выхода через элемент ИЛИ 13 записывает в счетчик адреса следующей страницы и добавля864ет единицу в счетчик 11. После этого счетчик 12 обнуляется (цепь обнуления не показана). Информация записывается в ячейки следующей страницы аналогично. При заполнении всех страниц блока памяти 6 счетчик 11 также заполняется и подает сигнал, который переключает триггер 22 в нулевое состояние. Запись информации окончена. При занесении информации с одновременным транспортированием матрицы показателей вначале записывается адрес первой страницы блока .памяти в счетчик адреса.Информация записывается в ячейку блока памяти, соответствукидую этому .адресу. Затем номера страниц поочередно переключаются. Для записи информации с транспортированием матрицы триггер 21 переключается в единичное положение сигналом с выхода блока ввода. Элемент И 17 открьгоается, а И 18 закрывается. Сигналом с выхода блока ввода триггер 22 переключается в единичное положение и открывает элемент И 19. Тактовые импульсы поступают на вход записи блока 6 памяти и через элементы ИЛИ 14, задержки 24,И17, ИЛИ 13.поступают на вход записи счетчика адреса и вход счетчика 11. Каждый тактовый импульс записывает информацию в первую ячейку выбранной страницы блока 5 памяти и записывает адрес следующей страницы в счетчик адреса. Заполнение счетчика 11 происходит одновременно с перебором всех стра- ниц блока 6 памяти, поэтому после записи информации в ячейку последней страницы ЗУ на выходе этого счетчика появляется сигнал, который переключает триггер 22 в нулевое состояние. Заполненная таким образом матрица показателей будет транспонированной по отношению к исходной. В режиме поиска адреса по показателю С-; триггер 23 сигналом с выхода блока ввода переключается в еди- ничное состояние. Элемент И 20 открывается и тактовые импульсы поступают с выхода 35 блока управления на вход чтения блока памяти и одновременно поступают на вход прибавления единицы или вход записи адреса страницы в зависимости от положения триггера 21. Считываемая информация поступает на вход-первого слагаемого сумматора 8. На вход второго слагаемого этого сумматора поступает обратный код

сравниваемого показателя Cif предварительно эаписанного в регистр 7 из блока ввода через элемент ИЛИ 4. Суммматор в этом случае работает как схема сравнения, что обеспечивается подачей сигнала на управляющий вход элемента 10 запрета и на вход переноса нулевого разряда сумматора (не показано) . При совпадении считанного из блока памяти показателя с показателем записанным в регистре 7, на выходе переноса последнего разряда сумматора появляется единичный сигнал, который поступает на вход 31 блока управления и через элемент ИЛИ 16 переключает триггер 23 в нулевое состояние. Элекент И 20 закрывается, запрещая прохождение тактовых импульсов. Адрес ячейки ЗУ, из которой была считана ин формация в последнем такте, выводится в блок индикации. При этом элементы 24 и 25 обеспечивают задержку записи нового адреса в счетчик адреса до окончания процесса записи или чтения блока памяти и передачи информации в блок индика1щи.

Если необходимо просуммировать

показатели С., по строкам или столб11цам матрицы, т.е. по одноименньм ячеи

кам всех страниц или всем ячейкам одной страницы, то адресная информация формируется аналогично построению транспонированной или прямой матрицы соответственно с подачей импульсов чтения блока памяти синхронно с изменением адресов. Информация, считываемая из блока памяти, поступает на вход сумматора, которьй работает в этом случае как накапливающий. Это обеспечивается снятием сигнала с управляющего входа элемента 10

запрета и входа переноса нулевого разряда сумматора. В процессе сумми рования информация накапливается в регистре 7 (цепь записи в регистр также не показана).

После чтения всех адресов триггер 23 обнуляется сигналом из счетчика 11 и информация выводится из сумматора в блок индикации.

При решении задач сортировки данных, требующих осуществлять выборочную запись и чтение информации в блоке памяти, данное устройство позволяет получить выигрыш во времени по сравнению с известным. Это возможно благодаря адресному обращению к нужной странице ЗУ, организованному с помощью счетчика адреса В известном устройстве обращение ко всем строкам и столбцам Матрицы бЛока памяти осуществляется лишь последовательно с помощью регистров сдвига, что исключает возможность выборочного обращения к нужной строке или. столбцу.

Блок ввода выполняет стандартные функции и не требует подробного описания. В простейшем случае он содержит клавиатуры набора информации и набора адреса, кнопки записи адреса в счетчик адреса и записи информации в блок памяти, кнопки чтения блока памяти, установка режима записи показателей в виде прямой или трспортированной матрицы. В режимах поиска адреса и суммирования показателей выдача адресной информации из блока ввода в счетчик адреса тактируется, генератором тактовых импульсов (не показано).

иг.2

Г

.

44

Pt/i.J

| Авторское свидетельство СССР № 431517, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО ДЛЯ ОПЕРАТИВНОГО КОНТРОЛЯ В СИСТЕМАХ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 0 |

|

SU399870A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-07—Публикация

1984-04-06—Подача