1

Изобретение относится к цифровой вычислительной технике и может быть использовано в мини-ЭВМ и специальных системах обработки информации, в частности в локальных вычислительных сетях с высокой скоростью передачи информации,

Цель изобретения - повьппение производительности устройства и системы в целом путем обеспечения перезагрузки устройства в процессе ра- боты, а также автоматической инициализации устройства при включении питания или по сигналу сброса.

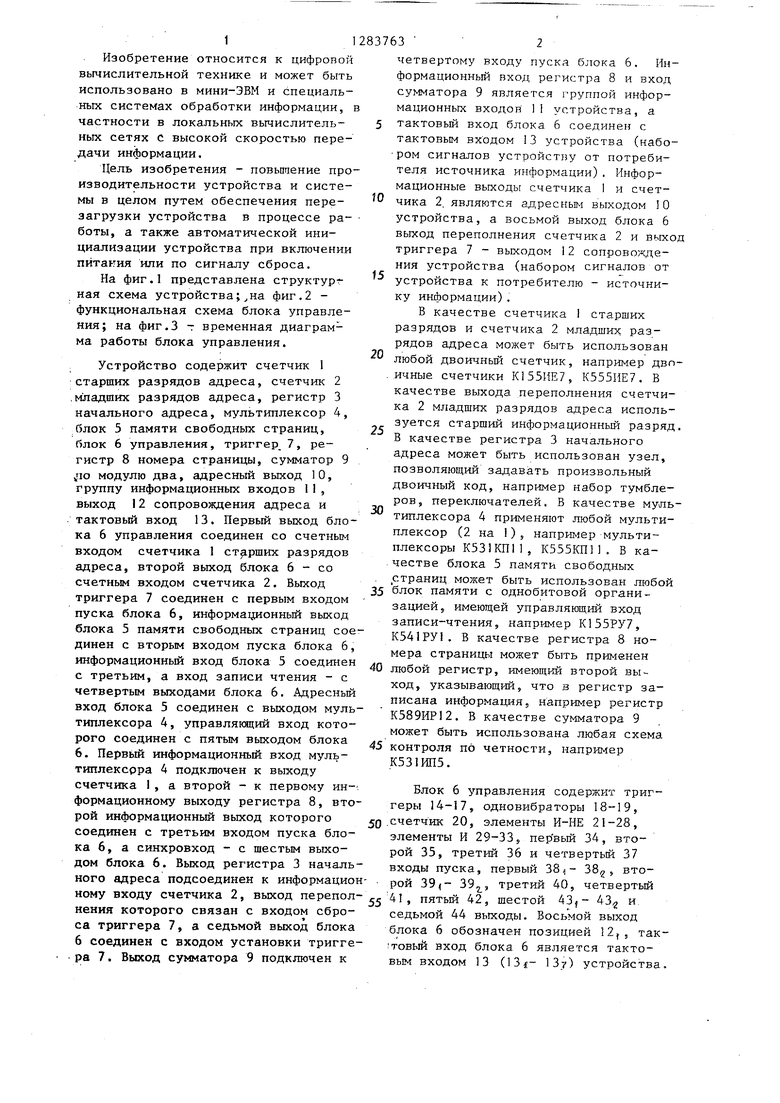

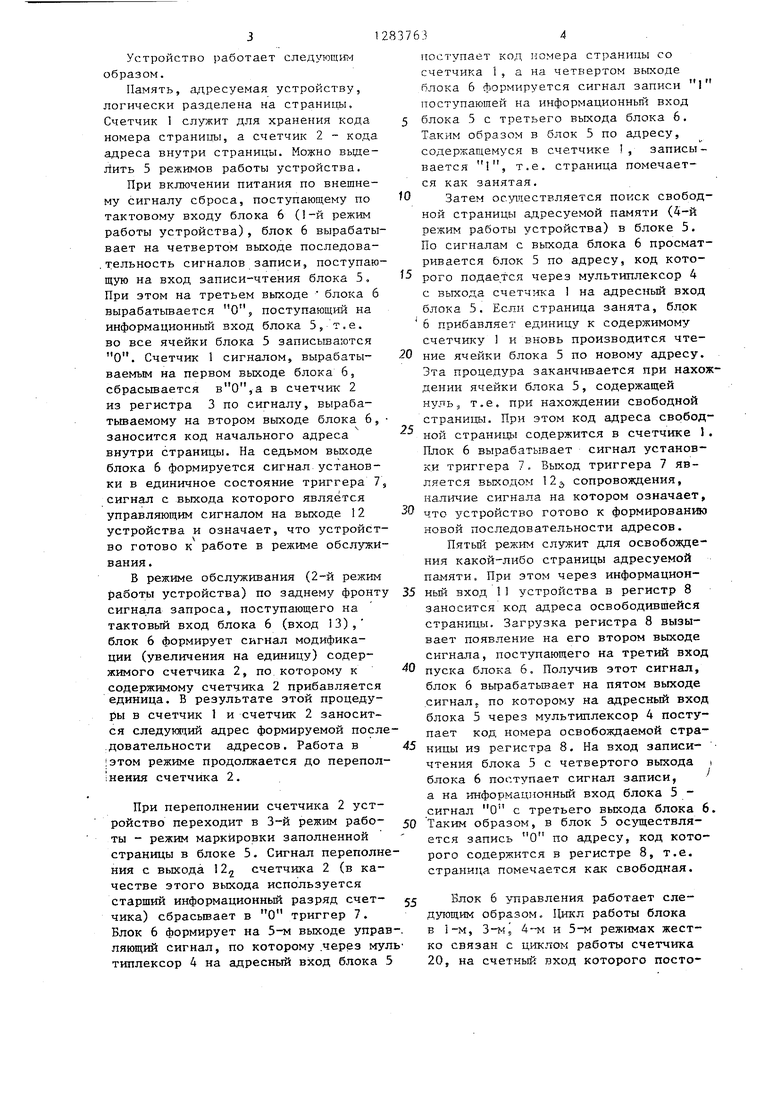

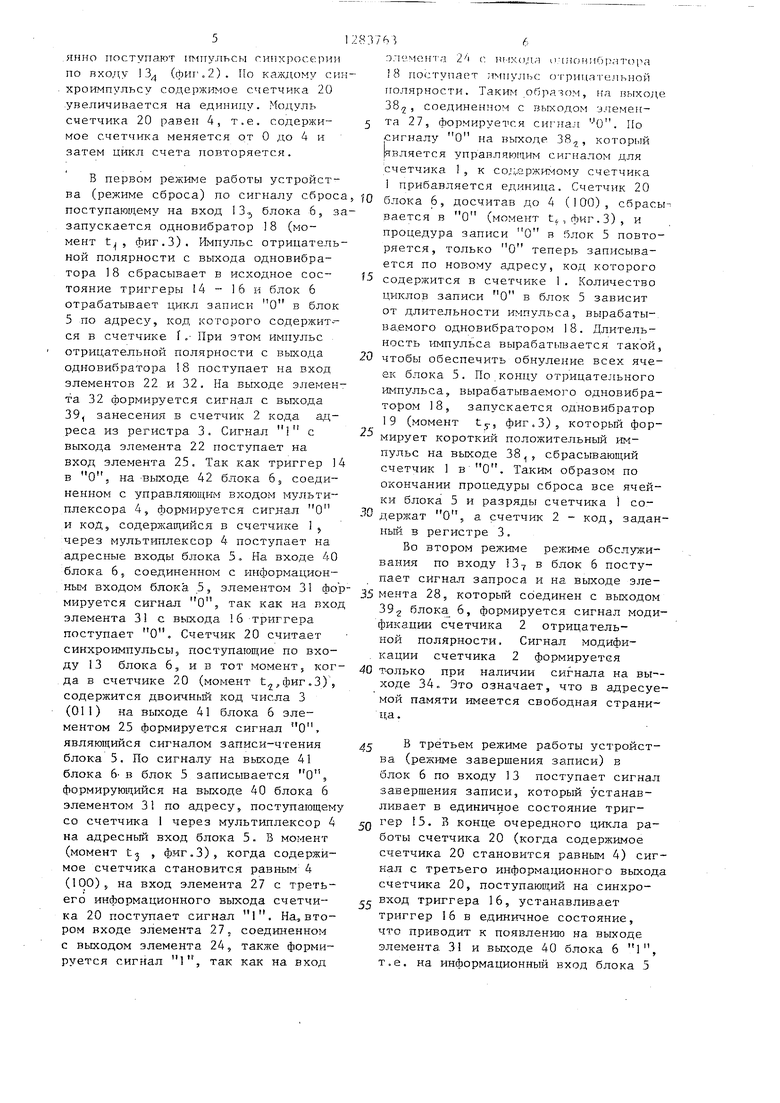

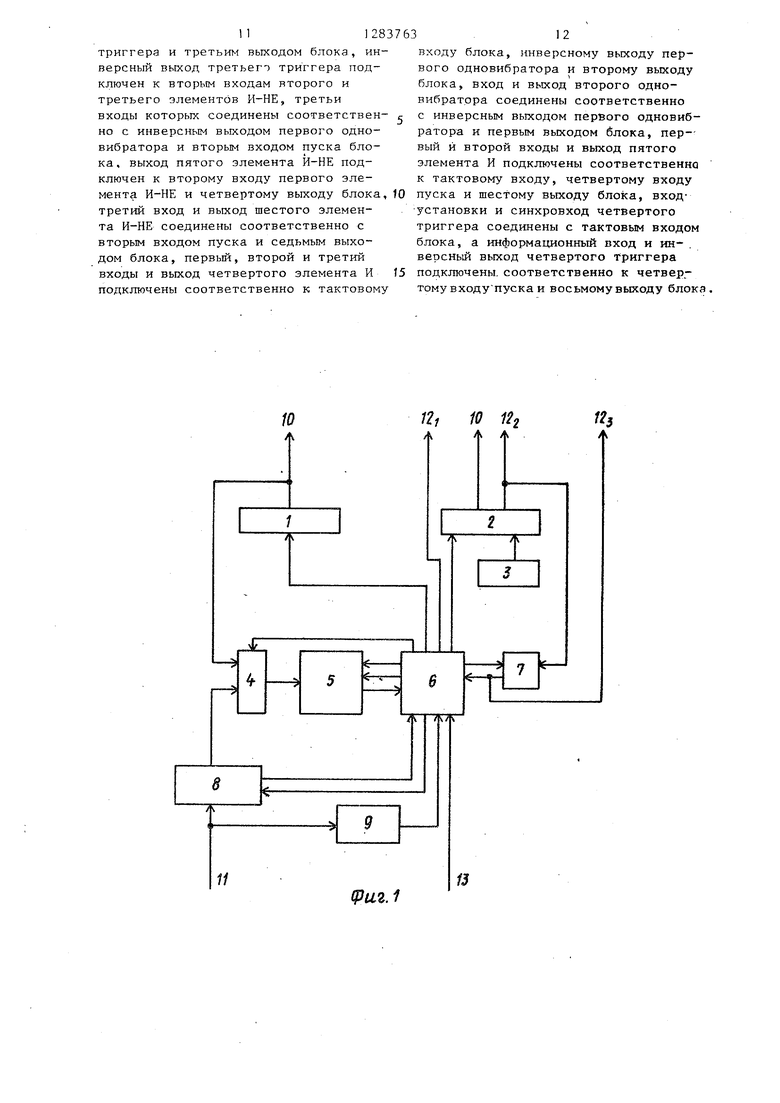

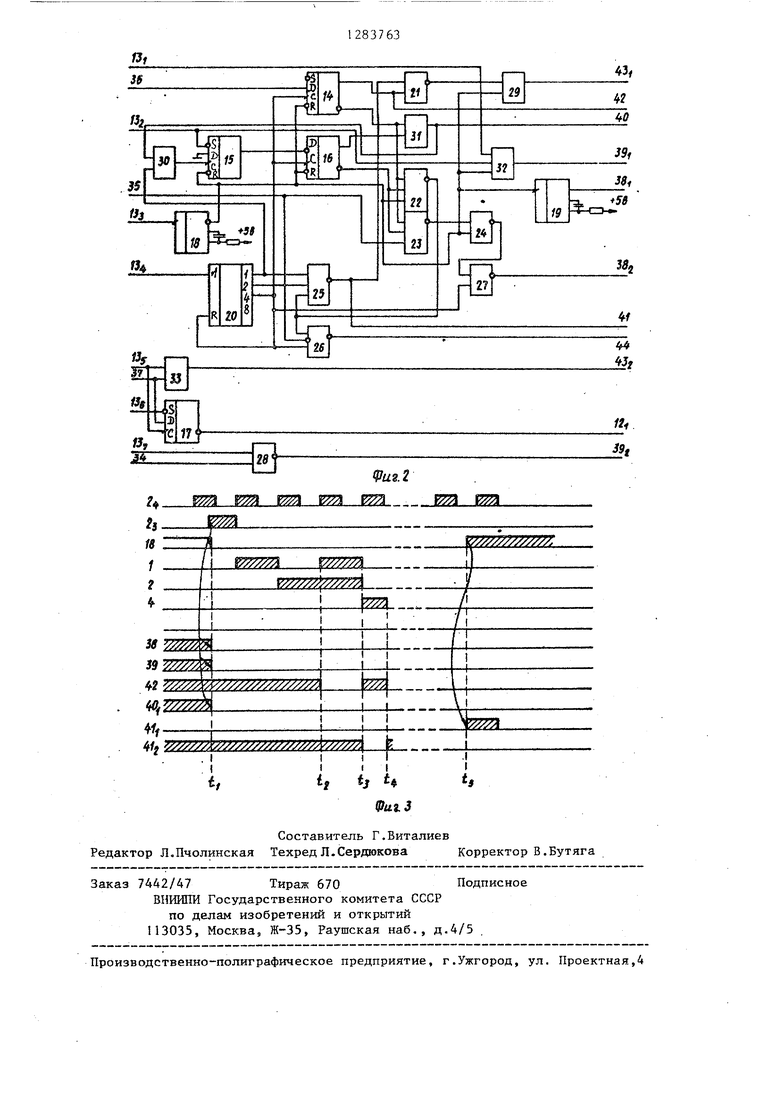

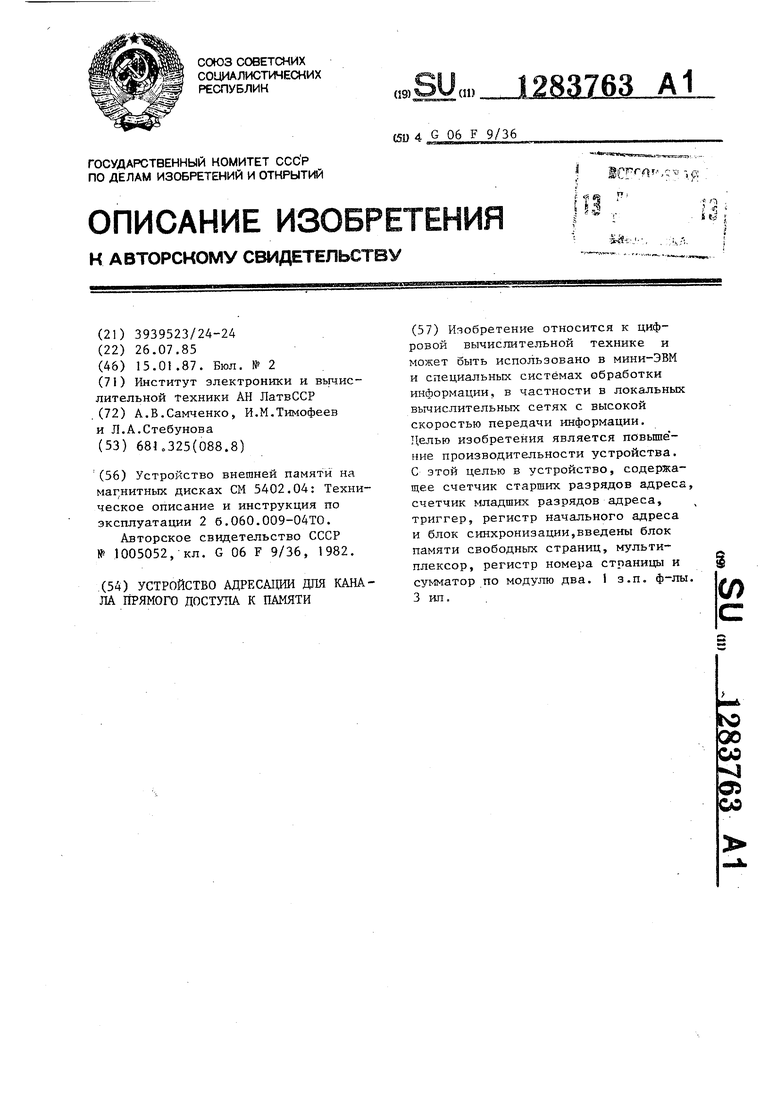

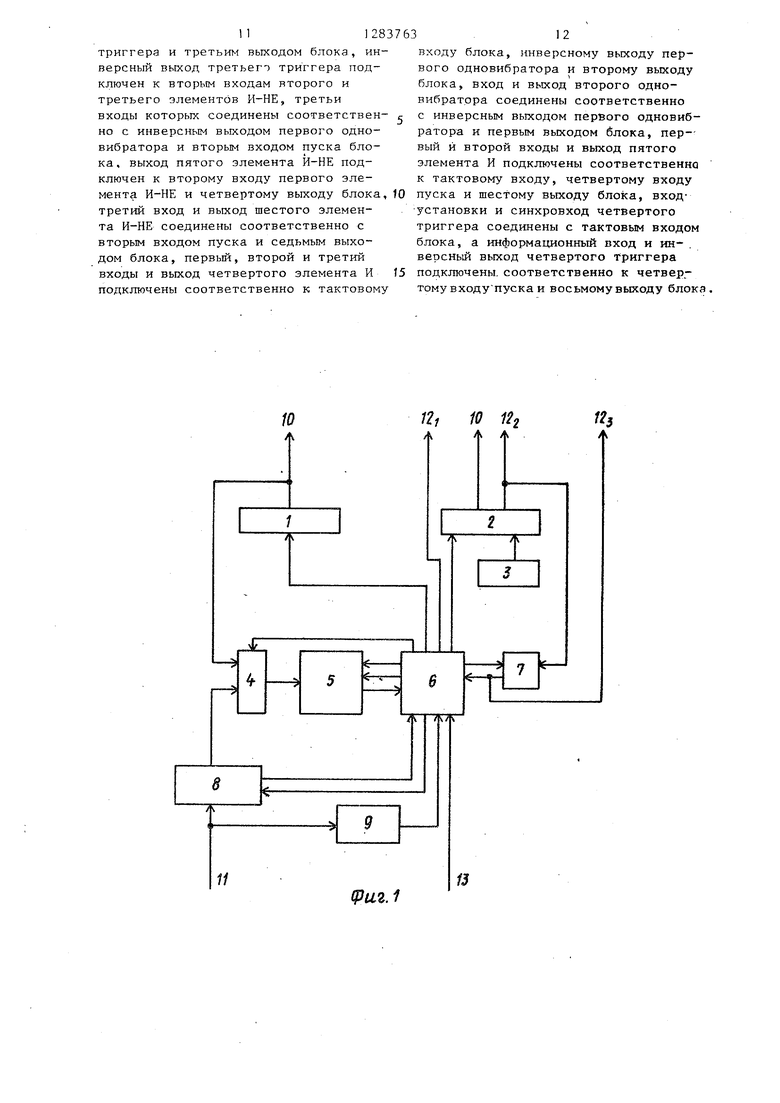

На фиг.1 представлена структург ная схема устройства; на фиг.2 - функциональная схема блока управления; на фиг.З т временная диаграмма работы блока управления.

Устройство содержит счетчик 1 старших разрядов адреса, счетчик 2

младших разрядов адреса, регистр 3 начального адреса, мультиплексор 4, блок 5 памяти свободных страниц, блок 6 управления, триггер. 7, регистр 8 номера страницы, сумматор 9 тю модулю два, адресный выход 10, группу информационных входов 11, выход 12 сопровождения адреса и

тактовый вход 13. Первый выход блока 6 управления соединен со счетным входом счетчика 1 старших разрядов адреса, второй выход блока 6 - со счетным входом счетчика 2. Выход триггера 7 соединен с первым входом пуска блока 6, информационный выход

. страниц может быть использован любо 35 блок памяти с однобитовой организацией, имеющей управляющий вход записи-чтения, например К155РУ7, К541РУ1. В качестве регистра 8 номера страницы может быть применен

блока 5 памяти свободных страниц соединен с вторым входом пуска блока 6,

информационный вход блока 5 соединен о любой регис тр , ™еющ й вто рой вы с третьим, а вход записи чтения - с четвертым выходами блока 6. Адресный вход блока 5 соединен с выходом мультиплексора 4, управлякмций вход которого соединен с пятым выходом блока 6. Первый информационный вход мультиплексора 4 подключен к выходу счетчика I, а второй - к первому ин-. Влок 6 управления содержит триг- формационному выходу регистра 8, вто- геры 14-17, одновибраторы 18-19, рой информационный выход которого Q ,счетчтяк 20, элементы И-НЕ 21-28, соединен с третьим входом пуска бло- элементы И 29-33, первый 34, вто- ка 6, а синхровход - с шестым выходом блока 6. Выход регистра 3 начального адреса подсоединен к информационход, указывающий, что в регистр записана информация, например регистр К589ИР12. В качестве сумматора 9 может быть использована любая схема 45 контроля по четности, например К531ИП5.

рой 35, третий 36 и четвертый 37 входы пуска, первый 38, второй 39(- 39, третий 40, четвертьй

рой 35, третий 36 и четвертый 37 входы пуска, первый 38, вт рой 39(- 39, третий 40, четверть

ному входу счетчика 2, выход перепол- j 41 , пятый 42, шестой 43,- 43 и нения которого связан с входом сбро- седьмой 44 выходы. Восьмой выход са триггера 7, а седьмой выход блока 6 соединен с входом установки триггера 7 . Выход сумматора 9 подключен к

блока 6 обозначен позицией 12,, товый вход блока 6 является такто вым входом 13 (13f- 137) устройс

ГО

15

83763 2

четвертому входу пуска блока 6. Информационный вход регистра 8 и вход сумматора 9 является группой информационных входов li устройства, а тактовый вход блока 6 соединен с тактовым входом 13 устройства (набором сигналов устройству от потребителя источника информации). Информационные выходы счетчика I и счетчика 2, являются адресным выходом 10 устройства, а восьмой выход блока 6 выход переполнения счетчика 2 и выход триггера 7 - выходом 12 сопровождения устройства (набором сигналов от устройства к потребителю - источнику информации).

В качестве счетчика 1 старших разрядов и счетчика 2 младших разрядов адреса может быть использован любой двоичный счетчик, например двоичные счетчики К 55ИЕ7, К555ИЕ7. В качестве выхода переполнения счетчика 2 младших разрядов адреса используется старший информационный разряд. В качестве регистра 3 начального адреса может быть использован узел, позволяющий задавать произвольный двоичный код, например набор тумблеров, переключателей, В качестве мультиплексора 4 применяют любой мультиплексор (2 на I)5 например мультиплексоры К531КПИ, К555КП11, В качестве блока 5 памяти свободных

. страниц может быть использован любой 35 блок памяти с однобитовой организацией, имеющей управляющий вход записи-чтения, например К155РУ7, К541РУ1. В качестве регистра 8 номера страницы может быть применен

20

25

30

о любой регис тр , ™еющ й вто рой вы Влок 6 управления содержит триг- геры 14-17, одновибраторы 18-19, Q ,счетчтяк 20, элементы И-НЕ 21-28, элементы И 29-33, первый 34, вто- любой регис тр , ™еющ й вто рой вы Влок 6 управления содержит триг- геры 14-17, одновибраторы 18-19, Q ,счетчтяк 20, элементы И-НЕ 21-28, элементы И 29-33, первый 34, вто- ход, указывающий, что в регистр записана информация, например регистр К589ИР12. В качестве сумматора 9 может быть использована любая схема 45 контроля по четности, например К531ИП5.

любой регис тр , ™еющ й вто рой вы Влок 6 управления содержит триг- геры 14-17, одновибраторы 18-19, счетчтяк 20, элементы И-НЕ 21-28, элементы И 29-33, первый 34, вто-

рой 35, третий 36 и четвертый 37 входы пуска, первый 38, второй 39(- 39, третий 40, четвертьй

41 , пятый 42, шестой 43,- 43 и седьмой 44 выходы. Восьмой выход

41 , пятый 42, шестой 43,- 43 и седьмой 44 выходы. Восьмой выход

блока 6 обозначен позицией 12,, так- товый вход блока 6 является тактовым входом 13 (13f- 137) устройства.

3

Устройство работает следующим образом.

Память, адресуемая устройству, логически разделена на страницы. Счетчик 1 служит для хранения кода номера страницы, а счетчик 2 кода адреса внутри страницы. Можно выделить 5 режимов работы устройства.

При включении цитания по внешнему сигналу сброса, поступающему по тактовому входу блока 6 (1-й режим работы устройства), блок 6 вырабатывает на четвертом выходе последова- .тельность сигналов записи, поступающую на вход записи-чтения блока 5, При этом на третьем выходе блока 6 вырабатьтается О, поступающий на информационный вход блока 5, т.е. во все ячейки блока 5 записываются О. Счетчик 1 сигналом, вырабатываемым на первом выходе блока 6, сбрасьшается ,а в счетчик 2 из регистра 3 по сигналу, выраба- тьюаемому на втором выходе блока 6 заносится код начального адреса внутри страницы. На седьмом вькоде блока 6 формируется сигнал установки в единичное состояние триггера 7 сигнал с выхода которого является управляющим сигналом на выходе 12 устройства и означает, что устройство готово к работе в режиме обслуживания .

В режиме обслуживания (2-й режим работы устройства) по заднему фронт сигнала запроса, поступающего на тактовый вход блока 6 (вход 13), блок 6 формирует сигнал модификации (увеличения на единицу) содержимого счетчика 2, по которому к

содержимому счетчика 2 прибавляется единица. В результате этой процедуры в счетчик 1 и счетчик 2 заносится следующий адрес формируемой посл .довательности адресов. Работа в 1ЭТОМ режиме продолжается до перепол iнения счетчика 2.

При переполнении счетчика 2 устройство переходит в 3-й режим рабо- 50 ты - режим маркировки заполненной страницы в блоке 5. Сигнал переполнения с выхода 12 счетчика 2 (в качестве этого выхода используется старший информационный разряд счет- 55 чика) сбрасьшает в О триггер 7. Блок 6 формирует на 5-м выходе управ-, ляющий сигнал, по которому .через муль типлексор 4 на адресный вход блока 5

O

5

0

5

5

0

5

0

0 5

поступает код номера страницы со счетчика i, а на четвертом выходе блока 6 формируется сигнал записи 1 поступающей на информационньш вход блока 5 с третьего выхода блока 6. Таким образом в блок 5 по адресу, содержащемуся в счетчике , записывается I, т.е. страница помечается как занятая.

Затем осутаествляется поиск свободной страницы адресуемой памяти (4-й режим работы устройства) в блоке 5. По сигналам с выхода блока 6 просматривается блок 5 по адресу, код которого подается через мультиплексор 4 с выхода счетчик,а 1 на адресный вход блока 5. Если страница занята, блок 6 прибавляет единицу к содержимому счетчику 1 и вновь производится чтение ячейки блока 5 по новому адресу. Эта процедура заканчивается при нахождении ячейки блока 5, содержащей нуль, т.е. при нахождении свободной страницы. При этом код адреса свободной страницы содержится в счетчике 1. Плок 6 вырабатывает сигнал установки триггера 7, Выход триггера 7 является выходом 12 сопровождения, наличие сигнала на котором означает, что устройство готово к формированио новой последовательности адресов.

Пятьш режим служит для освобождения какой-либо страницы адресуемой памяти. При этом через информационный вход 11 устройства в регистр 8 заносится код адреса освободившейся страницы. Загрузка регистра 8 вызывает появление на его втором выходе сигнала, поступающего на третий вход пуска блока 6. Получив этот сигнал, блок 6 вырабатьшает на пятом выходе сигнал, по которому на адресный вход блока 5 через мультиплексор 4 поступает код номера освобождаемой страницы из регистра 8. На вход записи- чтения блока 5 с четвертого выхода блока 6 поступает сигнал записи, а на информационный вход блока 5 - сигнал О с третьего выхода блока 6. Таким образом, в блок 5 осуществляется запись О по адресу, код которого содержится в регистре 8, т.е. страница помечается как свободная.

Блок 6 управления работает следующим образом. Цикл работы блока в i-M, S-jvi; и 5-м реж11мах жестко связан с циклом работы счетчика 20, на счетный вход которого постоянно поступают гмттульсы пинхросерни по входу 1. (фиг, 2). По каждому синхроимпульсу содерж№-юе счетчика 20 увеличивается на единицу. Модуль счетчика 20 равен 4, т.е. содержимое счетчика меняется от О до 4 и затем цикл счета повторяется.

В первом режиме работы устройства (режиме сброса) по сигналу сброса поступающему на вход 13,, блока 6, за запускается одновибратор 18 (момент t , фиг.З). Импульс отрицательной полярности с выхода одновибра- тора 18 сбрасывает в исходное состояние триггеры 14 - 16 и блок 6 отрабатывает цикл записи О в блок 5 цо адресу, код которого содержится в счетчике f . При этом импульс отрицательной полярности с выхода одновибратора 18 поступает на вход элементов 22 и 32. На выходе элемента 32 формируется сигнал с выхода 39, занесения в счетчик 2 кода адреса из регистра 3, Сигнал с выхода элемента 22 поступает на вход элемента 25. Так как триггер 14 в О, на выходе 42 блока 6з соединенном с управляющим входом мультиплексора 4, формируется сигнал О и код, содержащийся в счетчике I, через мультиплексор 4 поступает на адресные входы блока 5, На входе 40 блока 6, соединенном с информационным входом блока 5, элементом 31 формируется сигнал о, так как на вход элемента 3 с выхода б триггера поступает О, Счетчик 20 считает синхроимпульсы, поступающие по входу 3 блока бд и в тот момент, когда в счетчике 20 (момент й фиГоЗ), содержится двоичный код числа 3

(011) на выходе 41 блока 6 элементом 25 формируется сигнал О, являющийся сигналом записи-чтения блока 5. По сигналу на выходе 41 блока 6 в блок 5 записывается О, формирующийся на выходе 40 блока б элементом 31 по адресу, поступающему со счетчика 1 через мультиплексор 4 на адресный вход блока 5. В момент

(момент tj , фиг.З), когда содержимое счетчика становится равным 4

(100), на вход элемента 27 с третьего информационного выхода счетчика 20 поступает сигнал 1. На, втором входе элемента 27, соединенном с выходом элемента 24, также формируется сигнал 1, так как на вход

36

элелюнта 21 с. имходя чч,чоиио1;,чтора 18 поступает и -шульс отрицательной полярности. Таким об)1азом, на выходе 38, соединенном с выходом злемента 27, формируется сиг нал О. По сигналу О на выходе 38, который рВоТяется управляющим сигналом для счетчика 1 , к со;;,.ержимому счетчика 1 прибавляется единица. Счетчик 20

блока 6, досчитав до 4 (100), сбрасывается в О (момент ti, фиг.З), и процедура записи О в блок 5 повторяется, только О теперь записывается по новому адресу, код которого

содержится в счетчике 1. Количество циклов записи О в блок 5 зависит от длительности импульса, вырабатываемого одновибратором 18. Длительность т-1мпульса вырабатывается такой,

чтобы обеспечить обнуление всех ячеек блока 5. По КО1ЩУ отрицательного импульса, вырабатываемого одновибратором 18, запускается одновибратор

19 (момент tj., фиг.З), который формирует короткий положительный импульс на выходе 38, сбрасьшающий счетчик 1 в О. Таким образом по окончании процедуры сброса все ячейки блока 5 и разряды счетчика 1 соержат О, а счетчик 2 - код, заданный в регистре 3.

Во втором режиме режиме обслужиания по входу 13 в блок б поступает сигнал запроса и на выходе элеента 28, который соединен с выходом 392 блока 6, формируется сигнал модиикации счетчика 2 отрицательной полярности. Сигнал модифи- кации счетчика 2 формируется

т-олько при наличии сигнала на вы- ходе 34. Это означает, что в адресуемой памяти имеется свободная страни да.

В третьем режиме работы устройства (режиме завершения записи) в блок 6 по входу 13 поступает сигнал завершения записи, который устанавливает в единичное состояние триггер 15. В конце очередного цикла работы счетчика 20 (когда содержимое счетчика 20 становится равным 4) сигнал с третьего информационного выхода счетчика 20, поступаюпщй на синхровход триггера 16, устанавливает триггер б в единичное состояние, что приводит к появлению на выходе элемента 3 и выходе 40 блока б 1, т.е. на информационный вход блока 5

1

ПО vii ti: 1 . i ,1 | ыхоле t/ блока b гпп(-л тс 1Ч ;-чп- (), тпк как триггер ,14 сброшен, т.е. на адресные входы блока 5 через мультиплексор 4 поступает код номера.страницы, хранящий- ся в счетчике 1. На входы элемента 31 поступают I, так как триггер 14 сброшен, а триггер 15 установлен в единичное состояние. На выходе элемента 31, соединенном с выходом 40 блока 6 и информационным входом блока 5, формируется 1.

Логическая единица с выхода элемента 31 поступает на вход элемента 30, В тот момент, когда на первом информационном выходе счетчика 20 появится 1, на выходе элемента 30 формируется сигнал установки триг гера 15 в нулевое состояние по синх- роводу. На выходе элемента 22, один из входов которого является инверсным выходом триггера 16, формируется 1, поступающая на вход элемента 25, на выходе которого,так же как и в первом режиме работы, формируется сигнал записи в блок 5 на выходе 41 блока, т.е. страница с адресом, код которого содержится в счетчике 1, помечается в блоке 5 как занятая

В четвертом режиме работы устрой- ства (режиме поиска свободной страницы адресуемой памяти) на вход 35 блока 6 поступает 1, означающая, что страница с номером, код которой содержится в счетчике 1, занята. Че- рез элементы 23 и 24 1 поступает на вход элемента 27. В тот момент, когда содержимое счетчика 20 становится равным 4 (100), на выходе элемента 27 по выходу 38 формирует- ся сигнал модификации (увеличения на единицу) содержимого счетчика 1 и происходит чтение ячейки блока 5 по новому адресу. Эта процедура продолжается до тех пор, пока на входе 35 не появится О, т.е. очередная проверяемая страница окажется свободной. Сигнал О поступает на вход элемента 26, на входе которого с выхода 44 блока 6 форми- руется сигнал установки триггера 7 устройства. При этом в счетчике 1 содержится код адреса найденной свободной страницн.

В пятом режиме работы устройст- ва (освобождение занятой страницы адресуемой памяти) при занесении в регистр 8 кода номера освободившейся страницы на входе 36 блока 6 появляется 1, поступающая на инфор- мационньм вход триггера 14, который сигналом со счетчика 20, посту- на синхровод, устанавливается в единичное состояние. Сигнал 1 с выхода триггера 14,поступает на выход 42 блока 6, соединенный с управляющим входом мультиплексора 4 и код адреса и страницы из регистра 8 через мультиплексор 4 подается на адресный вход блока 5. Далее блок 6 производит запись О в ячейку блока 5, так же как и в первом режиме раПоты устройства. Сигнал 1 с выхо да триггера 14 поступает с инверсией через элемент 21 на вход элемента 29, на выходе которого формируется сигнал сброса регистра 8 устройства на выходе 43. блока 6. Если при занесении в регистр 8 произошла ошибка (код номера страницы содержит, неверный контрольный бит / на входе 37 блока 6 появляется О, поступающий на вход элемента 33, и сигнал записи в регистр 8 кода номера страницы, поступающий по входу 3у, не вьщается на выход 43 блока 6. Сигнал ошибки с входа 37 поступает на информацион- ньм вход триггера 17, а сигнал записи в регистр 8 - со входа 13 на синхровоход триггера 17. Таким образом, в случае возникновения ошибки на инверсном выходе триггера 17 появляется сигнал ошибки, выдаваемый с выхода 12,. Сигнал ошибки, вьщавае мьй с выхода 12,, сбрасьгоается внешним управляюп1им сигналом, поступаю- на вход 13 g и далее на вход установки триггера 17.

Таким образом, за счет автоматической перезагрузки устройства в процессе работы, а также автоматической инициализации устройства при включении питания по сигналу сброса устройство постоянно находится в состоянии готовности. Это позволяет использовать его в локальных вы- числительньпс сетях с высокой скоростью передачи информации. Устройство обеспечивает прием последовательности кадров информации, поступающих с малыми промежутками времени (цорядка нескольких микросекущ между кадрами. При высоких интенсив- ностях входного потока информационных кадров повьшгается производительность системы.

р м у л а

и

9 зоб

р е т е н

1283763 и я

, Устройство адресации для канала прямого доступа к памяти, содержащее счетчик старших разрядов адреса, счетчик младших разрядов адреса, триггер, регистр начального адреса и блок управленияSпервый вход пуска которого соединен с выходом триггера, вход сброса триггера под- к.т1ючен к выходу переполнения счетчика младших разрядов адреса, информационный вход которого соединен с выходом регистра начального адреса, первый и второй выходы блока управ- ления подключены соответственно к счетному входу счетчика старших разрядов адреса и счетному входу счетчика младших разрядов адреса, информационные выходы счетчиков старших и младших разрядов адреса являются адресным выходом устройства, а выход переполнения счетчика младших разрядов адреса является выходом сопровождения адреса устройства , отличающееся тем, 4TOs с целью повышения производительности устройства, оно содержит блок памяти свободных страниц, мультиплексор, регистр номера страницы и су матор по модулю два, вход которого и информационный вход регистра номера страницы объединены и соединены с группой информационны входов устройства, адресный вход, информационный вход, вход записи- чтения и выход блока памяти свободных ;траниц подключены соответственно к выходу мультиплексора, третьему и четвертому выходам и второму входу пуска блока управления, управляющий вход, первый и второй информационные входы мультиплексора соединены соответственно с пятым выходом блока управления, информацион- ВЕ гходом счвтчика старших разряд адреса и первым информационным вьтхо- дом регистра номера страни - Ь;ы, синхровход и второй информационный выход которого подключены соответственно к шестому выходу и третьему входу пуска блока управления, четвертый вход пуска, тактовый вход седьмой и восьмой выходы блока управления соединены соответствейно с выходом сут.матора по модулю два, тактовьм входом устройства, входом установки триггера и выходом сопровождения адреса устройства, который соединен также с выходом триггера.

о

O

15

0

O

5

0

0

2. Устройство по П.1, о а ю щ е е с я тем, что

т л и чающееся тем, что блок управления содержит счетчик, четыре триггера, два одновибратора, восемь элементов И-НЕ и пять злемен- тов И, при этом вход и инверсный выход первого одновибратора соединены соответственно с тактовым входом блока и входами сброса первого, второго и третьего триггеров, информационные входы первого, второго и третьего триггеров подключены соответственно к третьему входу пуска блока, шине нулевого потенциала и выходу второго триггера, прямой выход первого триггера соединен с первым входом первого элемента И-НЕ и пятым выходом блока, инверсный выход первого триггера подключен к первым входам второго и третьего элементов И-НЕ, первый и второй входы четвертого элемента И-НЕ соединены соответственно с выходом третьего элемента И-НЕ и инверсным вы5 ходом первого одновибратсра, выход второго элемента И-НЕ подключен к первым входам пятого и шестого элементов , первый вход и выход седьмого элемента И-НЕ соединены соответственно с выходом четвертого элемента И-НЕ и первьм выходом бло- ка, первый и второй входы и выход восьмого элемента И-НЕ подключены соответственно к тактовому входу, первому входу пуска и второму выходу блока, первый и второй входы и вы- ход первого элемента И соединены со- ответственно с выходом первого эле- мента И-НЕ, инверсным выходом-первого одновибратора и шестым выходом блока, первый и второй входы и выход второго элемента И подключены соответственно к выходу третьего элемента И, первому вь1ходу счетчика и син- хровходу второго триггера, вход установки которого соединен с тактовым входом блока, второй и третий входы пятого элемента И-НЕ подключены соответственно к первому и второму выходам счетчика, счетный вход которого соединен с тактовым входом блока, третий выход счетчика подключен к входу сброса счетчика, синхровходам первого и третьего триггеров и вторым входам шестого и седьмого элементов И-НЕ, первый и второй входы и выход третьего элемента И соединены соответственно с инверсным выходом первого триггера, прямым выходом третьего

5

55

n1283

триггера и третьим выходом блока, инверсный выход третьеп триггера подключен к вторьЕМ входам второго и третьего элементов И-НЕ, третьи входы которых соединены соответствен- но с инверсным выходом первого одно- вибратора и вторым входом пуска блока, выход пятого элемента И-НЕ подключен к второму входу первого элемента И-НЕ и четвертому выходу блока, третий вход и выход шестого элемента И-НЕ соединены соответственно с вторым входом пуска и седьмым выходом блока, первый, второй и третий входы и выход четвертого элемента И подключены соответственно к тактовому

12

входу блока, инверсному вькоду первого одновибратора и второму выходу блока, вход и выход второго одно- вибратора соединены соответственно с инверсным выходом первого одновибратора и первым выходом блока, пер-- вый и второй входы и выход пятого элемента И подключены соответственно к тактовому входу, четвертому входу пуска и шестому выходу блока, вход- установки и синхровход четвертого триггера соединены с тактовым входом блока, а информационный вход и ин- . вареный выход четвертого триггера подключены, соответственно к четвертому входу пуска и восьмому выходу блока,

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство для цветовой коррекции кинофильмов,передаваемых по телевидению | 1984 |

|

SU1233162A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для коррекции ошибок вычислительного процесса | 1991 |

|

SU1807487A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в мини-ЭВМ и специальных системах обработки информации, в частности в локальных вычислительных сетях с высокой скоростью передачи информации, Целью изобретения является повыше - ние производительности устройства. С зтой целью в устройство, содержащее счетчик старших разрядов адреса, счетчик младших разрядов адреса, триггер, регистр начального адреса и блок синхронизации,введены блок памяти свободных страниц, мультиплексор, регистр номера страницы и cybiMaTop по модулю два. I з.п. ф-лы. 3 ип. (Л

13

tpuz.i

33

iJ

ff

ff.

- C

J±.

J Л,

%.2 g S E g

4ff

4/ j Zify//j / //j y/ j /y//y7/ j } f ///y/ Y- - - -I

,1I I I.1

111 4, tj ,

.3

Составитель Г.Виталиев Редактор Л.Пчолинская Техред Л.Сердюкова Корректор В.Бутяга

Заказ 7442/47 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная,4

| Прибор для набора и печатания книг для слепых | 1926 |

|

SU5402A1 |

| Устройство адресации для канала прямого доступа к памяти | 1981 |

|

SU1005052A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-26—Подача