1

Изобретение относится к импульсной технике.

Цель изобретения - расширение функциональных возможностей за счет формирования линейных последовательностей с различными свойствами.

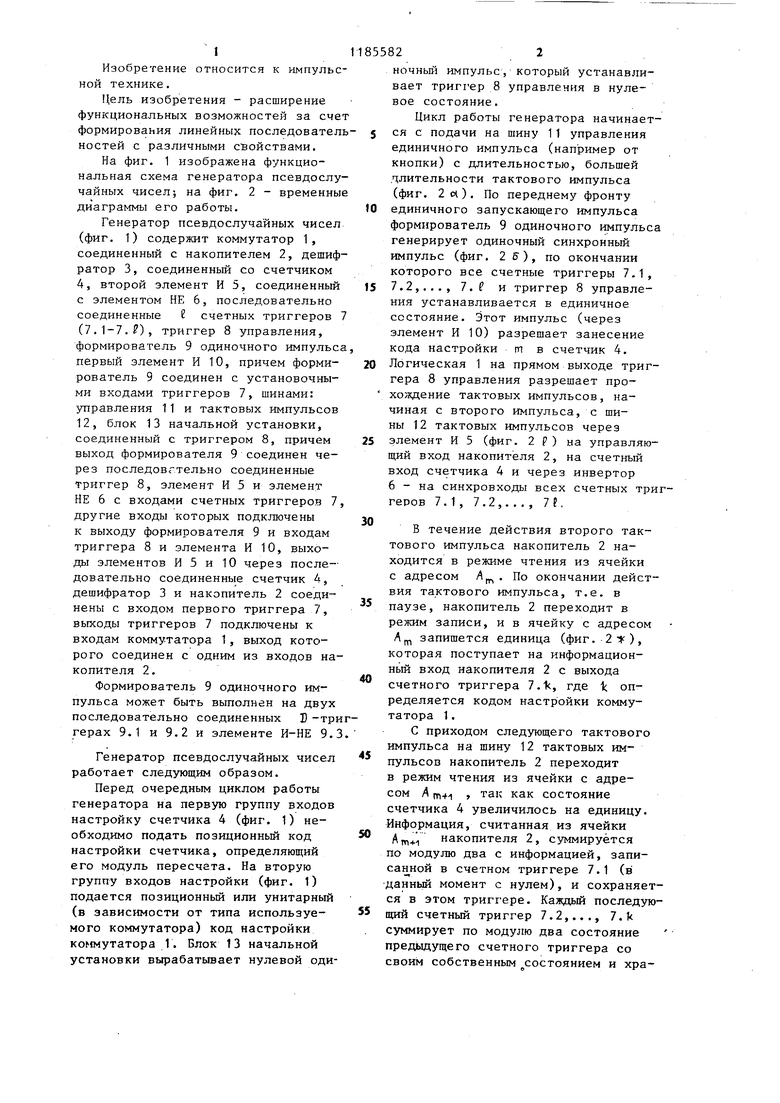

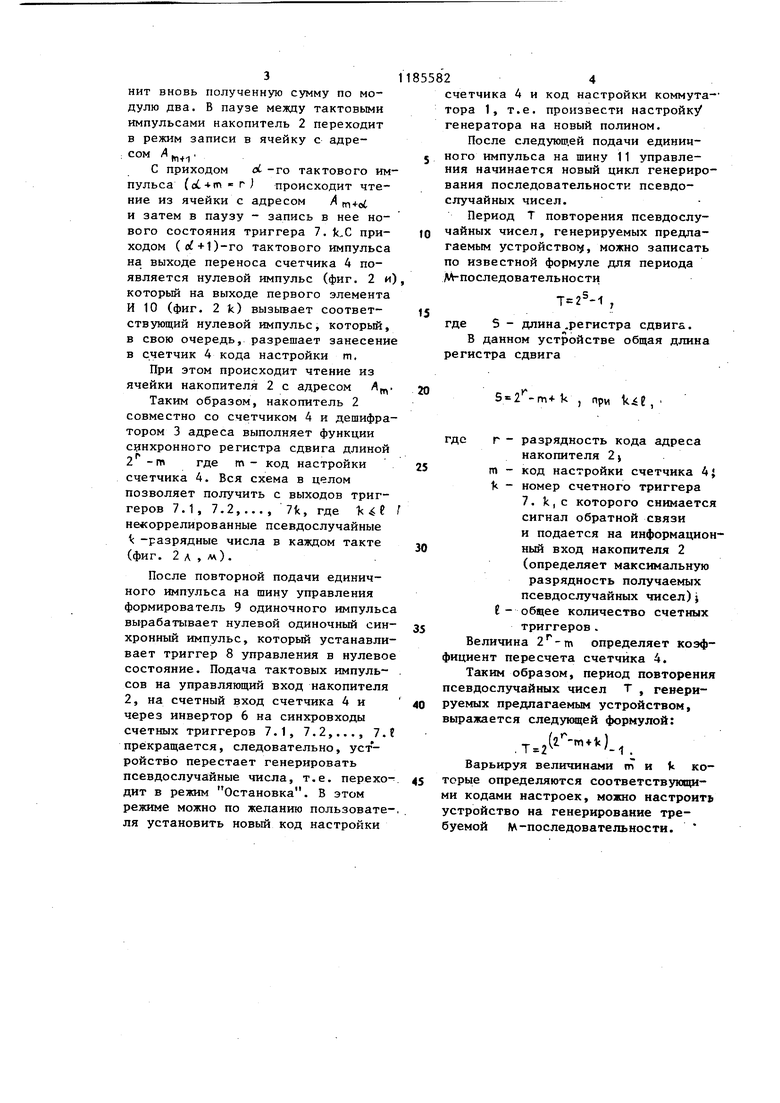

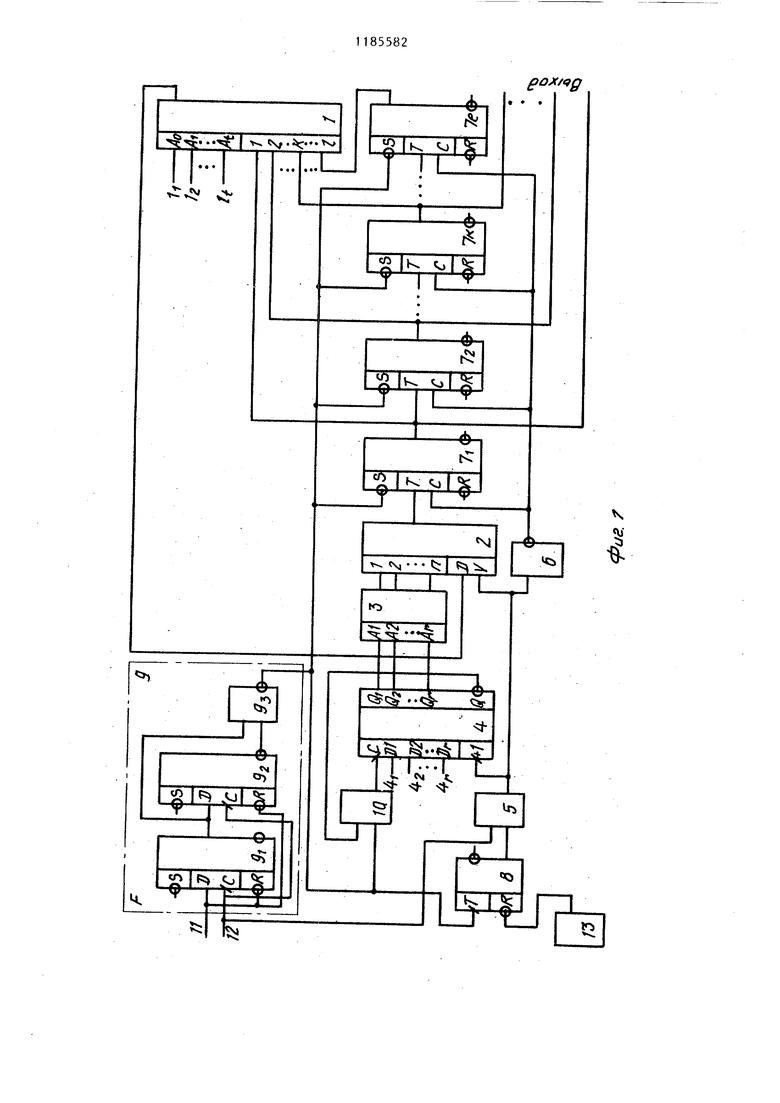

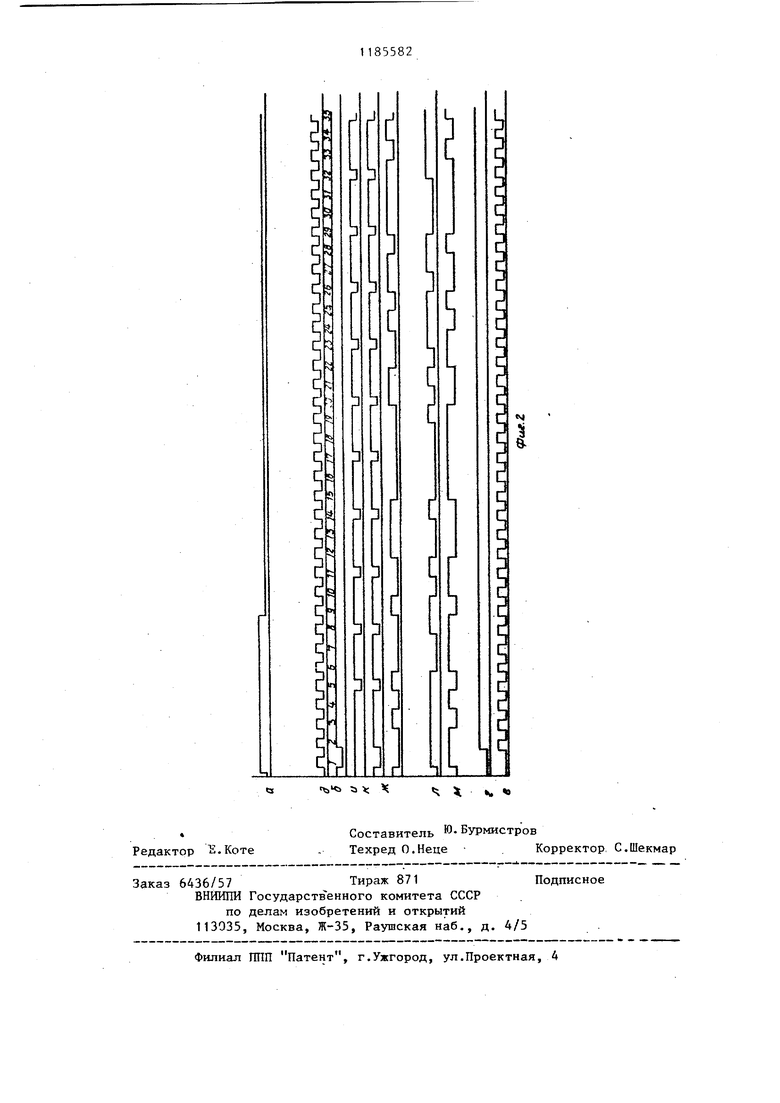

На фиг. 1 изображена функциональная схема генератора псевдослучайных чисел; на фиг. 2 - временные диаграммы его работы.

Генератор псевдослучайных чисел (фиг. 1) содержит коммутатор 1, соединенный с накопителем 2, дешифратор 3, соединенный со счетчиком 4, второй элемент И 5, соединенный с элементом НЕ 6, последовательно соединенные 2 счетных триггеров 7 (7.1-7.), триггер 8 управления, формирователь 9 одиночного импульса первый элемент И 10, причем формирователь 9 соединен с установочными входами триггеров 7, шинами: управления 11 и тактовых импульсов 12, блок 13 начальной установки, соединенный с триггером 8, причем выход формирователя 9 соединен через последовгтельно соединенные триггер 8, элемент И 5 и элемент НЕ 6 с входами счетных триггеров 7, другие входы которых подключены к выходу формирователя 9 и входам триггера 8 и элемента И 10, выходы элементов И 5 и 10 через последовательно соединенные счетчик 4, дешифратор 3 и накопитель 2 соединены с входом первого триггера 7, выходы триггеров 7 подключены к входам коммутатора 1, выход которого соединен с одним из входов накопителя 2.

Формирователь 9 одиночного импульса может быть выполнен на двух последовательно соединенных Б-три герах 9.1 и 9.2 и элементе И-НЕ 9.3

Генератор псевдослучайных чисел работает следующим образом.

Перед очередным циклом работы генератора на первую группу входов настройку счетчика 4 (фиг. 1) необходимо подать позиционный код настройки счетчика, определяющий его модуль пересчета. На вторую группу входов настройки (фиг. 1) подается позиционный или унитарный (в зависимости от типа используемого коммутатора) код настройки кo мyтaтopa 1. Блок 13 начальной установки вырабатывает нулевой оди855822

ночный импульс, который устанавливает триггер 8 управления в нулевое состояние.

Цикл работы генератора начинается с подачи на шину 11 управления единичного импульса (например от кнопки) с длительностью, большей длительности тактового импульса (фиг. 2 (Н ). По переднему фронту

10 единичного запускающего импульса формирователь 9 одиночного импульса генерирует одиночный синхронный импульс (фиг. 25), по окончании которого все счетные триггеры 7.1,

15 7.2,..., 7.Р и триггер 8 управления устанавливается в единичное состояние. Этот импульс (через элемент И 10) разрешает занесение кода настройки m в счетчик 4.

20 Логическая 1 на прямом выходе триггера 8 управления разрешает про хо;кдение тактовых импульсов, начиная с второго импульса, с шины 12 тактовых импульсов через

25 элемент И 5 (фиг. 2 Р) на управляющий вход накопителя 2, на счетньгй вход счетчика 4 и через инвертор 6 - на синхровходы всех счетных триггеров 7.1, 7.2,..., 7Г

В течение действия второго тактового импульса накопитель 2 находится в режиме чтения из ячейки с адресом А , По окончании действия тактового импульса, т.е. в паузе, накопитель 2 переходит в релсим записи, и в ячейку с адресом

А запишется единица (фиг. 2), которая поступает на информадионнь1й вход накопителя 2 с выхода счетного триггера 7.1, где Ic определяется кодом настройки коммутатора 1.

С приходом следующего тактового импульса на шину 12 тактовых импульсов накопитель 2 переходит в режим чтения из ячейки с адресом А так как состояние счетчика 4 увеличилось на единицу. Информация, считанная из ячейки

накопителя 2, суммируется по модулю два с информацией, записанной в счетном триггере 7.1 (в данньш момент с нулем), и сохраняеся в этом триггере. Каждьй последущий счетный триггер 7.2,..., 7.k суммирует по модулю два состояние предыдущего счетного триггера со своим собственным состоянием и хранит вновь полученную сумму по модулю два. В паузе между тактовыми импульсами накопитель 2 переходит в режим записи в ячейку с aRpeсом А.

С приходом oi -го тактового импульса ( г ) происходит чтение из ячейки с адресом / tn+oC и затем в паузу - запись в нее нового состояния триггера 7. k..C приходом (af+1)-ro тактового импульса на выходе переноса счетчика 4 появляется нулевой импульс (фиг. 2 и) который на выходе первого элемента И 10 (фиг. 2k) вызьгеает соответствующий нулевой импульс, который, в свою очередь, разрешает занесение в счетчик 4 кода настройки т.

При этом происходит чтение из ячейки накопителя 2 с адресом Л.

Таким образом, накопитель 2 совместно со счетчиком 4 и дешифратором 3 адреса выполняет функции синхронного регистра сдвига длиной 2 -т где т - код настройки счетчика 4. Вся схема в целом позволяет получить с выходов триггеров 7.1, 7.2,..., 7k, где 1 Р не«оррелированные псевдослучайные -разрядные числа в каждом такте (фиг. 2 л , м) .

После повторной подачи единичного импульса на шину управления формирователь 9 одиночного импульса вырабатывает нулевой одиночный синхронный импульс, который устанавливает триггер 8 управления в нулевое состояние. Подача тактовых импульсов на управляющий вход накопителя 2, на счетный вход счетчика 4 и через инвертор 6 на синхровходы счетных триггеров 7.1, 7.2,..., 7. прекращается, следовательно, устройство перестает генерировать псевдослучайные числа, т.е. переходит в режим Остановка. В этом режиме можно по желанию пользователя установить новый код настройки

счетчика 4 и код настройки коммутатора 1, т.е. произвести настройкУ генератора на новый полином.

После следующей подачи едининного импульса на шину 11 управления начинается новый цикл генерирования последовательности псевдослучайных чисел.

Период Т повторения псевдослучайных чисел, генерируемых предлагаемым устройствот#, можно записать по известной формуле для периода М-последовательности

,

где 5 - длина .регистра сдвига.

В данном устройстве общая длина регистра сдвига

у

k , при kiB ,

где г - разрядность кода адреса

накопителя 2

т - код настройки счетчика 4i Ч - номер счетного триггера 7. k, с которого снимается сигнал обратной связи и подается на информационный вход накопителя 2 (определяет максимальную разрядность получаемых псевдослучайных чисел)j t- общее количество счетных

триггеров .

Величина 2 - m определяет коэффициент пересчета счетчика 4.

Таким образом, период повторения псевдослучайных чисел Т , генерируемых предлагаемым устройством, выражается следукицей формулой:

.Т .

Варьируя величинами m и k которце определяются соответствующими кодами настроек, можно настроить устройство на генерирование требуемой М-последовательности.

ojf/tg

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сложной функции | 1985 |

|

SU1287135A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Генератор псевдослучайных последовательностей импульсов | 1976 |

|

SU640344A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Генератор двоичной последовательности | 1990 |

|

SU1709505A1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Устройство для измерения скорости изменения частоты | 1989 |

|

SU1620952A1 |

| Устройство для управления пневматической почтой | 1977 |

|

SU734099A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

1, ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ЧИСЕЛ, содержащий счетчик, разрядные выходы которого соединены с входами дешифратора, выходы которого соединены с информационными входами накопителя, шину тактовых импульсов, блок начальной установки, отличающийся тем, что, с целью расширения функциональных возможностей за счет формирования линейных последовательностей с различными свойствами, в него введены В последовательно соединенных счетных триггеров, первый и второй элементы И, триггер управления, формирователь одиночного импульса, коммутатор, шина управления, элемент НЕ, выход которого соединен с входами синхронизации Е счетных триггеров, выходы которых соединены с соответствующими входами коммутатора, выход которого соединен с ин- формационным входом накопителя. выход которого соединен со счетным входом первого из Р триггеров, установочные входы которых объединены между собой и соединены со счетным входом триггера управления, выходом формирователя и первым входом первого элемента И, второй вход которого соединен с выходом переполнения счетчика, вход синхронизации которого соединен с выходом первого элемента И, суммирующий вход счетчика соединен с входом управления накопителя, входом элемента НЕ и с выходом второго элемента И, первый вход которого соеg динен с шиной тактовых импульсов, (Л соединенной с первым входом формирователя одиночного импульса, с вторым входом которого соединена шина управления, второй вход второго элемента И соединен с выходом триггера управления, установочный вход которого соединен с выходом блока начальной установки, 2, Генератор по п, 1, отличающийся тем, что формирователь одиночного импульса содердит два последовательно соединенных D -триггера, прямой и инверсный выходы которых соединены с первым и вторым входами элемента И-НЕ соответственно, входы синхронизации Г -триггеров соединены между собой и с первым входом формирователя установочные входы D -триггеров соединены между собой и с вторым входом формирователя, выход элемента И-НЕ является выходом формирователя.

Авторы

Даты

1985-10-15—Публикация

1983-11-29—Подача