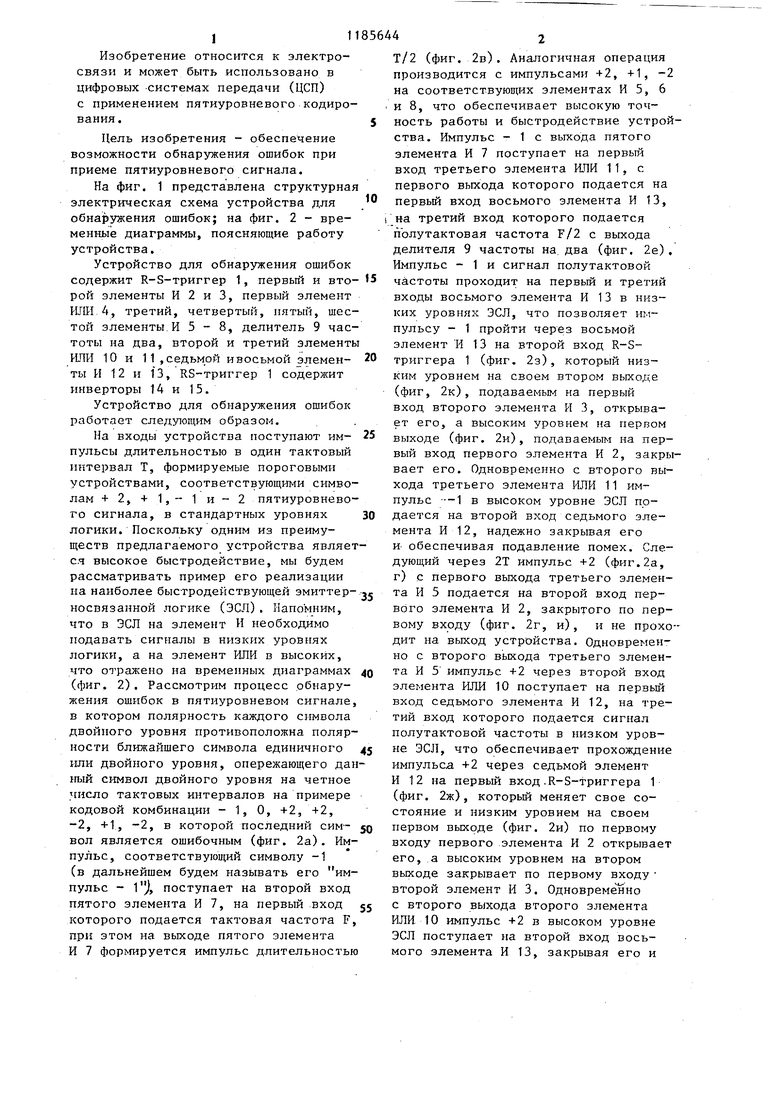

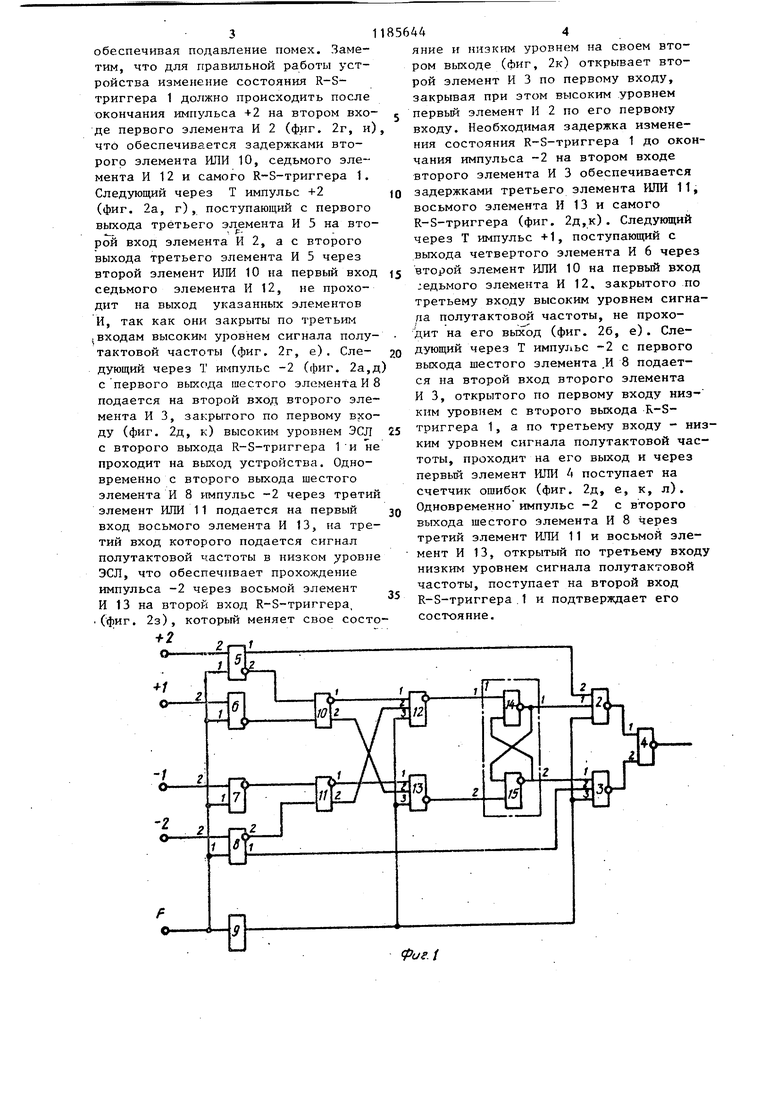

j1 Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи (ЦСП) с применением пятиуровневого кодирования. Цель изобретения - обеспечение возможности обнаружения ошибок при приеме пятиуровневого сигнала. На фиг. 1 представлена структурная электрическая схема устройства для обнаружения ошибок; на фиг. 2 - временные диаграммы, поясняющие работу устройства. Устройство для обнаружения ошибок содержит R-S-триггер 1, первый и второй элементы И 2 и 3, первый элемент ИЛИ 4, третий, четвертый, пятый, шестой элементы И 5-8, делитель 9 частоты на два, второй и третий элементы {ШР1 10 и 11 ,седьмой ивосьмой элементы И 12 и 13, RS-триггер 1 содержит инверторы 14 и 15. Устройство для обнаружения ошибок работает следующим образом. На входы устройства поступают импульсы длительностью в один тактовый интервал Т, формируемые пороговыми устройствами, соответствующими символам + 2, + 1, -- 1 и 2 пятиуровневого сигнала, в стандартных уровнях логики. Поскольку одним из преимуществ предлагаемого устройства являет ся высокое быстродействие, мы будем рассматривать пример его реализации па наиболее быстродействующей эмиттерносвязанной логике (ЭСЛ). Напомним, что в ЭСЛ на элемент И необходимо подавать сигналы в низких уровнях логики, а на элемент ИЛИ в высоких, что отражено на временных диаграммах (фиг. 2). Рассмотрим процесс обнаружения ошибок в пятиуровневом сигнале в котором полярность каждого символа двойного уровня противоположна полярности ближайшего символа единичного или двойного уровня, опережающего дан ный С1-1МВОЛ двойного уровня на четное число тактовых интервалов на примере кодовой комбинации - 1, О, +2,+2, -2, +1, -2, в которой последний символ является ошибочным (фиг. 2а). Импульс, соответствующий символу -1 (в дальнейшем будем называть его импульс - ), поступает на второй вход пятого элемента И 7, на первый вход которого подается тактовая частота F при этом па выходе пятого элемента И 7 форьгаруется импульс длительностью 4 Т/2 (фиг. 2в). Аналогичная операция производится с импульсами +2, +1, -2 на соответствующих элементах И 5, 6 и 8, что обеспечивает высокую точность работы и быстродействие устройства. Импульс - 1 с выхода пятого элемента И 7 поступает на первый вход третьего элемента ИЛИ 11, с первого выхода которого подается на первый вход восьмого элемента И 13, на третий вход которого подается полутактовая частота F/2 с выхода делителя 9 частоты на. два (фиг. 2е). Импульс - 1 и сигнал полутактовой частоты проходит на первый и третий входы восьмого элемента И 13 в низких уровнях ЭСЛ, что позволяет импульсу - 1 пройти через восьмой элемент И 13 на второй вход R-Sтриггера 1 (фиг. 2з), который низким уровнем на своем втором выходе (фиг, 2к), подаваемым на первый вход второго элемента И 3, открывает его, а высоким уровнем на первом выходе (фиг. 2и), подаваемым на первый вход первого элемента И 2, закрывает его. Одновременно с второго выхода третьего элемента ИЛИ 11 импульс -1 в высоком уровне ЭСЛ подается на второй вход седьмого элемента И 12, надежно закрывая его и обеспечивая подавление помех. Следующий через 2Т импульс +2 (фиг.2а, г) с первого выхода третьего элемента И 5 подается на второй вход первого элемента И 2, закрытого по первому входу (фиг. 2г, и), и не проходит на выход устройства. Одновременно с второго выхода третьего элемента И 5 импульс +2 через второй вход элемента ИЛИ 10 поступает на первый вход седьмого элемента И 12, на третий вход которого подается сигнал полутактовой частоты в низком уровне ЭСЛ, что обеспечивает прохождение импульса +2 через седьмой элемент И 12 на первый вход .К-5-триггера Г (фиг. 2ж), который меняет свое состояние и низким уровнем на своем первом выходе (фиг. 2и) по первому входу первого элемента И 2 открывает его, а высоким уровнем на втором выходе закрывает по первому входу второй элемент И 3. Одновременно с второго выхода второго элемента ИЛИ 10 импульс +2 в высоком уровне ЭСЛ поступает на второй вход восьмого элемента И 13, закрывая его и 3 обеспечивая подавление помех. Заметим, что для правильной работы устройства изменение состояния R-Sтриггера 1 должно происходить после окончания импульса +2 на втором вхо де первого элемента И 2 (фиг. 2г, и что обеспечивается задержками второго элемента ИЛИ 10, седьмого элемента И 12 и самого R-S-триггера 1. Следующий через Т импульс +2 (фиг. 2а, г), поступающий с первого выхода третьего элемента И 5 на второй вход элемента И 2, а с второго выхода третьего элемента И 5 через второй элемент ИЛИ 10 на первый вход седьмого элемента И 12, не проходит на выход указанных элементов И, так как они закрыты по третьим (Входам высоким уровнем сигнала полутактовой частоты (фиг. 2г, е). Следующий через Т импульс -2 (фиг. 2а,д с первого выхода шестого элемента И 8 подается на второй вход второго элемента И 3, закрытого по первому входу (фиг. 2д, к) высоким уровнем ЭОЛ с второго выхода R-S-триггера 1и не проходит на выход устройства. Одновременно с второго выхода шестого элемента И 8 импульс -2 через третий элемент ИЛИ 11 подается на первый вход восьмого элемента И 13, на третий вход которого подается сигнал полутактовой частоты в низком уровне ЭСЛ, что обеспечивает прохождение импульса -2 через восьмой элемент И 13 на второй вход R-S-триггера, (фиг. 2з), который меняет свое состо 44 яние и низким уровнем на своем втором выходе (фиг, 2к) открывает второй элемент И 3 по первому входу, закрывая при этом высоким уровнем первый элемент И 2 по его первому входу. Необходимая задержка изменения состояния R-S-триггера 1 до окончания импульса -2 на втором входе второго элемента И 3 обеспечивается задержками третьего элемента ИЛИ 11, восьмого элемента И 13 и самого R-S-триггера (фиг. 2д,к). Следующий через Т импульс +1, поступающий с выхода четвертого элемента И 6 через второй элемент ИЛИ 10 на первый вход :едьмого элемента И 12, закрытого по третьему входу высоким уровнем сигнапа полутактовой частоты, не проходит на его выход (фиг. 26, е). Следующий через Т импульс -2с первого выхода шестого элемента ,И 8 подается на второй вход второго элемента И 3, открытого по первому входу низКИМ уровнем с второго выхода R-Sтриггера 1, а по третьему входу - низким уровнем сигнала полутактовой частоты, проходит на его выход и через первый элемент ИЛИ 4 поступает на счетчик ошибок (фиг. 2д, е, к, л). Одновременно импульс -2 с второго выхода шестого элемента И 8 через третий элемент ИЛИ 11 и восьмой элемент И 13, открытый по третьему входу низким уровнем сигнала полутактовой частоты, поступает на второй вход R-S-триггера . 1 и подтверждает его состояние.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного сигнала в пятиуровневый сигнал | 1983 |

|

SU1172044A1 |

| Устройство приема тональных сигналов | 1991 |

|

SU1793560A1 |

| Устройство для обмена информацией | 1982 |

|

SU1131035A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

| Устройство для воспроизведения сигнала двухградационного изображения с носителя магнитной записи | 1983 |

|

SU1129649A1 |

| Устройство для сжатия цифрового телевизионного сигнала | 1985 |

|

SU1285626A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Способ детектирования манипулированных по частоте и фазе сигналов воспроизведения цифровой магнитной записи и устройство для его осуществления | 1991 |

|

SU1793461A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

УСТРОЙСТВО ДЛЯ ОБНАРЭТКЕНИЯ ОШИБОК, содержащее выполнент.1й на двух инверторах R-S-триггер, выходы которого подключены к первым входам первого и второго элементов И, выходы которых подключены к входам первого элемента ИЛИ, выход которого является выходом устройства, о т л ичающееся тем, что, с целью обнаружения ошибок при приеме пятиуровневого сигнала, введены шесть элементов И, два элемента ИЛИ и делитель частоты на два, вход которого объединен с первыми входами третьего, четвертого, пятого и шестого элементов И, вторые входы которых являются соответственно первым, вторым, третьим и четвертым входами устройства, при этом первый и второй выходы третьего элемента И подключены соответственно к второму входу первого элемента И и первому входу второго элемента ИЛИ, к второму входу которого подключен выход четвертого элемента И, выход пятого элемента И подключен к первому входу третьего элемента ИЛИ, а первый и второй выходы шестого элемента И подключены соответственно к второму входу второго элемента И и к второму входу третьего элемента ИЛИ, причем первые выходы второго и третьего элементов (Л ИЛИ подключены к первым входам соответственно седьмого и восьмого элементов И, к вторым входам которых % подключены вторые выходы соответственно третьего и второго элементов ИЛИ, а к третьим входам первого, второго, седьмого и восьмого элементов 00 И подключен выход делителя частоты ел на два, вход которого является пятым О) входом устройства, а выходы седьмого 4 и восьмого элементов И подключены 4 к первому и второму входам R-S-триггера.

| Устройство обнаружения ошибок при приеме псевдотроичного сигнала | 1977 |

|

SU658758A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Распоркип Л.Ф., Шульга В.Г., Богомолова В.Д | |||

| Об одной схеме регистрации сбоев регенератора | |||

| - Сб | |||

| трудов ЦНИИС Многоканальные системы связи, М., 1978. | |||

Авторы

Даты

1985-10-15—Публикация

1984-06-28—Подача