1C

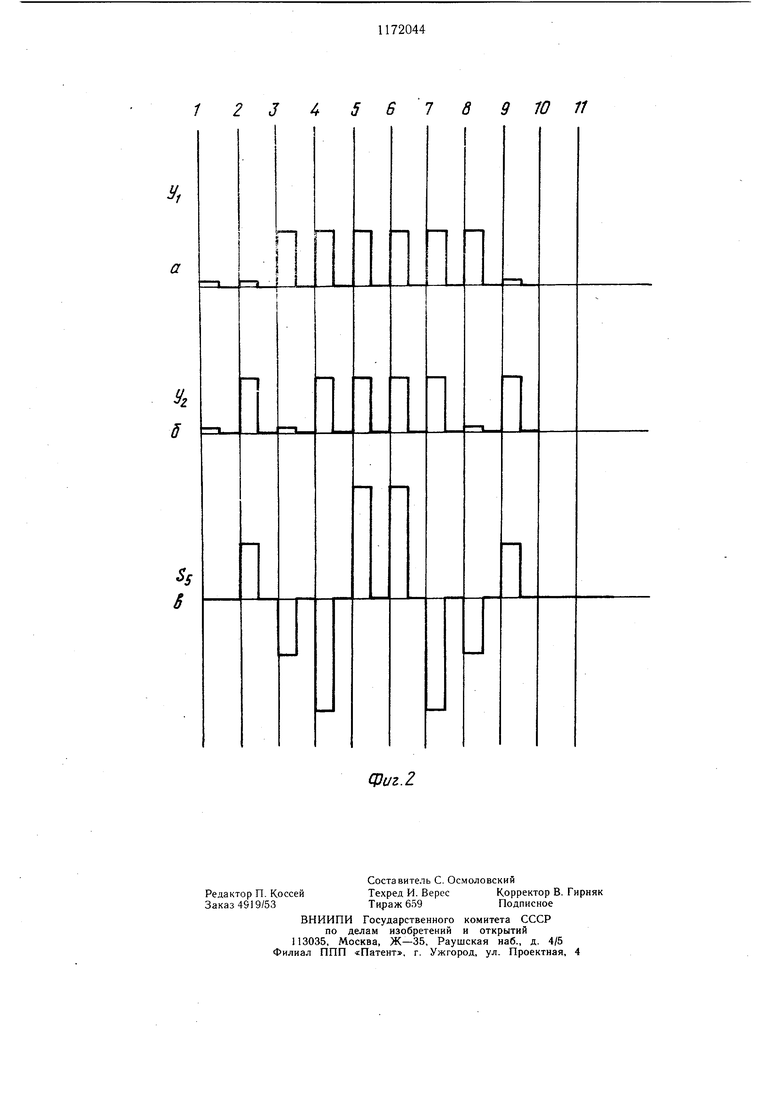

о Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи, оборудованных регенераторами пятиуровневого сигнала с квантованной обратной связью (КОС). Целью изобретения является повышение помехоустойчивости и увеличение быстродействия в линейном тракте с квантованной обратной связью в регенераторах. На фиг. 1 приведена структурная электрическая схема преобразователя; на фиг. 2 временные диаграммы, поясняющие его работу. Преобразователь двоичного сигнала в пятиуровневый сигнал содержит делитель 1 частоты на два, синхронизируемые конвертеры 2 и 3, блоки 4 и 5 управления полярностью импульсов, блоки 6-9 задержки, формирователь 10 пятиуровневого сигнала, каждый блок 4 и 5 управления полярностью содержит D-триггер 11, элементы 12 и 13 совпадения. Преобразователь двоичного сигнала в пятиуровневый сигнал работает следующим образом. Две синхронные двоичные последовательности Y и У (фиг. 2а,б) с тактовой частотой F (в частности, полученные из одной двоичной последовательности с удвоенной тактовой частотой 2F с помощью известных преобразователей) параллельно поступают на информационные входы двух синхронизируемых конвертеров 2 и 3, на входы синхронизации которых с парафазных выходов делителя 1 частоты на два подается полутактовая частота F/2. Каждый синхронизируемый конвертер 2 и 3 преобразует входные двоичные последовательности в четырехуровневый сигнал: Выходы конвертеров 000 01 1 1О -1 112 а поступающая на вход синхронизации конвертеров 2 и 3 полутактовая частота запрещает появление на его выходах символов четырехуровневного сигнала, следующих с полутактовой частотой. Запрещающие полутактовые последовательности на входах синхронизации синхронизируемых конвертеров 2 и 3 сдвинуты по фазе друг относительно друга на один период тактовой частоты F, при этом четырехуровневые последовательности символов на выходах синхронизируемых конверторов 2 и 3, следующие с полутактовой частотой F/2, также сдвинуты по фазе друг относительно друга на один период тактовой частоты F. Двоичные символы условной + 1, формирующиеся на первых выходах синхронизируемых конвертеров 2 и 3, соответственно через блоки 6 и 9 задержки, выравнивающие задержки в каналах символов единичного и двоичного уровней поступают на соответствующие входы формирователя 10 пятиуровневного сигна ла, обеспечивая формирование уровня +1 выходного пятиуровневого сигнала S $ (фиг. 2в). Аналогично двоичные символы условий -1, формирующиеся на вторых выходах синхронизируемых конвертеров 2 и 3, соответственно через блоки 7 и 8 задержки поступают на соответствующие входы формирователя 10 пятиуровневого сигнала, обеспечивая формирование уровня -1 выходного пятиуровневого сигнала Sj (фиг. 2в). Двоичные символы условной 2, формирующиеся на третьих выходах синхронизируемых конвертеров 2 и 3, поступают на соответствующие блоки 4 и 5 управления полярностью импульсов, каждый из которых устанавливает полярность символа двоичного уровня, противоположную полярности предыдущего символа на выходах соответствующего синхронизируемого конвертера. Блоки 4 и 5 управления полярностью импульсов двоичного уровня выполнены на D-триггере 11 и двух элементах 12 и 13 совпадения, причем инверсный выход D-триггера 11 подключен ко второму входу первого элемента совпадения 12, а прямой его выход - к первому входу второго элемента 13 совпадения. Одновременно инверсный выход D-триггера 11 подключен к его входу D. К входам S, R и С триггера подключены соответственно первый, второй и третий выходы синхронизируемых конвертеров 2 и 3, причем третий выход синхронизируемых конвертеров 2 и 3 одновременно подключен к первому входу первого и второму входу второго элементов 12 и 13 совпадения. Если импульс появляется на первом выходе синхронизируемых конвертеров 2 и 3 (символ условной + 1), он с помощью D-триггера 11 открывает первый элемент 12 совпадения, одновременно закрывая второй, и следующие за ним символ условной 2 с третьего выхода синхронизируемых конвертеров 2 и 3 проходит на первый выход блока 4 или 5 управления полярностью и далее на соответствующий вход формирователя 10 пятиуровневого сигнала, обеспечивая формирование уровня -2 выходного пятиуровневого сигнала S5 (фиг. 2в). Если импульс появляется на втором выходе синхронизируемых конвертеров 2 и 3 (символ условной -I), он с помощью D-триггера 11 открывает второй элемент 13 совпадения, закрывая первый, так что следующий за ним символ условной 2 проходит на второй выход блока 4 или 5 управления полярностью и далее на соответствующий вход формирователя 10 пятиуровневого сигнала, обеспечивая формирование уровня +2 выходного пятиуровневого сигнала 85 (фиг. 2в). Пройдя на выход одного из блоков 12 и 13 совпадения (например, первого). символ условной 2 по входу С меняет состояние D-триггера 11 и закрывает этот блок совпадения, открывая другой, так что следующий за ним символ условной 2 проходит на другой (второй) выход блоков 4 и 5 управления полярностью и обеспечивает инверсию полярности символа двойного уровня выходного пятиуровневого сигнала 85 (фиг. 2в). Таким образом, полярность символа двоичного уровня на выходе каждого канала управления формирователем всегда противоположна полярности любого предыдущего символа на выходах синхронизируемых конвертеров 2 и 3 этого канала. Поскольку частота появления символов на выходах синхронизируемого вонвертера 2, 3 равна F/2, полярность символа двоичного уровня всегда противоположна полярности символа, опережающего его на два тактовых интервала частоты F (фиг. 2V Сформированные в двух параллельных каналах управления формирователем две последовательности символов, следующих с полутактовой частотой F/2, сдвинутые по фазе друг относительно друга на один период тактовой частоты F, объединяются формирователем 10 пятиуровневого сигнала, на выходе которого формируется пятиуровневый сигнал 85 (фиг. 2в) тактовой частотой F, причем для любого данного .символа этого сигнала полярность символа двоичного уровня, расположенного в следующем тактовом интервале, всегда противоположна полярности символа, расположенного в предыдущем по отношению к данному символу тактовом интервале. Формирователь 10 пятиуровневого сигнала может быть выполнены, например, на управляемых источниках тока, включенных на общую нагрузИз сформированного пятиуровневого сигнала Ss (фиг. 2в) после передачи могут быть восстановлены исходные двоичные сигналы путем выполнения операций, обратных произведенным в преобразователе: принятый пятиуровневый сигнал с тактовой частотой F преобразуется в четырехуровневый, который затем разделяется на две синхронные двоичные последовательности Yj и Yj, идентичные исходным: 5 1 2 Обратный преобразователь весьма прост и реализуется на двух-Трехвходовых логических элементах. В предлагаемом преобразователе в соответствии с алгоритмом его работы для любого произвольно выбранного символа пятиуровневого сигнала $5полярность символа двойного уровня, расположенного в следующем по отношению к выбранному тактовом интервале, и полярность символа, расположенного в предыдущем по отношению к выбранному тактовом интервале - противоположны, что обеспечивает полную или частичную компенсацию межсимвольной помехи в момент приема выбранного символа, повышая тем самым помехозащищенность сигнала в целом по сравнению с известными преобразователями. Наличие в предлагаемом преобразователе двух параллельных каналов управления формирователем 10 пятиуровневого сигнала с пониженной вдвое частотой следования символов обеспечивает по крайней мере двукратное увеличение его быстродействия. Преимуществами предлагаемого преобразователя являются также относительная структурная простота, достигаемая за счет отсутствия обратных связей и применения функционально простых логических схем, а следовательно, экономичность, удобство в настройке и надежность j возможность организации встроенного контроля за работой линейного тракта цифровой системы передачи и входящих в него регенераторов по нарушению алгоритма преобразователя.

Си

&

123 56189 10 11

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО СИГНАЛА В ПЯТИУРОВНЕВЫЙ СИГНАЛ | 2010 |

|

RU2428787C1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1977 |

|

SU651491A1 |

| Устройство для обнаружения ошибок | 1984 |

|

SU1185644A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1983 |

|

SU1095397A1 |

| Устройство кодовой синхронизации | 1985 |

|

SU1328941A1 |

| Устройство для передачи двоичного сигнала | 1983 |

|

SU1376261A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1981 |

|

SU987832A1 |

| Преобразователь двоичного сигнала в квазитроичный | 1982 |

|

SU1095430A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Устройство преобразования линейного сигнала | 1986 |

|

SU1394446A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО СИГНАЛА В ПЯТИУРОВНЕВБ1Й СИГНАЛ, содержащий первый синхронизируемый конвертер, два блока задержки и формирователь пятиуровневого сигнала, отличающийся тем, что, с целью повышения помехоустойчивости и увеличения быстродействия в линейном тракте с квантованной обратной связью в регенераторах, в него введены второй синхронизируемый конвертер, два блока управления полярностью импульсов, два блока задержки и делитель частоты на два, вход которого является входом тактовой частоты преобразователя, а выходы делителя частоты на два «подключены к входам синхронизации первого и второго синхронизируемых конвертеров, информационные входы которых объединены и являются информационными входами преобразователя, при этом первый и второй выходы первого и второго синхронизируемых конвертеров подключены к входам соответственно первого и второго блоков управления полярностью импульсов и через соответствующие блоки задержки - к первому, второму, третьему и четвертому канальным входам формирователя пятиуровневого i сигнала, а третьи выходы первого и второго синхронизируемых конвертеров подключе(Л ны к третьим входам соответственно первого и второго блоков управления полярностью импульсов, выходы которьгх подключены соответственно к пятому, шестому, седьмому и восьмому входам формирователя пятиуровневого сигнала.

Фиг.г

| Kaneko Н., Sawai А., Feedblack Balanced Code for Multilevel PCM | |||

| Transmiss ion - «IEEE Trans Comm | |||

| - vol | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Ветряный двигатель | 1922 |

|

SU554A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1977 |

|

SU651491A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1985-08-07—Публикация

1983-03-09—Подача