на первой группе выходов устройства) соединены с выходами соответствующих т-мультиплексоров группы, управляющие входы мультиплексоров группы соединены с четвертым выходом признака режима регистра микрокоманд, пятый выход признака режима которого соединен с третьим входом первого элемента И, выход второго элемента ИЛИ соединен с входом установки в единицу триггера, выход которого соединен с входом чтения блока памяти микрокоманд и вторыми входами пятого и щестого элементов И, выходы которых соединены соответственно с входом записи регистра микрокоманд и счетным входом счетчика, вход записи счета которого соединен с одним из выходов соответствующего дещифратора группы, выход генератора тактовых импульсов соединен с входом распределителя импульсов, выход второго и третьего элементов И соединены соответственно с вторым и третьим входами первого элемента ИЛИ, третий вход второго элемента И является входом условий устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Способ интегрального преобразования релаксационных сигналов и устройство для его осуществления | 1986 |

|

SU1695324A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее счетчик адресов, блок памяти микрокоманд, регистр микрокоманд, группу дешифраторов, счетчик, генератор тактовых импульсов и первый элемент И, причем выход счетчика адресов соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, выход поля многофункционального назначения которого соединен с информационным входом счетчика и информационными входами дешифраторов, выходы которых являются первой группой выходов устройства, выход первого элемента И соединен со счетным входом счетчика адресов, отличающееся тем, что, с целью расширения функциональных возможностей путем реализации выработки управляющих сигналов внутри такта и реализации условных переходов, оно дополнительно содержит второй, третий, четвертый и пятый элементы И, первый, второй и третий элементы ИЛИ, триггер, распределитель импульсов, генератор одиночного импульса, группу мультиплексоров и мультиплексор адреса, причем первая группа информационных входов мультиплексора адреса соединена с выходом поля многофункционального назначения регистра микрокоманд, первый выход признака режима которого соединен с первыми входами третьего элемента И и третьего элемента ИЛИ, выход которого соединен с управляющим входом мультиплексора адреса, второй икформационный вход которого является входом кода команды устройства, второй вход третьего элемента ИЛИ соединен с первым входом второго элемента И и вторым выходом признака режима регистра микрокоманд, третий выход признака режима которого соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом переполнения счетчика и первым входом первого элемента И, второй вход которого соединен с первым выходом распределителя импульсов, первыми информационными входами мультиплексоров группы и третьим входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом генератора одиночного импульса и первым входом первого элемента ИЛИ, выход которого i соединен с входом записи расчета счетчика адресов, информационный вход которого (Л соединен с выходом мультиплексора адреса, второй выход распределителя импульсов соединен с вторыми входами второго и третьего элементов И и вторыми информационными входами мультиплексоров группы, третьи информационные входы которых соединены с третьим выходом распределителя импульсов и входом запуска генератора одиночного импульса, вход начальной уста00 новки которого подключен к входу пуска 00 устройства, четвертый выход распределителя импульсов соединен с входом установки в ноль триггера и четвертыми инОО О5 формационными входами мультиплексоров группы, пятые информационные входы которых соединены с пятым выходом распределителя импульсов и первыми входами пятого и шестого элементов И, остальные (п-5) выходов распределителя импульсов (где пвозможное количество микротактов внутри такта, ) соединены с остальными (л-5) информационными входами мультиплексоров группы, выходы которых подключены к второй группе выходов устройства, стробирующие входы т- дешифраторов группы (т- максимальное количество микротактируемых управляющих сигналов, формируемых

1

Изобретение относится к области вычислительной техники и может быть использовано в устройствах управления цифровых вычислительных машин (ЦВМ) и пультах управления ЦВМ.

Цель изобретения - расширение функциональных возможностей путем реализации выработки управляющих сигналов внутри такта и реализации условных переходов.

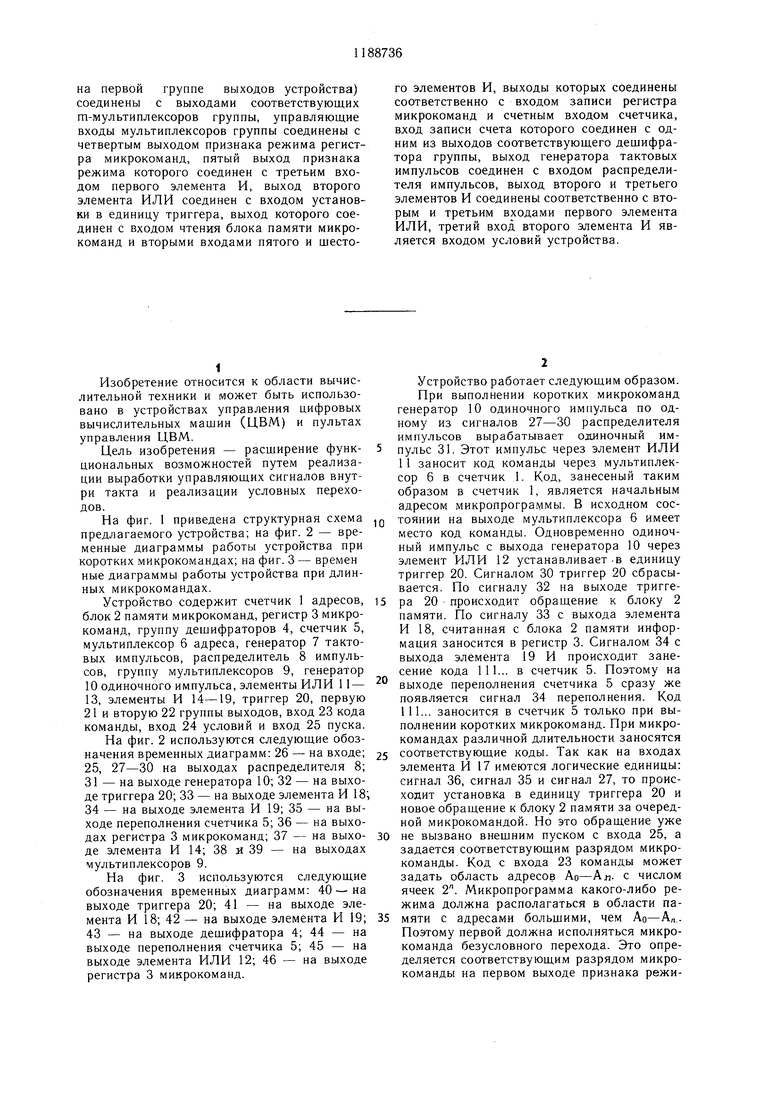

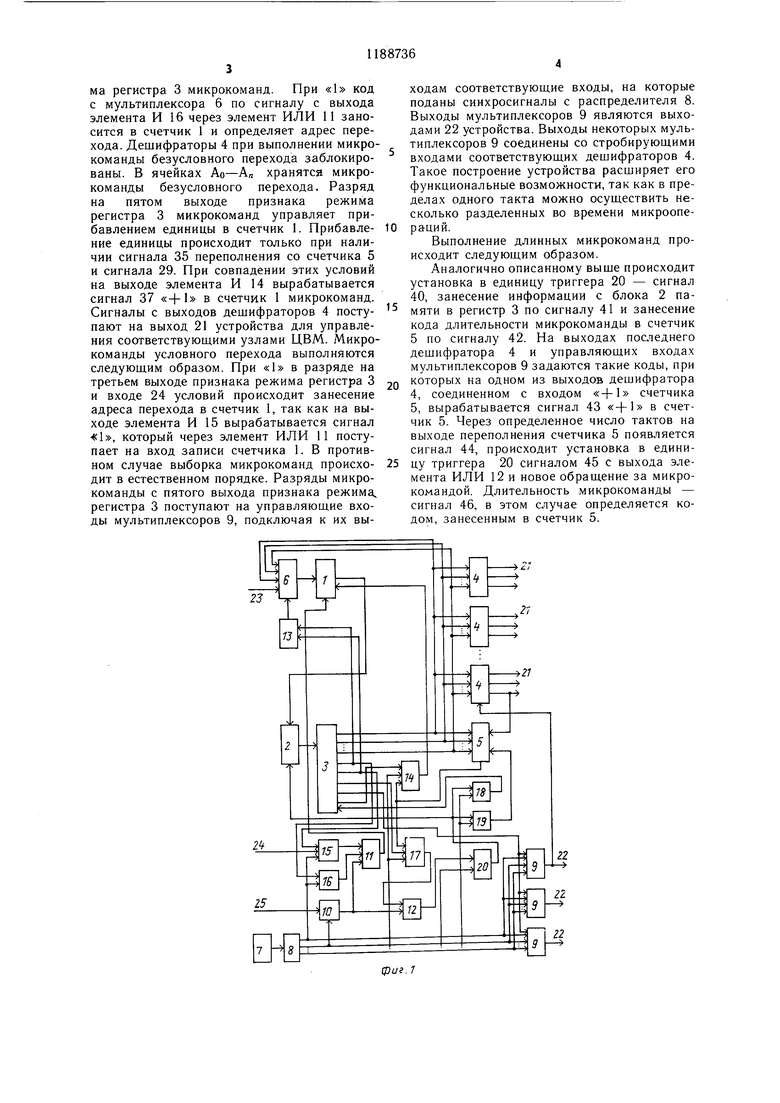

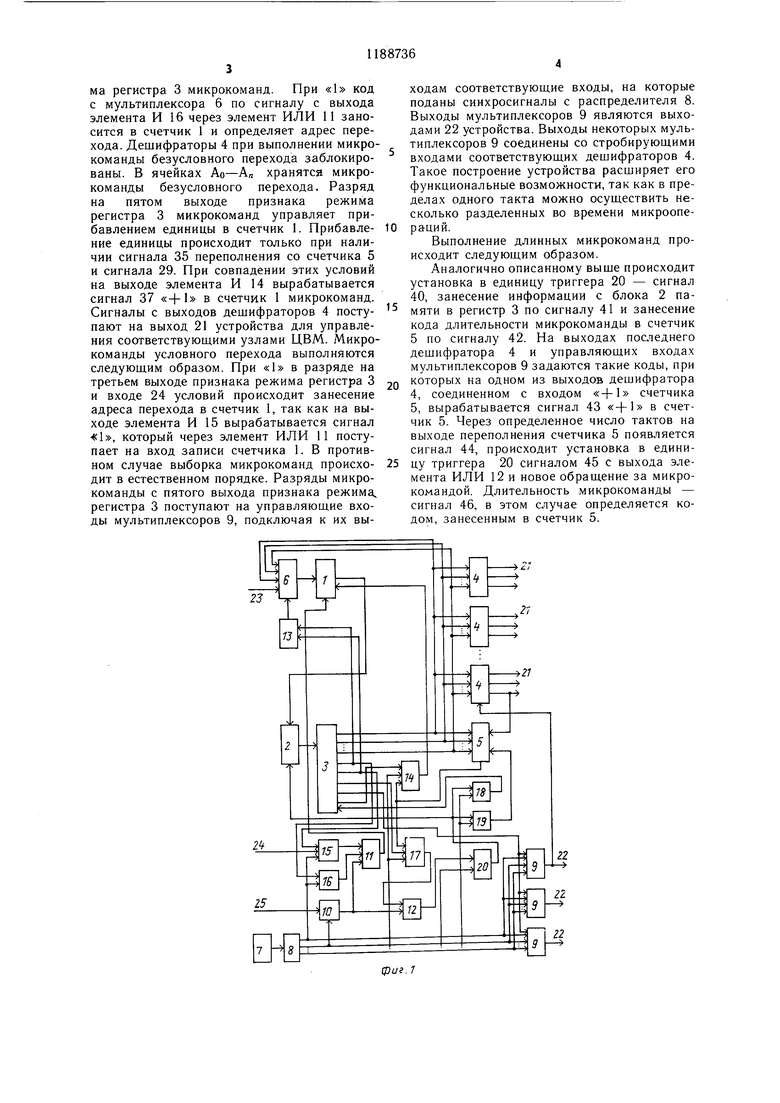

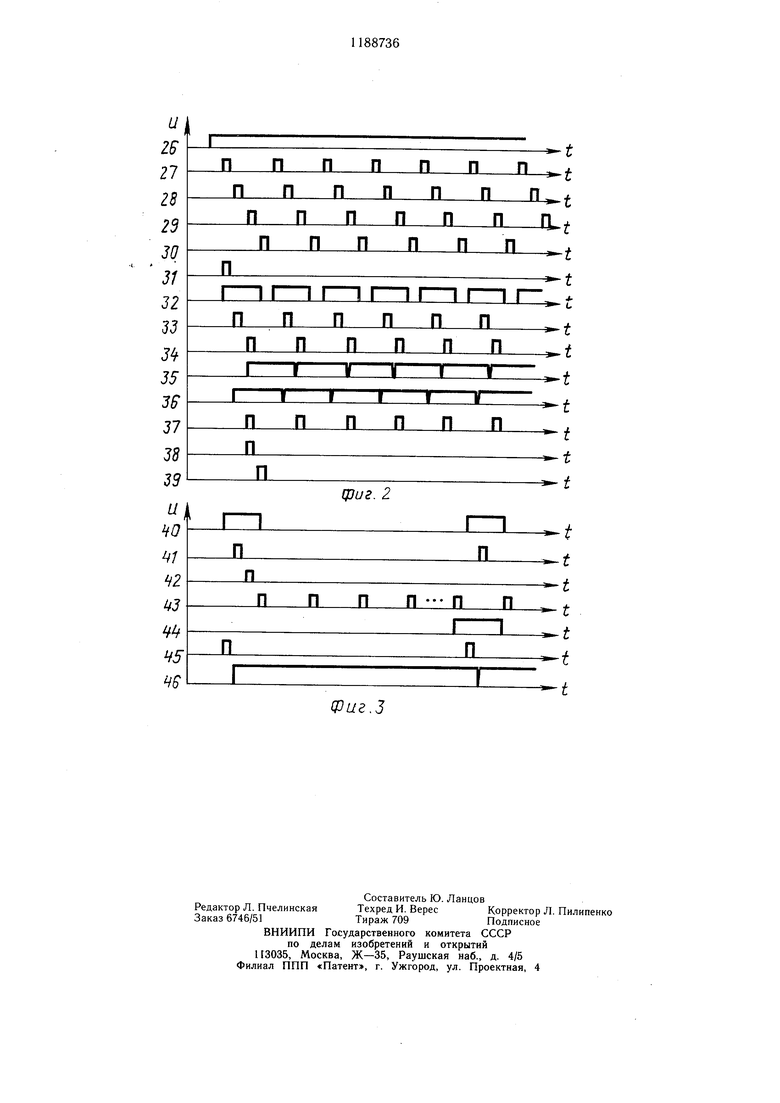

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы устройства при коротких микрокомандах; на фиг. 3 - времен ные диаграммы работы устройства при длинных микрокомандах.

Устройство содержит счетчик 1 адресов, блок 2 памяти микрокоманд, регистр 3 микрокоманд, группу дещифраторов 4, счетчик 5, мультиплексор 6 адреса, генератор 7 тактовых импульсов, распределитель 8 импульсов, группу мультиплексоров 9, генератор 10 одиночного импульса, элементы ИЛИ 11- 13, элементы И 14-19, триггер 20, первую 21 и вторую 22 группы выходов, вход 23 кода команды, вход 24 условий и вход 25 пуска.

На фиг. 2 используются следующие обозначения временных диаграмм: 26 - на входе; 25, 27-30 на выходах распределителя 8; 31 - на выходе генератора 10; 32 - на выходе триггера 20; 33 - на выходе элемента И 18 34 - на выходе элемента И 19; 35 - на выходе переполнения счетчика 5; 36 - на выходах регистра 3 микрокоманд; 37 - на выходе элемента И 14; 38 и 39 - на выходах мультиплексоров 9.

На фиг. 3 используются следующие обозначения временных диаграмм: 40-на выходе триггера 20; 41 - на выходе элемента И 18; 42 - на выходе элемента И 19; 43 - на выходе дешифратора 4; 44 - на выходе переполнения счетчика 5; 45 - на выходе элемента ИЛИ 12; 46 - на выходе регистра 3 микрокоманд.

Устройство работает следующим образом.

При выполнении коротких микрокоманд генератор 10 одиночного импульса по одному из сигналов 27-30 распределителя импульсов вырабатывает олшночный импульс 31. Этот импульс через элемент ИЛИ 11 заносит код команды через мультиплексор 6 в счетчик 1. Код, занесеный таким образом в счетчик 1, является начальным адресом микропрограммы. В исходном состоянии на выходе мультиплексора 6 имеет место код команды. Одновременно одиночный импульс с выхода генератора 10 через элемент ИЛИ 12 устанавливает-в единицу триггер 20. Сигналом 30 триггер 20 сбрасывается. По сигналу 32 на выходе триггера 20 происходит обращение к блоку 2 памяти. По сигналу 33 с выхода элемента И 18, считанная с блока 2 памяти информация заносится в регистр 3. Сигналом 34 с выхода элемента 19 И происходит занесение кода 111... в счетчик 5. Поэтому на выходе переполнения счетчика 5 сразу же появляется сигнал 34 переполнения. Код 111... заносится в счетчик 5 только при выполнении коротких микрокоманд. При микрокомандах различной длительности заносятся соответствующие коды. Так как на входах элемента И 17 имеются логические единицы: сигнал 36, сигнал 35 и сигнал 27, то происходит установка в единицу триггера 20 и новое обращение к блоку 2 памяти за очередной микрокомандой. Но это обращение уже не вызвано внешним пуском с входа 25, а задается соответствующим разрядом микрокоманды. Код с входа 23 команды может задать область адресов АО-Ал. с числом ячеек 2. Микропрограмма какого-либо режима должна располагаться в области памяти с адресами большими, чем АО-АЛ.. Поэтому первой должна исполняться микрокоманда безусловного перехода. Это определяется соответствующим разрядом микрокоманды на первом выходе признака режима регистра 3 микрокоманд. При «1 код с мультиплексора 6 по сигналу с выхода элемента И 16 через элемент ИЛИ 11 заносится в счетчик 1 и определяет адрес перехода. Дешифраторы 4 при выполнении микрокоманды безусловного перехода заблокированы. В ячейках АО-А„ хранятся микрокоманды безусловного перехода. Разряд на пятом выходе признака режима регистра 3 микрокоманд управляет прибавлением единицы в счетчик 1. Прибавление единицы происходит только при наличии сигнала 35 переполнения со счетчика 5 и сигнала 29. При совпадении этих условий на выходе элемента И 14 вырабатывается сигнал 37 «+1 в счетчик 1 микрокоманд. Сигналы с выходов дешифраторов 4 поступают на выход 21 устройства для управления соответствуюш,ими узлами ЦВМ. Микрокоманды условного перехода выполняются следуюшим образом. При «1 в разряде на третьем выходе признака режима регистра 3 и входе 24 условий происходит занесение адреса перехода в счетчик 1, так как на выходе элемента И 15 вырабатывается сигнал «1, который через элемент ИЛИ 11 поступает на вход записи счетчика 1. В противном случае выборка микрокоманд происходит в естественном порядке. Разряды микрокоманды с пятого выхода признака режима, регистра 3 поступают на управляюш,ие входы мультиплексоров 9, подключая к их выходам соответствуюш,ие входы, на которые поданы синхросигналы с распределителя 8. Выходы мультиплексоров 9 являются выходами 22 устройства. Выходы некоторых мультиплексоров 9 соединены со стробируюшими входами соответствуюш.их дешифраторов 4. Такое построение устройства расширяет его функциональные возможности, так как в пределах одного такта можно осуществить несколько разделенных во времени микроопераций.

Выполнение длинных микрокоманд происходит следующим образом.

Аналогично описанному выше происходит установка в единицу триггера 20 - сигнал 40, занесение информации с блока 2 памяти в регистр 3 по сигналу 41 и занесение кода длительности микрокоманды в счетчик 5 по сигналу 42. На выходах последнего дешифратора 4 и управляющих входах мультиплексоров 9 задаются такие коды, при которых на одном из выходов дешифратора

4,соединенном с входом «+1 счетчика

5,вырабатывается сигнал 43 «-f 1 в счетчик 5. Через определенное число тактов на выходе переполнения счетчика 5 появляется сигнал 44, происходит установка в единицу триггера 20 сигналом 45 с выхода элемента ИЛИ 12 и новое обращение за микрокомандой. Длительность микрокоманды - сигнал 46, в этом случае определяется кодом, занесенным в счетчик 5.

СРиг.З

фиг. 2

| Микропрограммное устройство управле-Ния | 1979 |

|

SU802963A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1979 |

|

SU834700A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-30—Публикация

1984-06-22—Подача