Изобретение относится к вычислительной технике и предназначено для создания цифровых устройств, реализующих интегральные преобразования и решающих интегральные уравнения в случае релаксационных сигналов. К классу релаксационных сигналов принадлежат сигналы, производные которых асимптотически стремятся к нулю при стремлении аргумента к бесконечности. Релаксационные сигналы описываются через так называемый релаксационный спектр д(Я) функциями вида

x(u) /0°° g(A)R(u,A)dA, и о (1) с апериодическими ядрами R(u, A ), в частности е-Яи1-е Яи uA

2+А2

2+А2

и +л и

Изобретение предназначено для реализации интегральных преобразований и решения интегральных уравнений, имеющих базисные ядра, зависящие от произведения (частного) аргумента, типа

УМ-/ к(тг)х(и)-тг 2)

у(г) - / K(ru)x(u)du;(3)

y(r) r/ K(ru)x(u)du.(4)

Цель изобретения расширение класса решаемых задач и повышение быстродействия.

Способ основывается на следующих положениях.

В случае дискретизации согласно закону геометрической прогрессии

un Moqn.q 1, n 0,fl,+2 (5)

где wo - свободно выбираемое фиксированное значение аргумента входного сигнала преобразование вида (2) при фиксированном значении аргумента г и весовой функции

г-0/U.W

h«(m-n).sJK(ZJ)

г„/и.

о,5 т- и

ТЧ

(6)

принимает вид

«ffrvYVZ Ь(пЬУ(гоЧут-и),

П - со(7

что можно также переписать в виде

О

у(г„О X Х(г0сГ) h(m-n).

. ГЧ (8)

Зависимости (7) и (8) показывают, что вследствие использования выборки мгновенных значений входного сигнала согласно закону геометрической прогрессии интегральные преобразования типа (2) независимо от конкретного вида базисного

0

5

0

5

0

5

ядра К( -), осуществляются весовым суммированием мгновенных значений входного сигнала, а изменение аргумента выходного сигнала реализуется смещением отсчетов весовой функции относительно выборок входного сигнала.

В случае отличных от вида (2) интегральных преобразований с базисными ядрами, зависящими от произведения (частного) аргументов, в частности (3) и (4) необходимо данные интегральные преобразования привести к виду (2), что всегда возможно, модифицируя вид базисного ядра или входного сигнала.

Вид алгоритмов (7) и (8) сохраняется при выполнении обратных интегральных преобразований, т.е. для решения интегральных уравнений. В данном случае меняются лишь методы определения значений отсчетов весовых функций.

Осуществление предложенного способа в устройстве требует усечения весовой функции и действие над ограниченными в протяженности последовательностями входных сигналов x(u0qn).

Необходимы следующие преобразования алгоритма (7) для реализации его в устройстве.

Ограничиваясь последовательностью весовой функции h(n) длины N 2N + 1 и

полагая a q, получают окончательный вид алгоритма применительно к его технической реализации в устройстве

,

N1

,Я

m-i,

h(K)x

N +m-K- 1

0

I k i a q +1

гдеКЮ /

I k a q

(Ф

K(z);a q-° 5-N-1;

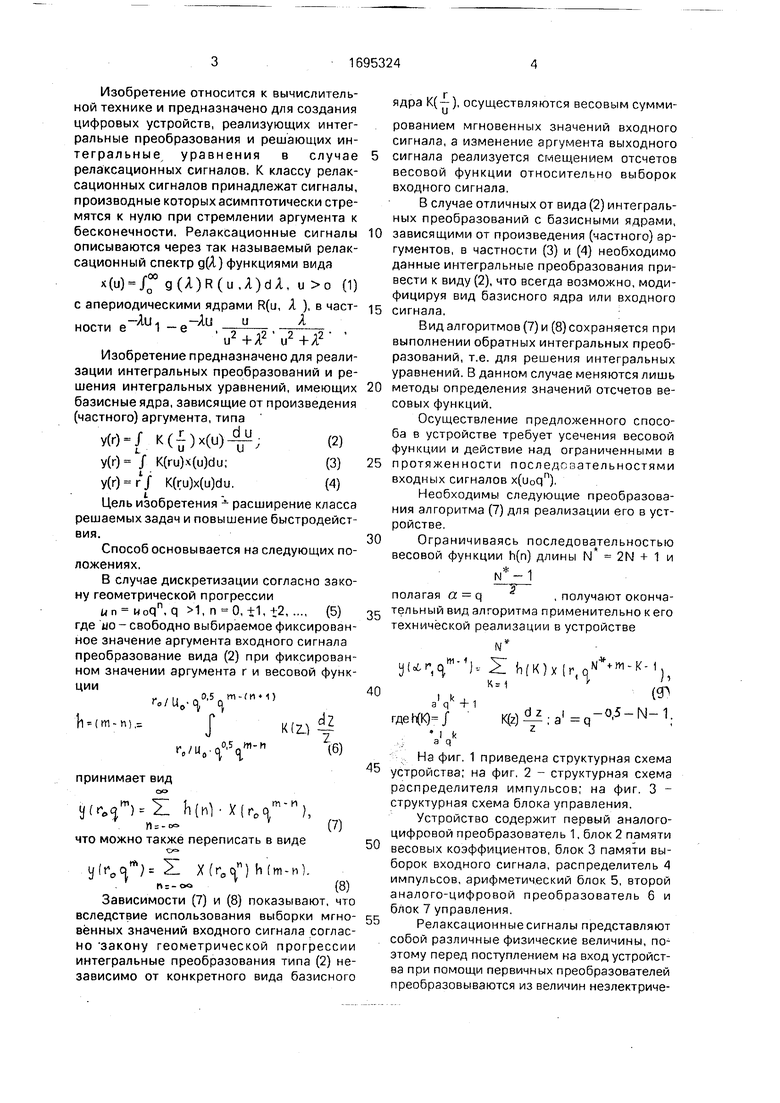

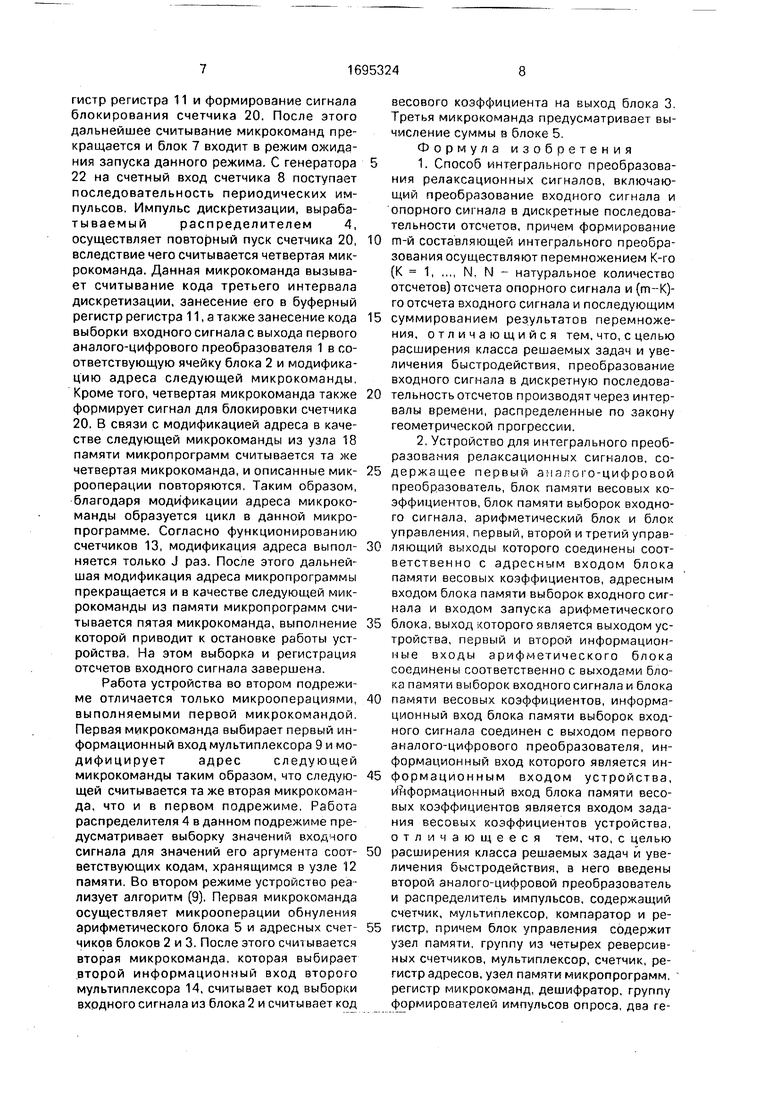

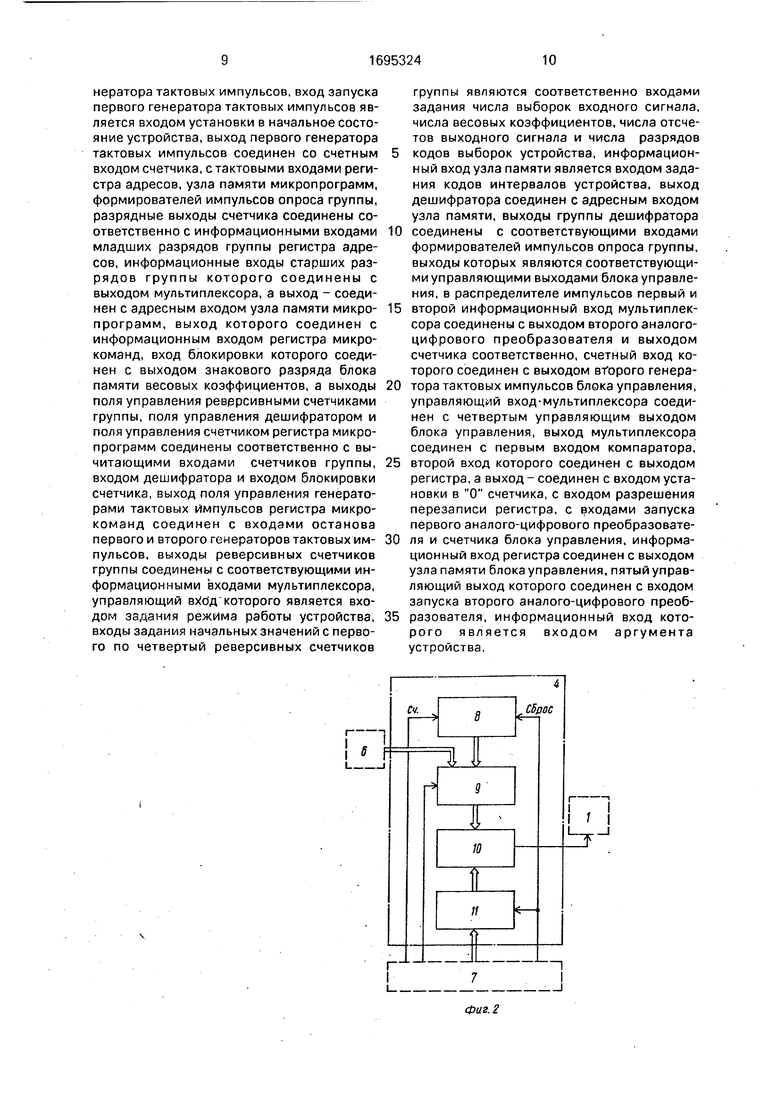

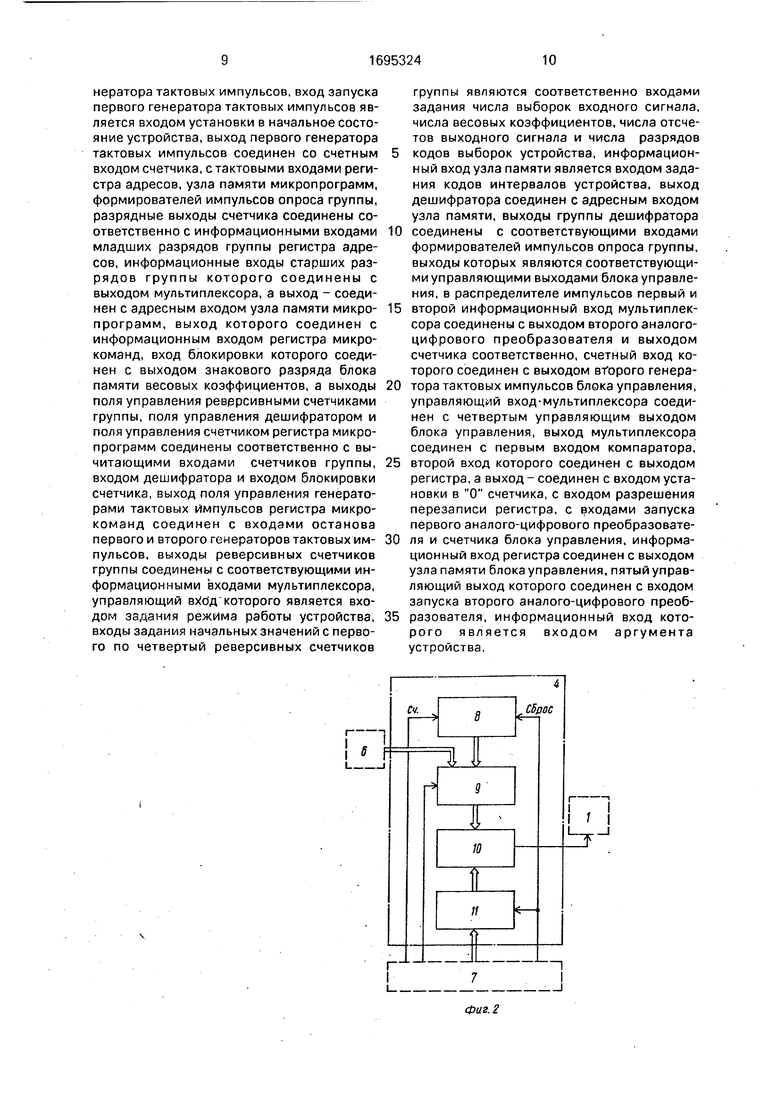

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема распределителя импульсов; на фиг. 3 - структурная схема блока управления.

Устройство содержит первый аналого- цифровой преобразователь 1,блок 2 памяти весовых коэффициентов, блок 3 памяти выборок входного сигнала, распределитель 4 импульсов, арифметический блок 5, второй аналого-цифровой преобразователь 6 и блок 7 управления.

Релаксационные сигналы представляют собой различные физические величины, поэтому перед поступлением на вход устройства при помощи первичных преобразователей преобразовываются из величин неэлектрического характера в электрическое напряжение. Кроме того, аргументом релаксационных сигналов для многих задач не является время, В таких случаях физические величины аргументов релаксационных сигналов при помощи первичных преобразователей преобразовываются в пропорциональные им электрические напряжения и подаются на соответствующий вход устройства. Если же аргументом преобразовываемого релаксационного сигнала является время, то сигнал на входе U(t) устройства отсутствует.

Распределитель 4 содержит счетчик 8, мультиплексор 9, компаратор 10 и регистр 11, содержащий основной и буферный регистры. Распределитель 4 работает в двух режимах в зависимости от того, является ли аргумент входного сигнала интегрального преобразователя временем или нет.

Если аргументом входного сигнала является время, то под воздействием управляющих сигналов с блока 7 выбирается второй информационный вход мультиплексора 9, т.е. второй вход компаратора 10 соединяется с выходом АЦП.

В исходном состоянии разряды счетчика обнулены, в основной регистр кода интервала дискретизации записан код первого, а в буферный регистр - код второго интервала дискретизации, причем содержимое основного регистра кода интервала дискретизации подается на второй информационный вход компаратора 10.

Работа распределителя начинается с момента подачи на счетный вход счетчика 8 последовательности периодических импульсов, после чего счетчик импульсов начинает их подсчет и, следовательно, с каждым подсчитанным импульсом меняется кодовая комбинация на разрядных выходах счетчика. Подсчет импульсов продолжается до тех пор, пока кодовая комбинация на разрядных выходах счетчика 8 не совпадет с кодом, записанным в основном регистре регистра 11. В случае совпадения кодовых комбинаций компаратор 10 на своем выходе вырабатывает кратковременный импульс. Этот импульс одновременно перезаписывает содержимое буферного регистра в основной регистр и обнуляет счетчик 8, после чего описанная процедура повторяется.

Если аргумент входного сигнала интегрального преобразователя не является временем, то под воздействием управляющих сигналов с блока 7 выбирается первый информационный вход мультиплексора 9.

Блок 7 управления представляет собой управляющий автомат, входное слово которого составляет код операции, тактовые импульсы и информационные сигналы, поступающие с отдельных функциональных узлов устройства, а его выходное слово формиру- 5 ет генерируемые управляющие сигналы. В основу управляющего автомата заложен принцип микропрограммирования.

Блок 7 управления содержит узел памя0 ти 12, группу 13 реверсивных счетчиков, мультиплексор 14, формирователи 15 импульсов опроса, дешифратор 16, регистр 17 микрокоманд, узел 18 памяти микропрограмм, регистр 19 адресов, счетчик 20, гене5 раторы 21 и 22 тактовых импульсов.

Устройство работает следующим образом.

Тактовые импульсы, вырабатываемые генератором 21, считываются счетчиком 20,

0 состояние разрядов которого в каждом тактовом периоде фиксируется в регистре 19. Код адреса, содержащийся в регистре 19 определяет адрес микрокоманды, считываемой из узла 18 памяти. Таким образом, в

5 соответствии с каждым тактовым импульсом согласно адресу в регистр 17 микрокоманд считывается одна микрокоманда. Операционная часть микрокоманд дешифруется в дешифраторе 16. Посредством фор0 мирователей 15 формируются управляющие сигналы, необходимые для выполнения микроопераций, соответствующих данному рабочему такту.

Для определения количества циклов,

5 циклически выполняемым процедурам, в счетчики 13 заносится число выборок входного сигнала J, число весовых коэффициентов N , число отсчетов выходного сигнала М и число разрядов кодов выборок входного

0 сигнала Ь.

Устройство работает в двух режимах:- выборка и регистрация отсчетов входного сигнала и вычисление отсчетов выходного сигнала требуемого интегрального преоб5 разования. Первый режим работы, кроме того, имеет два подрежима в зависимости от того, является ли аргумент входного сигнала интегрального преобразователя временем или нет.

0Рассмотрим функционирование устройства в первом подрежиме первого режима работы. Первая микрокоманда выбирает второй информационный вход мультиплексора 9, После этого считывается вторая мик5 рокоманда, которая реализует микрооперации считывания кода первого интервала дискретизации из узла 12 памяти и занесение данного кода в основной ре-, гистр 11. Далее считывается третья микрокоманда, осуществляющая считывание кода второго интервала дискретизации с последующим занесением его в буферный регистр регистра 11 и формирование сигнала блокирования счетчика 20. После этого дальнейшее считывание микрокоманд прекращается и блок 7 входит в режим ожидания запуска данного режима. С генератора 22 на счетный вход счетчика 8 поступает последовательность периодических импульсов. Импульс дискретизации, вырабатываемый распределителем 4, осуществляет повторный пуск счетчика 20, вследствие чего считывается четвертая микрокоманда. Данная микрокоманда вызывает считывание кода третьего интервала дискретизации, занесение его в буферный регистр регистра 11, а также занесение кода выборки входного сигнала с выхода первого аналого-цифрового преобразователя 1 в соответствующую ячейку блока 2 и модификацию адреса следующей микрокоманды. Кроме того, четвертая микрокоманда также формирует сигнал для блокировки счетчика 20. В связи с модификацией адреса в качестве следующей микрокоманды из узла 18 памяти микропрограмм считывается та же четвертая микрокоманда, и описанные микрооперации повторяются, Таким образом, благодаря модификации адреса микрокоманды образуется цикл в данной микропрограмме. Согласно функционированию счетчиков 13, модификация адреса выполняется только J раз. После этого дальнейшая модификация адреса микропрограммы прекращается и в качестве следующей микрокоманды из памяти микропрограмм считывается пятая микрокоманда, выполнение которой приводит к остановке работы устройства, На этом выборка и регистрация отсчетов входного сигнала завершена.

Работа устройства во втором подрежиме отличается только микрооперациями, выполняемыми первой микрокомандой. Первая микрокоманда выбирает первый информационный вход мультиплексора 9 и мо- дифицирует адрес следующей микрокоманды таким образом, что следующей считывается та же вторая микрокоманда, что и в первом подрежиме, Работа распределителя 4 в данном подрежиме предусматривает выборку значений входного сигнала для значений его аргумента соответствующих кодам, хранящимся в узле 12 памяти. Во втором режиме устройство реализует алгоритм (9). Первая микрокоманда осуществляет микрооперации обнуления арифметического блока 5 и адресных счетчиков блоков 2 и 3. После этого считывается вторая микрокоманда, которая выбирает второй информационный вход второго мультиплексора 14, считывает код выборки входного сигнала из блока 2 и считывает код

весового коэффициента на выход блока 3. Третья микрокоманда предусматривает вычисление суммы в блоке 5.

Формула изобретения

1. Способ интегрального преобразования релаксационных сигналов, включающий преобразование входного сигнала и опорного сигнала в дискретные последовательности отсчетов, причем формирование

0 m-й составляющей интегрального преобразования осуществляют перемножением К-го (К 1, ..,, N. N - натуральное количество отсчетов) отсчета опорного сигнала и (т-К)- го отсчета входного сигнала и последующим

5 суммированием результатов перемножения, отличающийся тем, что, с целью расширения класса решаемых задач и увеличения быстродействия, преобразование входного сигнала в дискретную последова0 тельность отсчетов производят через интервалы времени, распределенные по закону геометрической прогрессии.

2, Устройство для интегрального преобразования релаксационных сигналов, со5 держащее первый аналого-цифровой преобразователь, блок памяти весовых коэффициентов, блок памяти выборок входного сигнала, арифметический блок и блок управления, первый, второй и третий управ0 ляющий выходы которого соединены соответственно с адресным входом блока памяти весовых коэффициентов, адресным входом блока памяти выборок входного сигнала и входом запуска арифметического

5 блока, выход которого является выходом устройства, первый и второй информационные входы арифметического блока соединены соответственно с выходами блока памяти выборок входного сигнала и блока

0 памяти весовых коэффициентов, информационный вход блока памяти выборок входного сигнала соединен с выходом первого аналого-цифрового преобразователя, информационный вход которого является ин5 формационным входом устройства, информационный вход блока памяти весовых коэффициентов является входом задания весовых коэффициентов устройства, отличающееся тем, что, с целью

0 расширения класса решаемых задач и увеличения быстродействия, в него введены второй аналого-цифровой преобразователь и распределитель импульсов, содержащий счетчик, мультиплексор, компаратор и ре5 гистр, причем блок управления содержит узел памяти, группу из четырех реверсивных счетчиков, мультиплексор, счетчик, регистр адресов, узел памяти микропрограмм, регистр микрокоманд, дешифратор, группу формирователей импульсов опроса, два генератора тактовых импульсов, вход запуска первого генератора тактовых импульсов является входом установки в начальное состояние устройства, выход первого генератора тактовых импульсов соединен со счетным входом счетчика, с тактовыми входами регистра адресов, узла памяти микропрограмм, формирователей импульсов опроса группы, разрядные выходы счетчика соединены соответственно с информационными входами младших разрядов группы регистра адресов, информационные входы старших разрядов группы которого соединены с выходом мультиплексора, а выход - соединен с адресным входом узла памяти микропрограмм, выход которого соединен с информационным входом регистра микрокоманд, вход блокировки которого соединен с выходом знакового разряда блока памяти весовых коэффициентов, а выходы поля управления реверсивными счетчиками группы, поля управления дешифратором и поля управления счетчиком регистра микропрограмм соединены соответственно с вычитающими входами счетчиков группы, входом дешифратора и входом блокировки счетчика, выход поля управления генераторами тактовых импульсов регистра микрокоманд соединен с входами останова первого и второго генераторов тактовых импульсов, выходы реверсивных счетчиков группы соединены с соответствующими информационными входами мультиплексора, управляющий вХбд которого является входом задания режима работы устройства, входы задания начальных значений с первого по четвертый реверсивных счетчиков

группы являются соответственно входами задания числа выборок входного сигнала, числа весовых коэффициентов, числа отсчетов выходного сигнала и числа разрядов 5 кодов выборок устройства, информационный вход узла памяти является входом задания кодов интервалов устройства, выход дешифратора соединен с адресным входом узла памяти, выходы группы дешифратора

0 соединены с соответствующими входами формирователей импульсов опроса группы, выходы которых являются соответствующими управляющими выходами блока управления, в распределителе импульсов первый и

5 второй информационный вход мультиплексора соединены с выходом второго аналого- цифрового преобразователя и выходом счетчика соответственно, счетный вход которого соединен с выходом второго генера0 тора тактовых импульсов блока управления, управляющий вход-мультиплексора соединен с четвертым управляющим выходом блока управления, выход мультиплексора соединен с первым входом компаратора,

5 второй вход которого соединен с выходом регистра, а выход - соединен с входом установки в О счетчика, с входом разрешения перезаписи регистра, с входами запуска первого аналого-цифрового преобразовате0 ля и счетчика блока управления, информационный вход регистра соединен с выходом узла памяти блока управления, пятыйуправ- ляющий выход которого соединен с входом запуска второго аналого-цифрового преоб5 разователя, информационный вход которого является входом аргумента устройства.

Кодь/Сигналь/Гакто8б/е

мтербалоД (/правления сишр. имлулбСб/

L±.

1

. . .

Л

А . . .

1

v27/7

15

11

L±.

1

v27/7 / T/r

ZZ

регс/слтр.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

Изобретение относится к вычислительной технике и позволяет осуществлять интегральные преобразования и решать интегральные уравнения с ядрами, зависящими от произведения (частного) аргументов в случае релаксационных входных сигналов. Цель изобретения - расширение класса решаемых задач и повышение быстродействия. Способ реализуется путем выборки и весового суммирования мгновенных значений входного сигнала для дискретных значений аргумента, распределенных согласно закону геометрической прогрессии, при этом изменение аргумента выходного сигнала осуществляется смещением отсчетов весовой функции относительно выборок входного сигнала. Устройство, осуществляющее способ, содержит блок 2 памяти весовых коэффициентов, два аналого-цифровых преобразователя (АЦП) 1. 6, блок 3 памяти выборок входного сигнала, распределитель 4 импульсов, арифметический блок 5. блок 7 управления. Выборка мгновенных значений входного сигнала реализуется в устройстве при помощи распределителя импульсов, который осуществляет распределение во времени периодической последовательности тактовых импульсов согласно заданному закону. Входной сигнал подается на вход первого АЦП, второй АЦП предназначен для преобразова-. ния аргумента входного сигнала в дискретный эквивалент в случае, если его аргумент не является временем. 2 с.п. ф-лы, 3 ил. сл о чэ сл 00 го N Режим работы

$Коды интервалов э м м в

ЛОЛ

13

I

п

ТЬ

Режим работы

блок

„Ловт. лусх Фиг.З

/7

ОС/770Н06

Лг

0/7 6/76Х

18

-н

If

19

н

т

н

г/

&

„Луск

0/л Р#

| Рабинер Л., Голд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| - М.: Мир, 1978, с | |||

| Станционный указатель направления времени отхода поездов и т.п. | 1925 |

|

SU434A1 |

| Мизин И.А., Матвеев А.А | |||

| Цифровые фильтры | |||

| - М.: Связь, 1979, с | |||

| Приспособление для записи звуковых явлений на светочувствительной поверхности | 1919 |

|

SU101A1 |

Авторы

Даты

1991-11-30—Публикация

1986-09-01—Подача