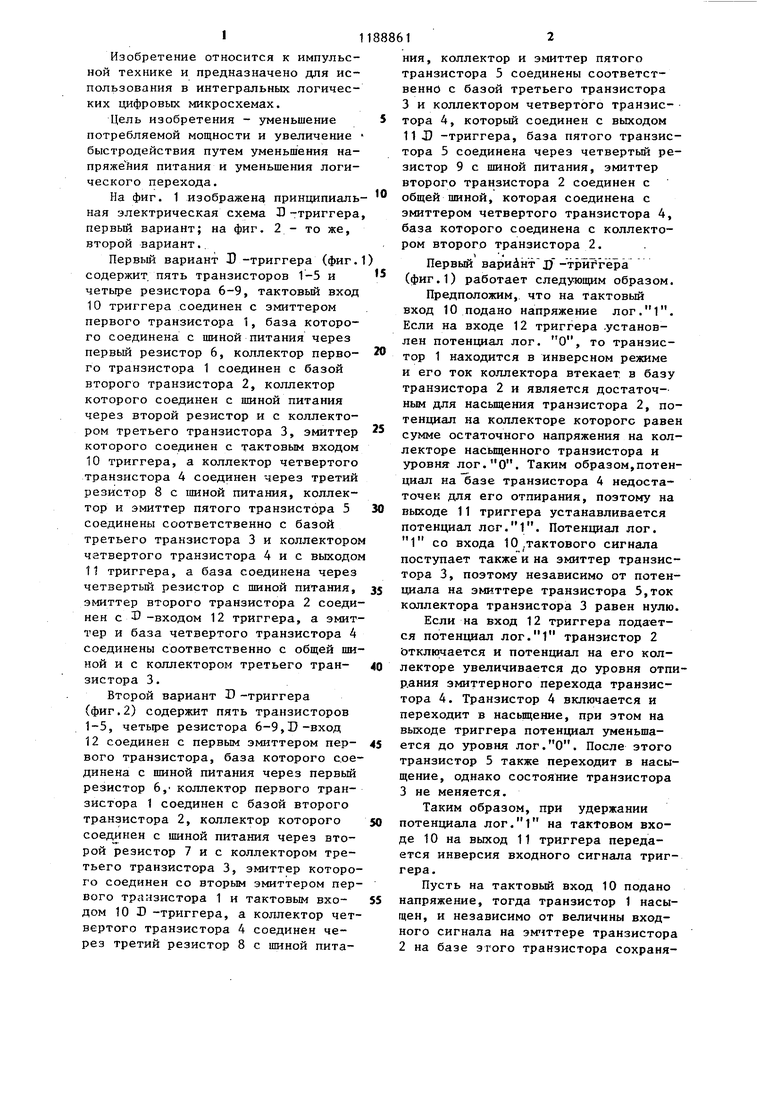

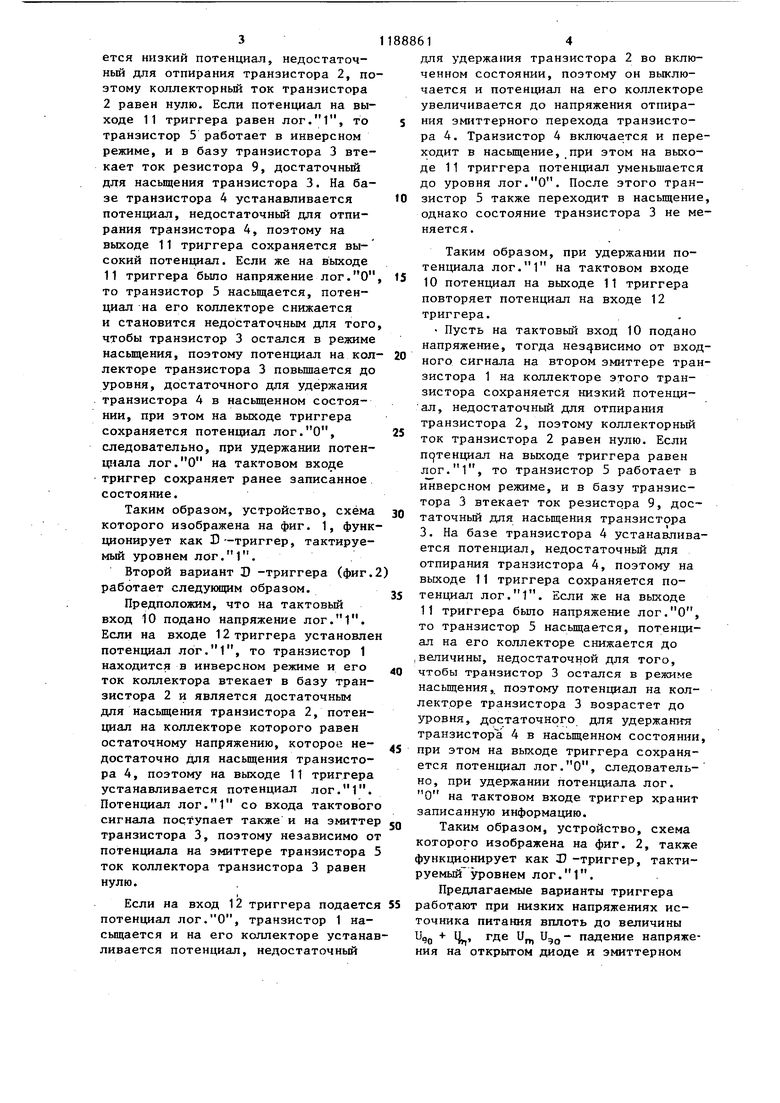

Изобретение относится к импульсной технике и предназначено для использования в интегральных логических цифровых микросхемах. Цель изобретения - уменьшение потребляемой мощности и увеличение быстродействия путем уменьшения напряжейия питания и уменьшения логического перехода. На фиг. 1 изображена принципиаль ная электрическая схема Л -триггера первый вариант; на фиг. 2 - то же, второй вариант.. Первый вариант D -триггера (фиг. содержит, пять транзисторов 1-5 и четыре резистора 6-9, тактовый вход 10 триггера соединен с эмиттером первого транзистора 1, база которого соединена с шиной питания через первый резистор 6, коллектор первого транзистора 1 соединен с базой второго транзистора 2, коллектор которого соединен с шиной питания через второй резистор и с коллектором третьего транзистора 3, эмиттер которого соединен с тактовым входом 10триггера, а коллектор четвертого транзистора 4 соединен через третий резистор 8 с шиной питания, коллектор и эмиттер пятого транзистора 5 соединены соответственно с базой третьего транзистора 3 и коллекторо четвертого транзистора 4 и с выходо 11триггера, а база соединена через четвертый резистор с шиной питания, э йптер второго транзистора 2 соеди нен с 33 -входом 12 триггера, а эмит тер и база четвертого транзистора 4 соединены соответственно с общей ши ной и с коллектором третьего транзистора 3. Второй вариант D -триггера (фиг.2) содержит пять транзисторов 1-5, четыре резистора 6-9,D -вход 12соединен с первым эмиттером первого транзистора, база которого сое динена с шиной питания через первый резистор 6, коллектор первого транзистора 1 соединен с базой второго транзистора 2, коллектор которого соединен с шиной питания через второй резистор 7 и с коллектором третьего транзистора 3, эмиттер которо го соединен со вторым эмиттером пер вого транзистора 1 и тактовым входом 10 И -триггера, а коллектор чет вертого транзистора 4 соединен через третий резистор 8 с шиной питания, коллектор и эмиттер пятого транзистора 5 соединены соответственно с базой третьего транзистора 3 и коллектором четвертого транзистора 4, который соединен с выходом 11 ЛЗ -триггера, база пятого транзистора 5 соединена через четвертый резистор 9 с шиной питания, эмиттер второго транзистора 2 соединен с общей шиной, которая соединена с эмиттером четвертого транзистора 4, база которого соединена с коллектором второго транзистора 2. 1 . Первый вариант JJ -триггера (фиг.1) работает следующим образом. Предположим, что на тактовьй вход 10 подано напряжение лог.Ч. Если на входе 12 триггера -установлен потенциал лог. О, то транзистор 1 находится в инверсном режиме и его ток коллектора втекает в базу транзистора 2 и является достаточным для насыщения транзистора 2, потенциал на коллекторе которого равен сумме остаточного напряжения на коллекторе насьщенного транзистора и уровня лог.О. Таким образом,потенциал на базе транзистора 4 недостаточен для его отпирания, поэтому на выходе 11 триггера устанавливается потенциал лог.М. Потенциал лог. 1 со входа 10,тактового сигнала поступает также и на эмиттер транзистора 3, поэтому независимо от потенциала на эмиттере транзистора 5,ток коллектора транзистора 3 равен нулю. Если на вход 12 триггера подается потенциал лог.Ч транзистор 2 отключается и потенциал на его коллекторе увеличивается до уровня отпир.ания змиттерного перехода транзистора 4. Транзистор 4 включается и переходит в насыщение, при этом на выходе триггера потенциал уменьшается до уровня лог.О. После этого транзистор 5 также переходит в насыщение, однако состояние транзистора 3 не меняется. Таким образом, при удержании потенциала лог.Ч на тактовом входе 10 на выход 11 триггера передается инверсия входного сигнала триггера. Пусть на тактовый вход 10 подано напряжение, тогда транзистор 1 насыщен, и независимо от величины входного сигнала на эм1ттере транзистора 2 на базе этого транзистора сохраняется низкий потенциал, недостаточный для отпирания транзистора 2, по этому коллекторньш ток транзистора 2 равен нулю. Если потенциал на выходе 11 триггера равен лог.Ч, то транзистор 5 работает в инверсном режиме, и в базу транзистора 3 втекает ток резистора 9, достаточный для насыщения транзистора 3. На базе транзистора 4 устанавливается потенциал, недостаточный для отпирания транзистора 4, поэтому на выходе 11 триггера сохраняется высокий потенциал. Если же на выходе 11 триггера бьшо напряжение лог.О то транзистор 5 насьщается, потенциал на его коллекторе снижается и становится недостаточным для того чтобы транзистор 3 остался в режиме насыщения, поэтому потенциал на кол лекторе транзистора 3 повьшается до уровня, достаточного для удержания транзистора 4 в насьщенном состоянии, при этом на выходе триггера сохраняется потенциал лог.О, следовательно, при удержании потенциала лог.О на тактовом входе триггер сохраняет ранее записанное состояние. Таким образом, устройство, схема которого изображена на фиг. 1, функ ционирует как D -триггер, тактируемый уровнем лог.Ч. Второй вариант D -триггера (фиг. работает следующим образом. Предположим, что на тактовый вход 10 подано напряжение лог.Ч. Если на входе 12 триггера установле потенциал лог.1, то транзистор 1 находится в инверсном режиме и его ток коллектора втекает в базу транзистора 2 и является достаточным для насыще1шя транзистора 2, потенциал на коллекторе которого равен остаточному напряжению, которое недостаточно для насыщения транзистора 4, поэтому на выходе 11 триггера устанавливается потенциал лог.Ч. Потенциал лог.1 со входа тактовог сигнала поступает также и на эмитте транзистора 3, поэтому независимо о потенциала на эмиттере транзистора ток коллектора транзистора 3 равен нулю. Если на вход 12 триггера подаетс потенциал лог.О, транзистор 1 насыщается и на его коллекторе устана ливается потенциал, недостаточный для удержания транзистора 2 во включенном состоянии, поэтому он выключается и потенциал на его коллекторе увеличивается до напряжения отпирания эмиттерного перехода транзистора 4. Транзистор 4 включается и переходит в насыщение, при этом на выходе 11 триггера потенциал уменьшается до уровня лог.О. После этого транзистор 5 также переходит в насыщение, однако состояние транзистора 3 не меняется . Таким образом, при удержании потенциала лог.1 на тактовом входе 10потенциал на выходе 11 триггера повторяет потенциал на входе 12 триггера. Пусть на тактовый вход 10 подано напряжение, тогда независимо от входного сигнала на втором эмиттере транзистора 1 на коллекторе этого транзистора сохраняется низкий потенциал, недостаточный для отпирания транзистора 2, поэтому коллекторный ток транзистора 2 равен нулю. Если П9тенциал на выходе триггера равен лог.1, то транзистор 5 работает в инверсном режиме, и в базу транзистора 3 втекает ток резистора 9, достаточный для насыщения транзистора 3. На базе транзистора 4 устанавливается потенциал, недостаточный для отпирания транзистора 4, поэтому на выходе 11 триггера сохраняется потенциал лог.Ч. Если же на выходе 11триггера было напряжение лог.О, то транзистор 5 насыщается, потенциал на его коллекторе снижается до величины, недостаточной для того, чтобы транзистор 3 остался в режиме насыщения, поэтому потенциал на коллекторе транзистора 3 возрастет до уровня, достаточного для удержания транзистор 4 в насыщенном состоянии, при этом на выходе триггера сохраняется потенциал лог.О, следовательно, при удержании потенциала лог. О на тактовом входе триггер хранит записанную информацию. Таким образом, устройство, схема которого изображена на фиг. 2, также функционирует как 17-триггер, тактируемый уровнем лог . 1 . Предлагаемые варианты триггера работают при низких напряжениях источника питания вплоть до величины Ugg -I- Ц, где и УЭО падение напряжения на открытом диоде и эмиттерном

| название | год | авторы | номер документа |

|---|---|---|---|

| D-триггер | 1985 |

|

SU1332380A1 |

| @ -Триггер | 1984 |

|

SU1188862A1 |

| Триггер | 1989 |

|

SU1690176A1 |

| Триггер | 1989 |

|

SU1691931A1 |

| @ -Триггер | 1984 |

|

SU1174987A1 |

| Триггер с предварительной установкой | 1988 |

|

SU1598125A1 |

| Д-триггер | 1984 |

|

SU1221714A1 |

| Счетный разряд | 1989 |

|

SU1684926A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| Д-триггер | 1980 |

|

SU868982A1 |

1. D-ТРИГГЕР, содержащий четыре транзистора и четыре резистора, тактовый вход D -триггера соединен с эмиттером первого транзистора, база которого соединена с шиной питания через первый резистор, а коллектор соединен с базой второго транзистора, коллектор которого соединен с шиной питания через второй резистор и с коллектором третьего транзистора, эмиттер которого соединен с тактовым входом Э -триггера, коллектор четвертого транзистора соединен через третий резистор с шиной питания, отличающийс я тем, что, с целью уменьшения потребляемой мощности и увеличения быстродействия, в него введен пятый транзистор, коллектор и эмиттер которого соединены соответственно с базой третьего тр;анзистора и коллектором четвертого транзистора, а база соединена через четвертый резистор с шиной питания, эмиттер второго транзистора соединен с D -входом D-триггера, эмиттер и база четвертого транзистора соединены соответственно .с общей шиной и с коллектором третьего транзистора, а коллектор - с выходом Э -триггера. 2.О -триггер, содержащий четыре транзистора и четыре резистора,Dвход D -триггера соединен с первым эмиттером первого транзистора, база которого соединена с шиной питания через первый резистор, коллектор с .базой второго транзистора, коллекс тор которого соединен с шиной пита ния через второй резистор и с коллектором третьего транзистора, эмиттер которого соединен с вторьм эмиттером первого транзистора и тактовым входом D -триггера, коллектор четвертого транзистора соединен через третий резистор с шиной питания, отличающийся тем, что, с целью уменьшения потребляемой мощ00 ности и увеличения быстродействия,ое бд в него введен пятый транзистор,коллектор и эмиттер которого соединены соответственно с базой третьего транзистора и коллектором четвертого транзистора, база пятого транзистора соединена через четвертый резистор с шиной питания, эмиттер второго транзистора соединен с общей шиной, эмиттер и база четвертого транзистора соединены соответственно с общей шиной и с коллектором второго транзистора, а коллектор с выходом -триггера.

| Алексеенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, | |||

| с | |||

| Прибор для определения всасывающей силы почвы | 1921 |

|

SU138A1 |

| Березенко А.И., Корягин Л.Н., Назарьян А.Р | |||

| Микропроцессорные комплекты повышенного быстродействия | |||

| М .: Радио и связь, 1981, с.69, рис.39. | |||

Авторы

Даты

1985-10-30—Публикация

1984-04-19—Подача