Изобретение относится к вычислительной технике и предназначено для использования в интегральных логических микросхемах цифровых ЭВМ.

Целью изобретения является повышение быстродействия и снижение потребляемой мощности.

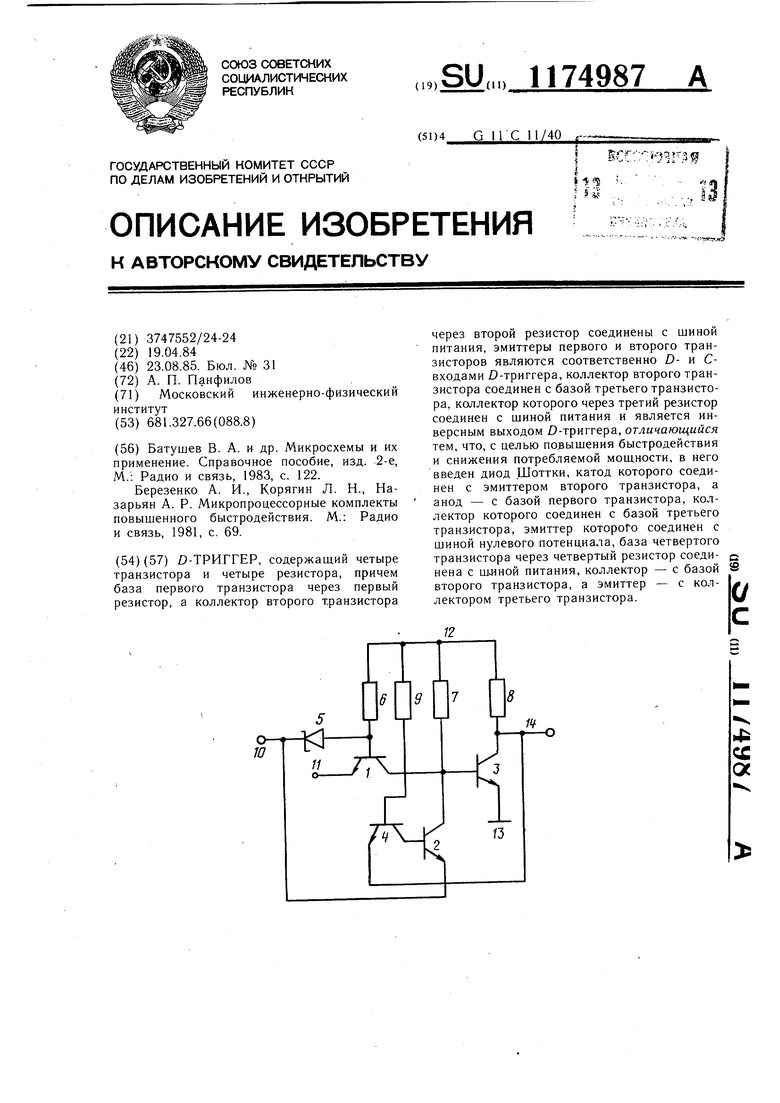

На чертеже изображена принципиальная электрическая схема D-триггера.

D-триггер содержит четыре транзистора 1 -4, диод Шоттки 5 и четыре резистора.6-9. Эмиттер второго транзистора является Свходом 10, а эмиттер первого транзистора- D-входом 11 D-триггера. Одни выводы резисторов 6:-9 соединены с шиной 12 питания, эмиттер третьего транзистора 3 соединен с шиной 13 нулевого потенциала, а его коллектор является инверсным выходом 14 D-триггера.

Триггер работает следующим образом.

Предположим, что на С-вход 10 подано напряжение логической единицы U, тогда диод Шоттки 5 закрыт при любом значении потенциала на входе триггера и ток через него не протекает. Если на D-входе 11 триггера установлен потенциал логической единицы и , то транзистор 1 находится в инверсном режиме и ток его коллектора втекает в базу транзистора 3 и является достаточным для насыщения транзистора 3, потенциал на коллекторе которого, т. е. на инверсном выходе триггера, равен остаточному напряжению U . Потенциал логической единицы и с С-входа 10 поступает также и на эмиттер транзистора 2, поэтому независимо от потенциала на эмиттере транзистора 4 ток коллектора транзистора 2 равен нулю.

Если на D-ВХОД триггера 11 подается потенциал логического нуля U°, транзистор 1 насыщается и на его коллекторе устанавливается потенциал , где UHH - падение напряжения между коллектором и эмиттером насыщенного транзистора. Этот

потенциал недостаточен для удержания транзистора 3 во включенном состоянии, поэтому он выклЕОчается и потенциал на его коллекторе увеличивается до уровня логической единицы. После этого транзистор 4 также переходит в насыщение, однако состояние транзистора 2 не меняется.

Таким образом, при удержании потенциала логической единицы на С-входе 10 на выходе триггера появляется потенциал логической инверсии входного сигнала.

Пусть на С-вход 10 подано напряжение

и°, диод Шоттки открывается и потенциал

на базе транзистора 1 уменьшается до ве- личины , где Ото - напряжбние

на открытом диоде Шоттки, тогда независимо от входного сигнала на эмиттере транзистора 1 на базе этого транзистора сохраняется низкий потенциал , недостаточный для отпирания транзистора 1, поэтому коллекторный ток транзистора 1 равен нулю. Если потенциал на выходе триггера равен и , то транзистор 4 работает в инверсном режиме, и в базу транзистора 2 втекает ток резистора 7, достаточный для насыщения транзистора 2. На базе транзистора 3 устанавливается потенциал 0°+

5 -f-UKH, недостаточный для отпирания транзистора 3, поэтому на выходе триггера сохраняется высокий потенциал U. Если же на выходе триггера было напряжение логического нуля и , то транзистор 4 насыщается, потенциал на его коллекторе снижается до величины , недостаточной для того, чтобы транзистор 2 остался в режиме насыщения, поэтому потенциал на коллекторе транзистора 2 повышается до уровня, достаточного для удержания транзистора 3 в насыщенном состоянии, при этом на выходе триггера сохраняется потенциал логического нуля U°, следовательно, при удержании потенциала логического нуля и° на С-входе триггер сохраняет ранее записанную информацию.

| название | год | авторы | номер документа |

|---|---|---|---|

| D-триггер | 1985 |

|

SU1332380A1 |

| @ -Триггер | 1984 |

|

SU1188862A1 |

| @ -Триггер (его варианты) | 1984 |

|

SU1188861A1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| ТТЛ-элемент | 1985 |

|

SU1274150A1 |

| Счетный триггер | 1980 |

|

SU924835A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

| Элемент памяти | 1981 |

|

SU978328A1 |

/)-ТРИГГЕР, содержащий четыре транзистора и четыре резистора, причем база первого транзистора через первый резистор, а коллектор второго транзистора через второй резистор соединены с шиной питания, эмиттеры первого и второго транзисторов являются соответственно D- и Свходами D-триггера, коллектор второго транзистора соединен с базой третьего транзистора, коллектор которого через третий резистор соединен с шиной питания и является инверсным выходом D-триггера, отличающийся тем, что, с целью повышения быстродействия и снижения потребляемой мощности, в него введен диод Шоттки, катод которого соединен с эмиттером второго транзистора, а анод - с базой первого транзистора, коллектор которого соединен с базой третьего транзистора, эмиттер которого соединен с шиной нулевого потенциала, база четвертого транзистора через четвертый резистор соединена с щ-иной питания, коллектор - с базой второго транзистора, а эмиттер - с коллектором третьего транзистора.

| Батушев В | |||

| А | |||

| и др | |||

| Микросхемы и их применение | |||

| Справочное пособие, изд | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Схема обмотки ротора для пуска в ход индукционного двигателя без помощи реостата, с применением принципа противосоединения обмоток при трогании двигателя с места | 1922 |

|

SU122A1 |

| Березенко А | |||

| И., Корягин Л | |||

| Н., Назарьян А | |||

| Р | |||

| Микропроцессорные комплекты повышенного быстродействия | |||

| М.: Радио и связь, 1981, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

Авторы

Даты

1985-08-23—Публикация

1984-04-19—Подача