jioMeirra И, соединенного выходом с шестым входом первого элемента ИЛИ, пятого элемента ИЛИ подключен к третьему входу третьего элемента ИЛИ и к BTopbiN входам седьмого, восьчЬго и девятого элементов И, соединенных выходами соответственно с седьмым, восьмым и девятым входами

1 190/4

15

первого элемента ШТИ, а выход шестого элемента И.1ТИ подсоединен к второму входу пятого элемента ИЛИ, к четвертому входу четвертого элемента ИЛИ и к второму входу десятого элемента И, соединенного выходом с десятым входом первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1980 |

|

SU944136A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ LDPC-КОДОВ | 2013 |

|

RU2549134C1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1986 |

|

SU1365117A1 |

| Устройство для синхронизации координатных пультов ввода информации | 1982 |

|

SU1045238A1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| Устройство для воспроизведения информации с магнитного носителя | 1981 |

|

SU1014017A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Программируемый коммутатор | 1982 |

|

SU1075410A1 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СБОЯ СИНХРОНИЗМА ДЕКОДИРОВАНИЯ ПРИ ВОСПРОИЗВЕДЕНИИ С НОСИТЕЛЯ ЗАПИСИ, содержащее триггер, подключенный выходом к выходной шине и подсоединенный информационным входом к выходу первого из элементов ИЛИ, соединенного первым и вторым входами с выходами соответственно первого и второго элементов И, входную шину информации, входную шину синхроимпульсов и входную шину импульсов сброса, отличающееся тем, что, с целью повьш1ения достоверности обнаружения сбоя, в него введены регистр сдвига, подсоединенный информационным входом, синхронизирующим входом и входом установки логического нуля соответственно к входной шине информации, к входной шине синхроимпульсов и к входной шине импульсов сброса, коммутатор, выходы которого подключены к первым входам элементов И, детектор длины кодового слова, счетчик и дешифратор, причем входная шина импульсов сброса подключена к входу установки логического нуля триггера, подсоединенного синхронизирующим входом к входной шине синхроимпульсов, соединенной с синхронизирующим входом счетчика и с первым входом детектора длины кодового слова, который подсоединен вторым входом к одному из выходов регистра сдвига, соединенных с входами коммутатора, и подключен выходом к входу установки логического нуля счетчика, соединенного выходами с входами дешифратора, первый выход которого подключен к вторым входам первого и второго элементов И и к первым входам второго и третьего элементов ИЛИ, второй и третий выходы дешифратора подсоединены i соответственно к первому входу четвертого элемента 1ШИ и к второму (Л входу третьего элемента ИЛИ, четвертый и пятый выходы дешифратора соединены соответственно с вторым входом четвертого элемента ИЛИ ц с первым входом пятого элемента ИЛИ, ш&стой выход дешифратора подключен к третьему входу четвертого элемента со о 4;: ИЛИ, седьмой выход дешифратора подсоединен к первому входу шестого элемента ИЛИ и к второму входу третьего элемента И, соединенного выходом с третьим входом первого элеел мента ИЛИ, восьмой выход дешифратора подключен к второму входу шестого элемента ИЛИ и к второму входу второго элемента ИЛИ, соединенного выходом с вторым входом четвертого элемента И, выход которого подсоединен к четвертому входу первого элемента ИЛИ, выход третьего элемента ИЛИ соединен с вторым входом пятого элемента И, подключенного выходом к пятому входу первого элемента ИЛИ, выход четвертого элемента ИЛИ подсоединен к второму входу шестого

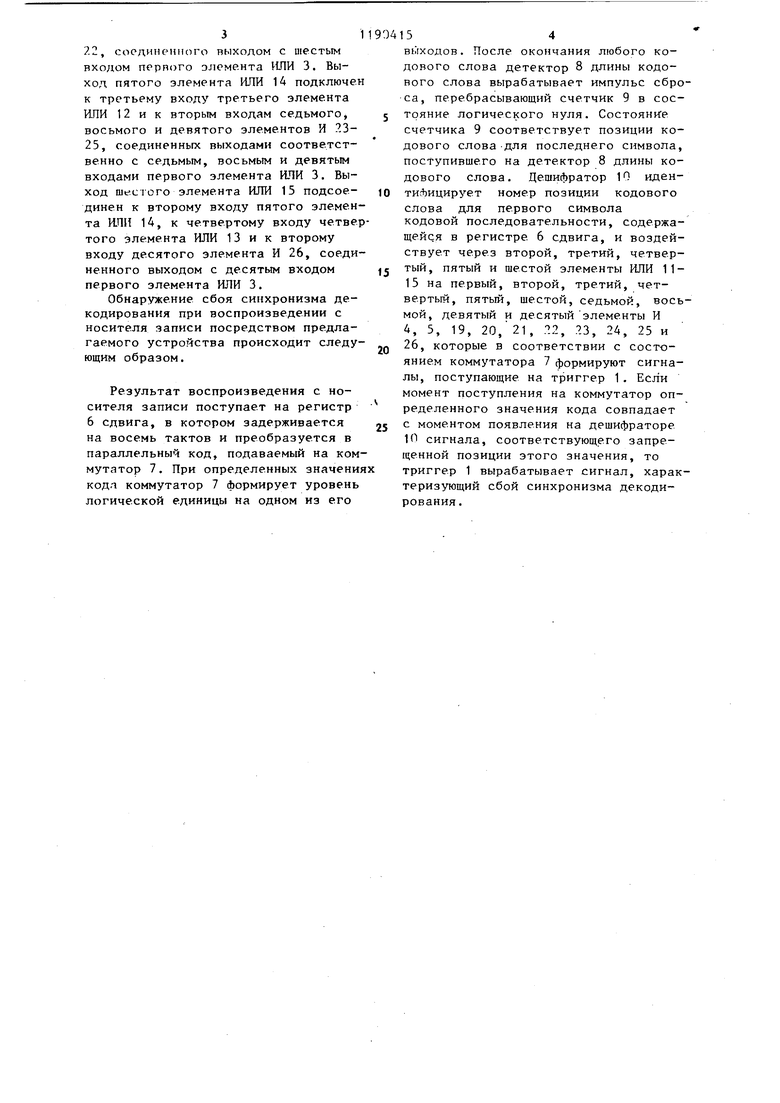

Изобретение относится к области накопления информации, а именно к устройствам для обнаружения сбоя син хронизма декодирования при воспроизведении с носителя записи. Цель изобретения - повышение достоверности обнаружения сбоя синхронизма декодирования при воспроизведе нии с носителя записи. На чертеже изображен один из возможных вариантов предлагаемого устройства для обнаружения сбоя синхронизма декодирования при воспроизведении с носителя записи. Устройство содержит триггер 1, подключенный выходом к выходной шине 2 и подсоединенный информационным входом к выходу первого элемента ИЛИ 3, соединенного первым и вторым входам.i с выходами соответственно первого и второго элементов И 4 и 5, ре гистр 6 сдвига, коммутатор 7, детектор 8 длины кодового слова, счетчик 9, дешифратор 10, и второй, третий. четвертый, пятый и шестой элементы ИЛИ 11 - 15. Регистр 6 сдвига подсоединен информационным входом, синхро низирующим входом и входом установки логического нуля соответственно к входной илтне 16 информации, к входной шине 17 синхроимпульсов и к вход ной шине 18 импульсов сброса. Выходы коммутатора 7 подключены к первым входам первого, второго, третьего, четвертого, nHToio, шестого, седьмо го, восьмого, девятого и десятого эл ментов И 4, 5, 19, 2П, 21, 22, 23, 2 25 и 26. Входная шина 18 импульсов сброса подключена к входу установки логического нуля триггера 1, подсоединенногс С1П1хронизирующим входом к входной шине 17 синхроимпульсов, соединенной с синхронизирующим входом счетчика 9 и с первым входом детектора 8 длины кодового слова .Детектор 8длины кодового слова подсоединен первым входом к одному из выходов регистра 6 сдвига, соединенных со входами коммутатора 7, и подключен выходом к входу установки логического нуля счетчика 9. Выходы счетчика 9соединены с входами дешифратора 10, подключенного первым выходом к вторым входам первого и второго элементов И 4 и 5 и к первым входам второго и третьего элементов ИЛИ 11 и 12. Второй и третий выходы дешифратора 10 подсоединены соответственно к первому входу четвертого элеMetrra ИЛИ 13 и к второму входу третьего элемента ИЛИ 12. Четвертый и пятый выходы дешифратора 10 соединены соответственно с вторым входом четвертого элемента ИЛИ 13 и с первым входом пятого элемента Ш1И 14. Шестой рвыход дешифратора 10 подключен к третьему входу четвертого элемента ИЛИ 13. Седьмой выход дешифратора 10 подсоединен к первому входу шестого элемента ИЛИ 15 и к второму входу третьего элемента И 19, соединенного выходом с третьим входом первого элемента ИЛИ 3. Восьмой выход дешифратора 10 подключен к второму входу шестого элемента 1ПИ 15 и к второму входу второго элемента ИЛИ 11, соединенного выходом с вторым входом четвертого элемента И 20, выход которого подсоединен к четвертому входу первого элемента ИЛИ 3. Выход третьего элемента ИЛИ 12 соединен с вторым входом пятого элемента И 21, подключеннного выходом к пятому входу первог(5 элемента ИЛИ 3. Выход четвертого элемента ИЛИ 13 подсоединен к второму входу шестого элемен-i-a И 3 22, сосдинсм Ис1Го выходом с шестым входом первого элемента ИЛИ 3. Выход пятого элемента ИЛИ 14 подключе к третьему входу третьего элемента ИЛИ 12 и к вторым входам седьмого, восьмого и девятого элементов И 2325, соединенньгх выходами соответственно с седьмым, восьмым и девятым входами первого элемента ИЛИ 3. Выход шесюго элемента ИЛИ 15 подсоединен к второму входу пятого элемен та И.ПИ 14, к четвертому входу четве того элемента ИЛИ 13 и к второму входу десятого элемента И 26, соеди ненного выходом с десятым входом первого элемента ИЛИ 3. Обнаружение сбоя синхронизма декодирования при воспроизведении с носителя записи посредством предлагаемого устройства происходит следу ющим образом. Результат воспроизведения с носителя записи поступает на регистр 6 сдвига, в котором задерживается на восемь тактов и преобразуется в параллельный код, подаваемый на ком мутатор 7. При определенных значени кода коммутатор 7 формирует уровень логической единицы на одном из его 54 выходов. После окончания любого кодового слова детектор 8 длины кодового слова вырабатывает импульс сброса, перебрасывающий счетчик 9 в состояние логического нуля. Состояние счетчика 9 соответствует позиции кодового слова-для последнего символа, поступившего на детектор 8 длины кодового слова. Дешифратор 10 идентиАицирует номер позиции кодового слова для первого символа кодовой последовательности, содержащейся в регистре. 6 сдвига, и воздействует через второй, третий, четвертый, пятый и шестой элементы ИЛИ 1115 на первый, второй, третий, четвертый, пятьй, шестой, седьмой, восьмой, девятый и десятый элементы И 4, 5, 19, 20,21, 22, 23, 24, 25 и 26, которые в соответствии с состоянием коммутатора 7 формируют сигналы, поступающие на триггер 1. Если момент поступления на коммутатор определенного значения кода совпадает с моментом появления на дешифраторе 10 сигнала, соответствующего запрещенной позиции этого значения, то триггер 1 вырабатывает сигнал, характеризующий сбой синхронизма декодирования.

| Устройство для контроля воспроизведенияцифРОВОй иНфОРМАции C НОСиТЕля МАгНиТ-НОй зАпиСи | 1979 |

|

SU834763A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 3414894, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для контроля движения | 1921 |

|

SU1968A1 |

Авторы

Даты

1985-11-07—Публикация

1984-06-28—Подача