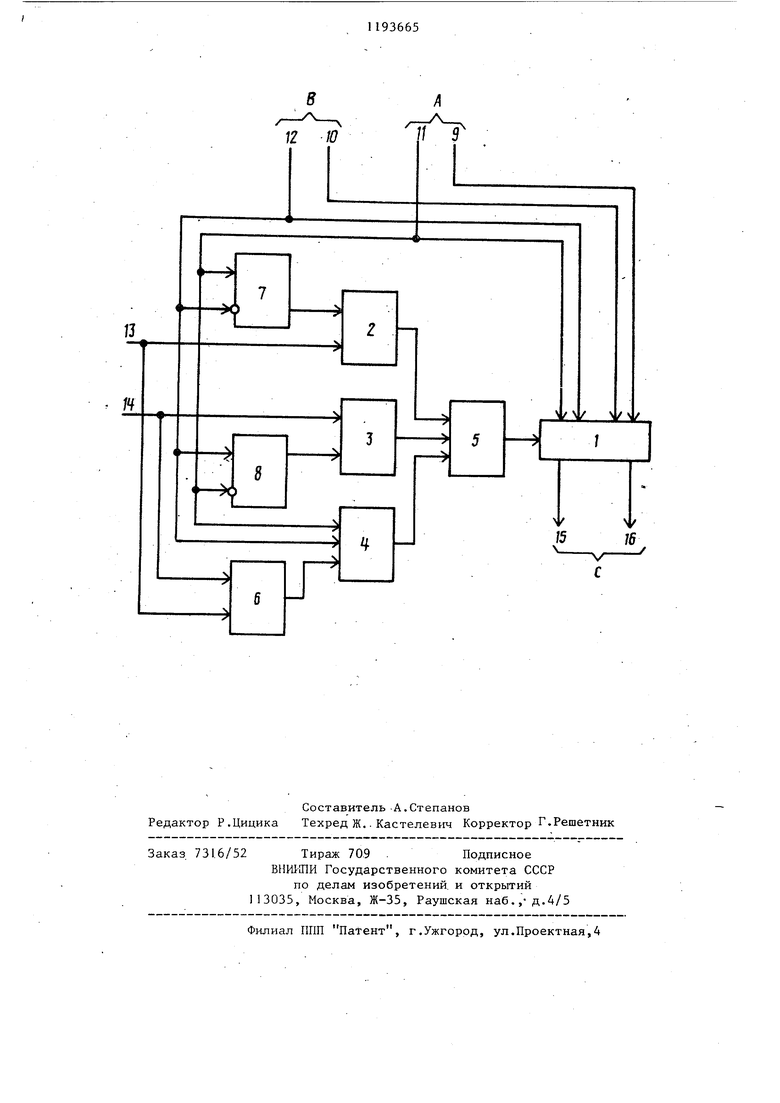

1 Изобретение относится к вычислительной технике и может быть исполь зовано при построении арифметически устройств ЭВМ. Целью изобретения является расши рение области применения устройства путем обеспечения возможности сумми рования чисел как в дополнительном, так и в коде. На чертеже представлена структур ная схема устройства для суммирования двоичных чисел. Устройство содержит параллельный сумматор 1, элементы И 2-4, ИЛИ 5 и 6 и ЗАПРЕТ 7 и 8. Устройство содержит входные числовые шины 9 и 10 слагаемых и входные шины 11 и 12 знаков, а также входы 13 и 14 задания режима и выходную числовую шину 15, выходную шину 16 знака. Устройство для суммирования двоичных чисел работает следуюш;им образом. Числа А и В, поступающие на соот ветствующие входные шины 9,11 и 10,12 устройства, представлены п чи ловыми и двумя знаковыми разрядами, а результат С на шинах 15 и 16 устройства представлен также п числовыми и двумя знаковыми разрядами. При этом числа А и В, поступающее на соответствующие шины 9, 11 и 10,12 устройства, кодируются обратными или дополнительными модифицированными кодами, а результат С на шинах 15 и 16 устройства - только в дополнительном модифицированном коде. Если числа А и В представлены в дополнительных модифицированных кодах, то на входах 13 и 14 задания режима устройства должны быть нулевые сигналы. При этом результат суммирова:ния С также представлен в дополнительном модифицированном коде. Если число А представлено в обратном модифицированном коде, а чис ло -В - в дополнительном модифицированном коде, то на входе 13 задания режима устройства должен быть единичный сигнал, а на входе 14 нулевой сигнал. Если число А отрица 652 тельное, а число В положительное, то на выходе элемента ЗАПРЕТ 7, а следовательно, и на выходах элементов И 2 и ИЛИ 5 будут единичные сигналы, вследствие чего в младший разряд сумматора 1 поступает дополнительная единица. Если числа А и В отрицательные, то на выходе элемента И 4, а следовательно, и на выходе элемента ИЛИ 5 будет единичный сигнал, вследствие чего в младший разряд сумматора 1 также поступает дополнительная единица. Если числа А и В положительные или число А положительное, а число В отрицательное, то на выходах элементов ЗАПРЕТ 7, И2, И4 и ИЛИ 5 будут нулевые сигналы вследствие чего в младший разряд сумматора 1 дополнительная единица не поступает . Результат суммирования С представлен в дополнительном модифицированном коде. Если число А представлено в дополнительном модифицированном коде, а число В - в обратном модифицированном коде, то на входе 14 задания режима устройства должен быть единичный сигнал, а на входе 13 - нулевой сигнал. Если число В отрицательное, а число А положительное, то на выходе элемента ЗАПРЕТИВ, а следовательно, и на выходах элементов И 3 и ИЛИ 5 будут единичные сигналы, вследствие чего в младший разряд сумматора 1 поступает дополнительная единица. Если числа А и В отрицательные, то на выходе элемента И 4, а следовательно, и на выходе элемента ИЛИ 5 будет единичный сигнал, вследствие чего в младший разряд сумматора I также поступает дополнительная едини,ца. Если числа А и В положительные или число В положительное, а число А отрицательное, то на выходах элементов ЗАПРЕТ 8 И 3, И 4 и ИЛИ 5 будут нулевые сигналы, вследствие чего в младший разряд сумматора 1 дополнительная единица не поступает. Результат суммирования С представлен в дополнительном модифицированном коде.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1264164A1 |

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1270757A1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Устройство для суммирования двоичных чисел | 1986 |

|

SU1343409A1 |

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1103223A2 |

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1198511A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для суммирования двоичных чисел | 1982 |

|

SU1022153A1 |

УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ ДВОИЧУЫХ ЧИСЕЛ, содержащее параллельньй- сумматор, разряды первогс числового входа которого соединены с первой входной числовой шиной устройства, разряды второго числового входа - с второй входной чи шовой шиной устройства, разряды первого и второго входов знака параллельного сумматора - с соответствующими входными шинами знака устройства, выходы разрядов и знака параллельного сумматора - соответственно с разрядами выходной числовой шины и выходной шины знака устройства, о тличающееся тем, что, с целью расширения области применения путем обеспечения возможности суммирования чисел как в дополнительном, так и в обратном коде, устройство дополнительно содержит три элемента И, два элемента ИЛИ и два элемента ЗАПРЕТ, пр4}чем первый разряд первой входной шины знака соединен с первым входом первого элемента И, с прямым входом первого элемента ЗАПРЕТ и с инверсным входом второго элемента ЗАПРЕТ, первый разряд второй входной шины знака соединен с вторым входом первого элемента И, с инверсным входом первого элемента ЗАПРЕТ и с прямым входом второго элемента ЗАПРЕТ, СП выходы первого и второго элементов ЗАПРЕТ соединены с первыми входами с соответственно второго и третьего элементов И, вторые входа которых § подключены соответственно к первому и второму входам задания режима устройства и первому и второму вхосо со дам первого элемента ИЛИ, выход которого соединен с третьим входом первого элемента И, выходы первого, а второго и третьего элементов И О) подключены к соответствующим входам ел второго элемента ИЛИ, выход которого соединен с входом переноса младшего разряда параллельного сумматора.

| Соловьев Т.Н | |||

| Арифметические устройства ЭВМ.М: Энергия, 1978, с.89, рис.4-13о( | |||

| Самофалов К.Г., Корнейчук В.И., Тарасенко В.П./Под ред.К.Г.Самофалова | |||

| Электронные цифровые вычислительные машины. | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-11—Подача