ts

1

о

СП

Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности, при реализации арифметических устройств специализированных цифровых вычислительных машин.

Целью изобретения ячляется расширение области применения устройства за счет обеспечения возможности суммирования чисел и представления результата суммирования как в обратном, так и в дополнительном кодах.

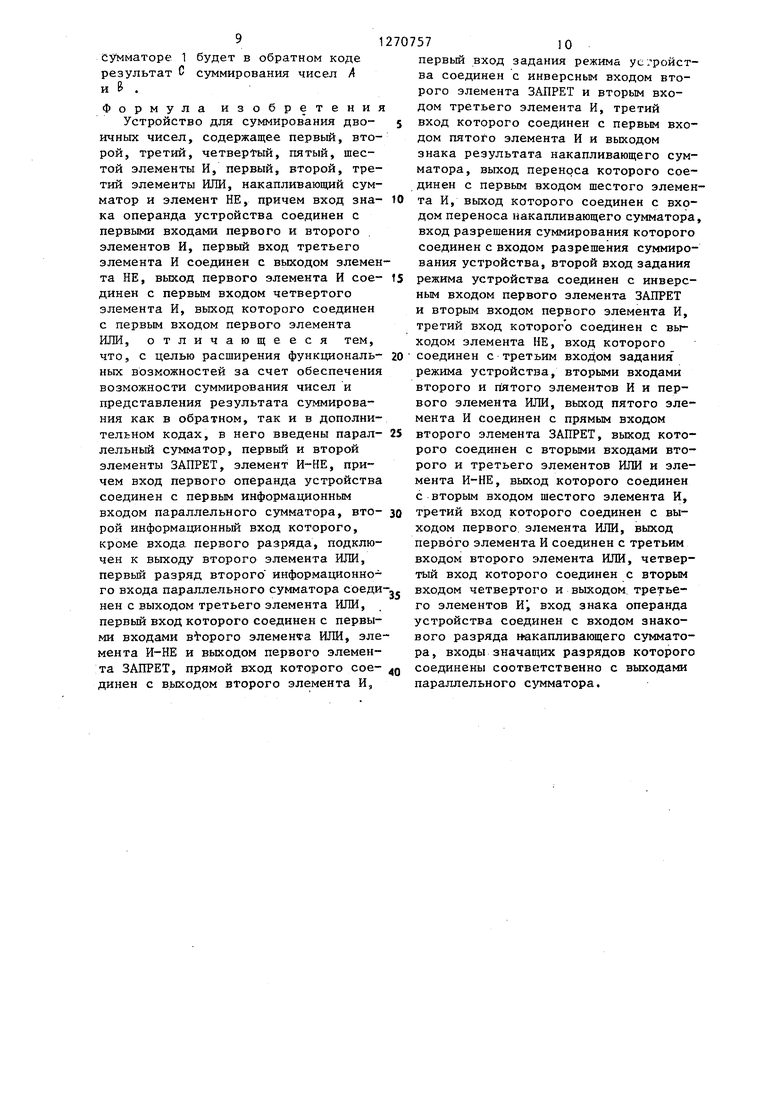

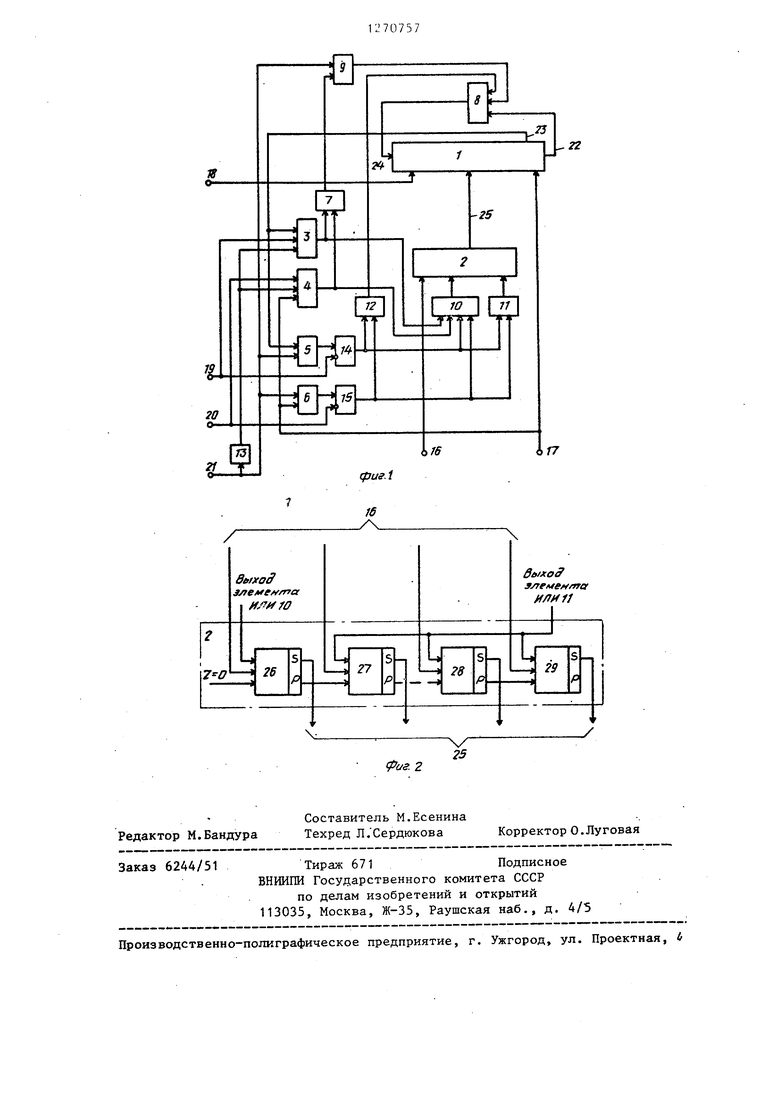

На фиг. 1 представлена блок-схема устройства для суммирования двоичных чисел; на фиг. 2 - блок-схема параллельного сумматора.

Устройство для суммирования двоичных чисел (фиг. 1) содержит накапливающий сумматор 1, параллельный сумматор 2, элементы И 3-8, ЕПИ 9, 10 и 11, И-НЕ 12, НЕ 13, ЗАПРЕТ 14, 15, входную числовую шнну 16 и входную шину 17 знака слагаемого, вход 18 разрешения суммирования, входы 19, 20 и 21 задания режима, выход 22 переноса, выход 23 знака и вход

24переноса младшего разряда накапливающего сумматора 1, выходную шину

25параллельного сумматора 2. Параллельный сумматор 2 содержит

последовательно соединенные сумматоры 26-29.

Устройство для суммирования двоичных чисел работает следующим образом

Число А , поступающее на соответствующие входы 16 и 17 устройства, и число В , хранящееся в накапливающем сумматоре 1, представлены п числовыми и двумя знаковьми разрядами, а результат. суммирования С , образующийся и хранящийся в накап-ливающем сумматоре 1, представлен такжеп числовыми и двумя знаковыми разрядами. При этом, если число / , поступающее на входы 16 и 17, представлено в дополнительном модифиц;ированном коде, то на входе 20 задания режима устройства должен быть нулевой сигнал, а если число Д представлено в обратном модифицированном коде, т(5 на входе 20 задания режима устройства должен быть единичный сигнал. Аналогично, если число & , хранящееся в накапливающем сумматоре 1, представлено в дополнительном модифицированном коде, то на входе 19 задания режима устройства дол;кен быть единичньй сигнал. Если же результат суммирования С должен быть представлен в дополнительном модифицированном коде, то на входе 21 задания режима устройства должен

быть нулевой сигнал, а если результат суммирования С должен быть представлен в обратном модифицированном коде, то на входе 21 задания режима устройства должен быть единичный

сигнал.

Пусть числа Д и 6 представлены в дополнительных модифицированных кодах, а результат С суммирования должен быть представлен в дополнительном модифицированном коде. В этом случае на входах 19, 20 и 21 задания режима устройства будут нулевые сигналы, вследствие чего на выходах элементов И 3-8, ЗАПРЕТ 14

и 15, ИЛИ 9 10 к 11 будут нулевые сигналы, а на выходах элементов И-НЕ 12, НЕ 13 - единичные сигналы. При этом независимо от знаков чисел / и В на выходе параллельного сумматора 2 будет результат суммирования . числовой части числа А с числом 0...0. При поступлении сигнала на вход 18 разрешения суммирования з накапливающем сумматоре 1 будет осуществляться суммирование числа 8 , хранящегося в накапливающем сумматоре 1 , с числом,числовая часть которого сформирована на выходе параллельного сумматора 2, а знак тот же, что и

у числа А . При этом на входе 24 переноса младшего разряда накапливающего сумматора 1 всегда будет нулевой сигнал. В итоге в накапливающем сумматоре 1 будет в дополнительном

коде результат С суммирования чисел / и & .

Пусть числа Д и 6 представлены , в дополнительных модифицированных кодах, а результат С суммирования должен быть представлен в обратном модифицированном коде. В этом случае на входах 19 и 20 задания режима устройства будут нулевые сигналы, а на входе 21 задания режима устройства будет единичный сигнал. При

этом на выходах элементов И 3, 4 и 7, НЕ 13 будут нулевые сигналы, а на выходе элемента ИЛИ 9 будет единичный сигнал.

Если числа Д и 6 положительные, то на выходах элементов И 5, 6, а . следовательно, и на выходах элемен,тов ЗАПРЕТ 14, 15, ИЛИ 10 и 11 будут нулевые сигналы. При этом на .выходе элемента И-НЕ 12 будет единичный сигнал, а на вькоде параллельного сумматора 2 будет результат суммирования числовой части числа А с числом 0...0.

В случае, если числа Д и 8 отрицательные, то на выходах элементов И 5, 6, а следовательно, и на выходах элементов ЗАПРЕТ 14, 15, ИЛИ 10, 11 будут единичные сигналы. При этом на выходе элемента И-НЕ 12 будет нулевой сигнал, а на выходе параллельного сумматора 2 будет результат суммирования числовой части числа А с числом 1... 1.

Если число Д положительное, а число ft отрицательное, то на выходе элемента И 5, а следовательно, и на выходе элемента ЗАПРЕТ 14 будет едияичный сигнал; При этом на выходе параллельного сумматора 2 будет результат суммирования числовой части числа Д с числом 1...1. В этом случае на выходе элемента И-НЕ 12 будет единичный сигнал, так как на выходе элемента И 6, а следовательно, и на выходе элемента ЗАПРЕТ 15 есть нулевой сигнал.

В случае, если число А отрицательное, а число Ь положительное, то на выходе элемента И 6, а следовательно, и на выходе элемента ЗАПРЕТ 15 будет единичный сигнал. При этом на выходе параллельного сум матора 2 будет результат суммирования числовой части числа Д с числом 1... 1 .В этом случае на выходе элемента И-НЕ 12 будет единичньй сигнал,так как на выходе элемента И 5, а следовательно, и на выходе элемента ЗАПРЕТ 14 есть нулевой сигнал.

При поступлении сигнала на вход 18 разрешения суммирования в накапливающем сумматоре 1 будет осуществляться суммирование числа В , хранящегося в накапливающем сумматоре с числом, числовая часть которого сформирована на выходе параллельного сумматора 2, а.знак тот же, что и у числа Д . При этом единичный сигнал на входе 24 переноса младшего разряда накапливающего сумматора 1 есть только в том случае, если на выходе 22 переноса накапливающего сумматора 1 и на выходах элементов ИЛИ 9, И-НЕ 12 есть единичные сигналы. В итоге в накапливающем сумматоре 1 будет в обратном коде результат С суммирования чисел X и В

Пусть число Д представлено в обратном модифицированном коде, число В - в- дополнительном модифицированном коде, а результат С суммирования должен быть сформирован в дополнительном модифицированном коде. В этом случае на входах 19 и 21 задания режима устройства будут нулевые сигналы, а на в.оде 20 задания режима устройства будет единичньй сигнал. При этом на выходах элементов И 5, 6, 3, 7, ЗАПРЕТ 14, 15, ИЛИ 9, 11 будут нулевые сигналы а на выходах элементов И-НЕ 12., НЕ 13 будут единичные сигналы.

Если число А положительное, а число В положительное или отрицателное, то на выходах элементов И 4, ИЛИ 10 также будут нулевые сигналы. При этом на выходе параллельного сумматора 2 будет результат суммирования числовой части числа А с числом О... О.

В случае, если число А отрицателное , а число & положительное или отрицательное, то на выходах элементов И 4, ИЛИ 10 будут единичные сигналы. При этом на выходе параллельного сумматора 2 будет результат суммирования числовой части числа Д с числом 0...01.

При поступлении сигнала на вход 16 разрешения суммирования в накапливающем сумматоре 1 будет осуществляться суммирование числа 8 , хранящегося в накапливающем сумматоре с числом, числовая часть которого сформирована на выходе параллельног сумматора 2, а знак тот же, что и в числе А . При этом на входе 24 переноса младшего разряда накапливающего сумматора 1 всегда будет нулевой сигнал. В итоге в накапливающем сумматоре 1 будет в дополнительном коде результат С суммирования чисел Д и В .

Пусть число А представлено в обратном модифицированном коде, число В - в дополнительном модифицированном коде, а результат С суммирования должен быть сформирован в обратном модифицированном коде. В это случае на входах 20 и 21 задания режима устройства будут единичные сигналы, а на входе 19 будет нулевой сигнал. При этом на выходах элементов И 3, 4, 7, НЕ 13, ЗАПРЕТ 15 будут нулевые сигналы, а на выходах элементов ИЛИ 9, И-FiE 12 будут единичные сигналы. Если же число 6 отрицательное, а число Д положительное или отрицательное, то на выходе элемента И 5, а следовательно, и на выходах элемен тов ЗАПРЕТ 14, ИЛИ 10, 11 будут единичные сигналы. При этом на выходе параллельного сумматора 2 буде результат суммирования числовой час ти числа с числом 1... 1. В случае, если число И положител ное, а число Д положительное или от рицательное, то на выходе элемента И 5, а следовательно, и на выходах элементов ЗАПРЕТ 14, ИЛИ 10, 11, бу дут нулевые сигналы. При этом на выходе параллельного сумматора 2 бу дет результат суммирования числовой части числа с числом 0...0. При поступлении сигнала на вход 18 разрешения суммирования в накапливающем сумматоре 1 будет осуществляться суммирование числа 6 , хра нящегося в накапливающем сумматоре с числом, числовая часть которого сформирована на выходе параллельног сумматора 2, а знак тот же, что и у числа . При этом единичный сигнал на входе 24 переноса младшего разря да накапливающего сумматора 1 есть только в том случае, е:сли на выходе 22 переноса накапливающего сумматора 1 и на элементов ИЛИ 9, И-НЕ 12 есть единичные сигналы. )3 итоге в накапливающем сумматоре 1 б дет в обратном коде результат С сум мирования чисел Д и В . Пусть число А представлено в дополнительном модифицированном коде, число fc - в обратном модифицированном коде, а результат С суммировани должен быть сформирован в дополнительном модифицированном коде. В этом случае на входах 20 и 21 задания режима устройства будут нулевые с;игналы, а на входе 19 задания режи ма устройства будет единичньш сигнал. При этом на выходах элементов И 5, 6, 4 7, ЗАПРЕТ 14, 15, ИЛИ 9, 11 будут нулевые сигналы, а на выходах элементов И-НЕ 12, НЕ 13 будут единичные сигналы. Если число & положительное, а число 4 положительное или отрицател ное, то на выходах элементов И 3, ИЛИ 10 также будут нулевые сигналы. При этом на выходе параллельного сумматора 2 будет результат суммирования числовой .части числа Л с числом 0...0. В случае, если число В отрицательное, а гасло А положительное или отрицательное, то на выходах элементов И З, ИЛИ 10 будут единичные сигналы. При этом на -выходе параллельного сумматора 2 будет результат суммирования числовой части числа А с числом 0...01. При поступлении сигнала на вход 18 разрешения суммирования в накапливающем сумматоре 1 будет осуществляться суммирование числа В , хранящегося в накапливающем сумматоре 1, с числом, числовая часть которого сформирована на выходе параллельного сумматора 2, а знак тот же, что и у числа . При этом на входе 24 переноса младшего разряда накапливающего сумматора 1 всегда будет нулевой сигнал. В итоге в накапливающем сумматоре 1 будет в дополнительном коде результат С суммирования чисел Д и В . Пусть число представлено в дополнительном модифицированном коде, число В - в обратном модифицированном коде, а результат С суммирования до.пжен быть сформирован в обратном модифицированном коде. В этом случае на входах 19 и 21 задания режима устройства будут единичные сигналЬ, а на входе 20 будет нулевой сигнал. При этом на выходах элементов ИЛИ 9, И-НЕ 12-будутединичные сигналы. Если число А отрицательное, а число & положительное или отрицательное, то на выходе элемента И 6, а следовательно, и на выходах элементов ЗАПРЕТ 15, ИЛИ 10, 11 будут единичные сигналы. При этом на выходе параллельного сумматора 2 будет результат суммирования числовой части числа 4 с числом 1... 1. В случае, если число положительное, а число В положительное или отрицательное, то на выходе элемента И 6, а следовательно., и на выходах элементов ЗАПРЕТ 15, ИЛИ 10, 11 будут нулевые сигналы.-При этом на выходе параллельного сумматора 2 будет результат суммирования числовой части числа А с числом 0...0. 7 При поступлении сигнала на вход 18 разрешения суммирования в накапливающем сумматоре 1 будет осуществляться суммирование числа В , хранящегося в накапливающем суммато ре 1 , с числом, числовая часть кото рого сформирована на выходе параллельного сумматора 2, а знак тот же что и у числа /, при этом единичный ,сигнал на входе 24 переноса младшего разряда накапливающего сумматора 1 есть только в том случае, если на выходе 22 переноса накапливающего сумматора 1 и на выходах элементов ИЛИ 9, И-НЕ 12 есть единичные сигналы. В итоге в накапливающем сумматор 2 1 будет в обратном коде результат С суммирования чисел и В . Путь числа и представлены в обратных модифицированных кодах, а результат С суммирования должен быть сформирован в дополнительном модифицированном коде. В этом случае на входах 19 и 20 задания режим устройства будут единичные сигналы, а на входе 21 задания режима устрой ства будет нулевой сигнал. При этом на выходах элементов ЗАПРЕТ 14, 15, ИЛИ 11 будут нулевые сигналы, а на вькодах элементов И-НЕ 12, НЕ 13 будут единичные сигналы. Если числа и Р положительные, выходах элементов И 3, 4, 7, ИЛИ 9, 10 будут нулевые сигналы. При этом на выходе параллельного су матора 2 будет результат суммирования числовой части числа А с числом 0...0. В случае, если числа и Ь отрицательные, то на выходах элементов ИЗ, 4, 7, ИЛИ 9, 10 будут единичные сигналы. При этом на выходе параллельного сумматора 2 будет результат суммирования числовой части числа Л с числом О... 01. Если число А положительное, а число В отрицательное, то на выхода элементов И 3, ИЛИ 10 будут единичные сигналы, а на выходах элементов И 4, , ИЛИ 9 будут нулевые сигналы При этом на выходе параллельного сумматора 2 будет результат суммиро вания числовой части числа А с числом О... 01. в случае, если число Д отрицател ное, а число Ь положительное, то на выходах элементов И 4, ИЛИ 10 будут 57 единичные сигналы, а на выходах элементов ИЗ, 7, ИЛИ 9 будут нулевые сигналы. При этом независимо от знаков чисел А к на выходе параллельного сумматора 2 будет результат суммирования числовой части числа А с числом О... 01. При поступлении сигнала на вход 18 разрешения суммирования в накапливающем сумматоре 1 будет осуществляться суммирование числа 6 , хранящегося в накапливающем сумматоре 1, с числом, числовая часть которого сформирована на выходе параллельного сумматора 2, а знак тот же, что и у числа А . При этом единичный сигнал на входе 24 переноса младшего разряда накапливающего сумматора 1 есть только в том случае, если на выходе 22 переноса накапливающего сумматора 1 и на выходах элементов ИЛИ 9, И-НЕ 12 есть единичные сигналы. В итоге в накапливающем сумматоре 1 будет в дополнительном коде результат С суммирования чисел Л и в . Пусть числи 1 и 6 представлены в обратньпс модифицированных кодах, а результат С суммирования должен быть сформирован в обратном модифицированном коде. В этом случае на входах 19, 20 и 21 задания режима устройства будут единичные сигналы. При этом на выходах элементов ЗАПРЕТ 14, 15, ИЛИ 10, 11, И 3, 4, 7, НЕ 13 будут нулевые сигналы, а на выходах элементов ИЛИ 9, И-НЕ 12 будут единичные сигналы. При этом на выходе параллельного сумматора 2 : будет результат суммирования числовой части числа Л с числом 0...0. При поступлении сигнала на вход 18 разрешения суммирования в накапливающем сумматоре 1 будет осуществляться суммирование числа , хранящегося в накапливающем сумматоре 1, с числом, числовая часть которого сформирована на выходе параллельного сумматора 2, а знак тот же, что. и у числа Л . При этом единичный сигнал на входе 24 переноса младшего разряда накапливающего сумматора 1 есть только в том случае, если на выходе 22 переноса накапливающего сумматора 1 и на выходах элементов ИЛИ 9, И-НЕ 12 есть единичные сигналы. В итоге в накапливающем сумматоре 1 будет в обратном коде результат С суммирования чисел /4 и & . Формула изобретения Устройство для суммирования двоичных чисел, содержащее первый, второй, третий, четвертый, пятый, шестой элементы И, первый, второй, третий элементы ИЛИ, накапливающий сумматор и элемент НЕ, причем вход знака операнда устройства соединен с первыми входами первого и второго элементов И, первый вход третьего элемента И соединен с выходом элемен та НЕ, выход первого элемента И соединен с первым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности суммирования чисел и представления результата суммирования как в обратном, так и в дополнительном кодах, в него введены параллельный сумматор, первый и второй элементы ЗАПРЕТ, элемент И-НЕ, причем вход первого операнда устройства соединен с первым информационным входом параллельного сумматора, второй информационньй вход которого, кроме входа первого разряда, подключен к выходу второго элемента ИЛИ, первый разряд второго информационного входа параллельного сумматора соеди-, нен с выходом третьего элемента ИЛИ, первый вход которого соединен с первыми входами в- орого элемента ИЛИ, элемента И-НЕ и выходом первого элемента ЗАПРЕТ, прямой вход которого сое- о динен с выходом второго элемента И, 1 5710 первый вход задания режима устройства соединен с инверсным входом второго элемента ЗАПРЕТ и вторьм входом третьего элемента И, третий вход которого соединен с первым входом пятого элемента И и выходом знака результата накапливающего сумматора, выход переноса которого соединен с первым входом шестого элемента И, выход которого соединен с входом переноса накапливающего сумматора, вход разрешения суммирования которого соединен с входом разрешения суммирования устройства, второй вход задания режима устройства соединен с инверсным входом первого элемента ЗАПРЕТ и вторым входом первого элемента И, третий вход которого соединен с выходом элемента НЕ, вход которого соединен с третьим вхоДом задания режима устройства, вторыми входами второго и пятого элементов И и первого элемента ИЛИ, выход пятого элемента И соединен с прямым входом второго элемента ЗАПРЕТ, выход которого соединен с вторьми входами второго и третьего элементов ИЛИ и элемента И-НЕ, выход которого соединен с вторым входом шестого элемента И, третий вход которого соединен с выходом первого, элемента ИЛИ, выход первого элемента И соединен с третьим входом второго элемента ИЛИ, четвертый вход которого соединен с вторым входом четвертого и выходом, третьего элементов И, вход знака операнда устройства соединен с входом знакового разряда накапливающего сумматора, входы значащих разрядов которого соединены соответственно с выходами параллельного сумматора.

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1193665A1 |

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1264164A1 |

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Устройство для суммирования двоичных чисел | 1986 |

|

SU1343409A1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1198511A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

. Изобретениеотносится к автоматике и вычислительной технике. Цель изобретения - расширение области применения устройства за счет обеспечения возможности суммирования чисел и представления результата сум- мироиания как в обратном, так и в дополнительном зсодах. Устройство для суммирования двоичных чисел содержит накапливающий сумматор, причем входная шина знака устройства соединена с входом знака накапливающего сумматора, а вход разрешения суммирования устройства соединен с входом разрешения накапливающего сумматора. Новым в устройстве является введение параллельного сумматора, шести элементов И, двух элементов ЗАПРЕТ, трех элементов ИЛИ, одного элемента i И-НЕ и одного элемента НЕ, которые соответствующим образом соединены сл между собой, с входными шинами устс: ройства и с входами и выходами на.капливающего сумматора. 2 ил.

| Устройство для суммирования чисел | 1982 |

|

SU1024907A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для суммирования чисел | 1983 |

|

SU1124288A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-15—Публикация

1985-05-27—Подача