Р зобретение относится к автоматике и вычислительной технике«

Цель изобретения - расширение области применения за счет обеспечения возможности, суммирования чисел обратных кодах и представления результата как в обратном, так и в дополнительном кодах.

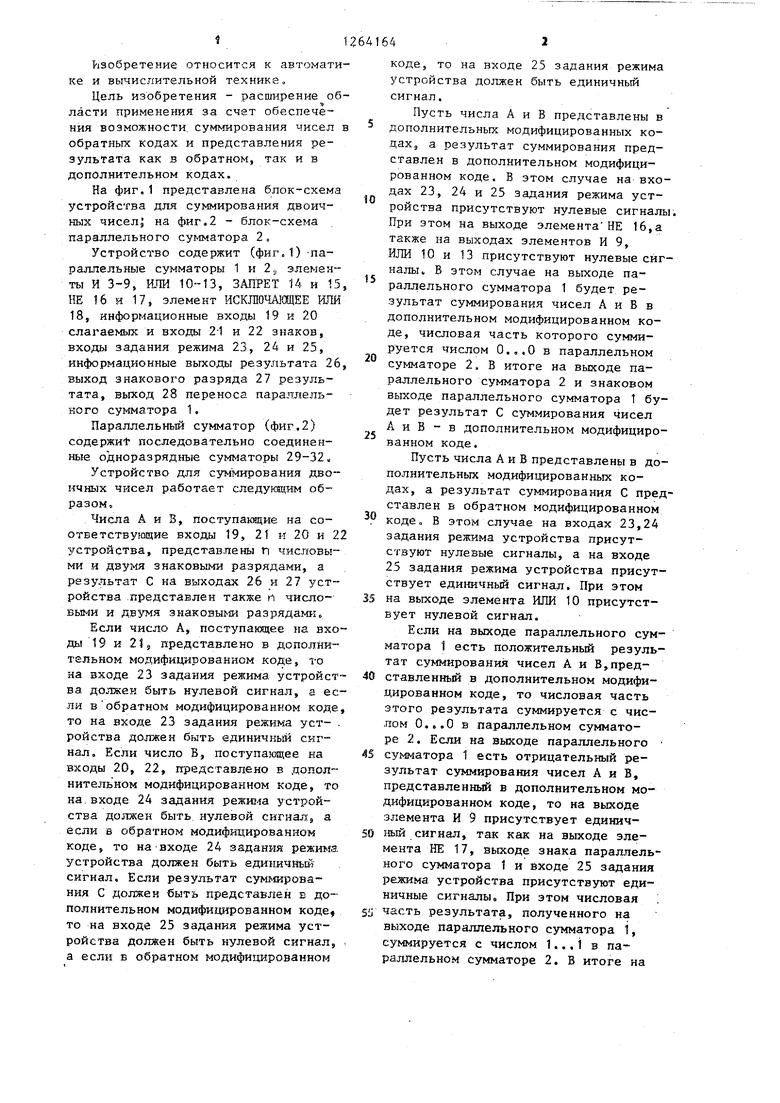

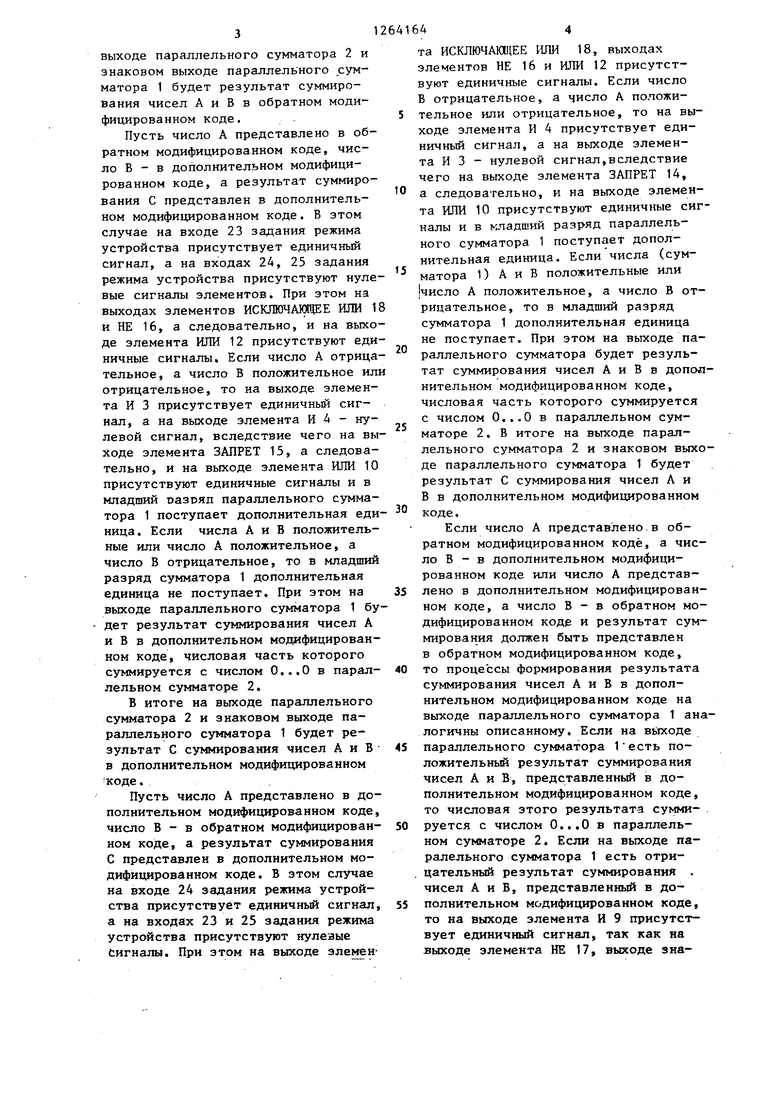

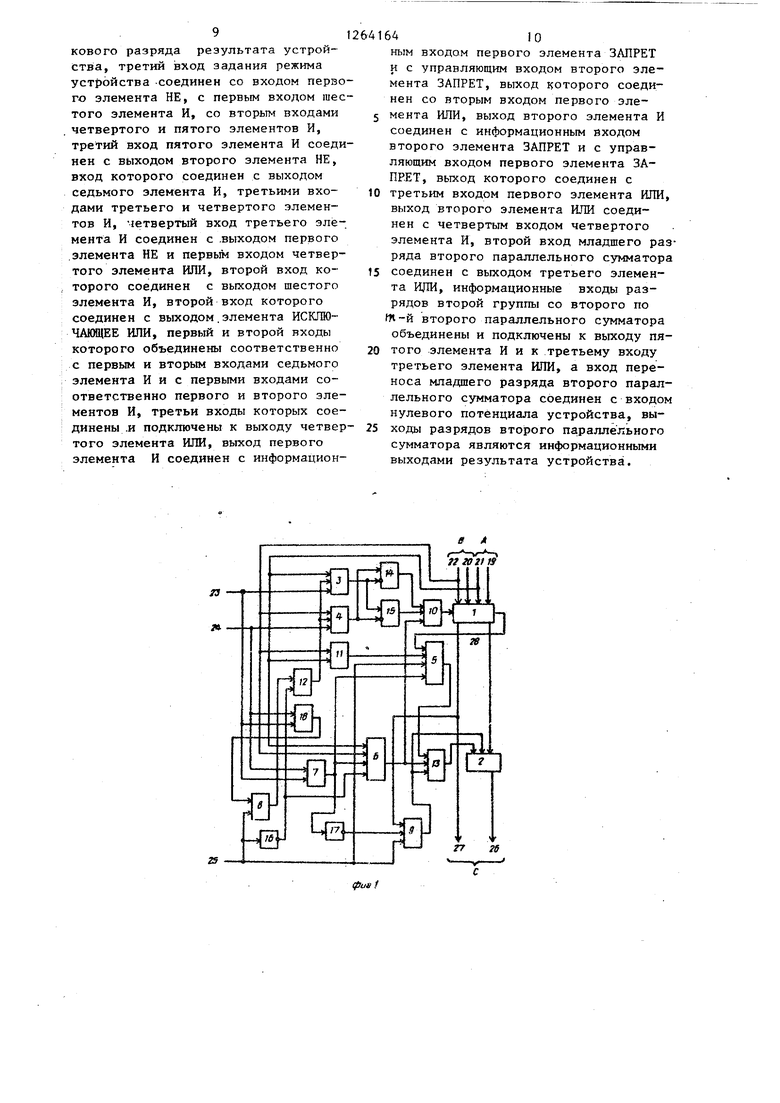

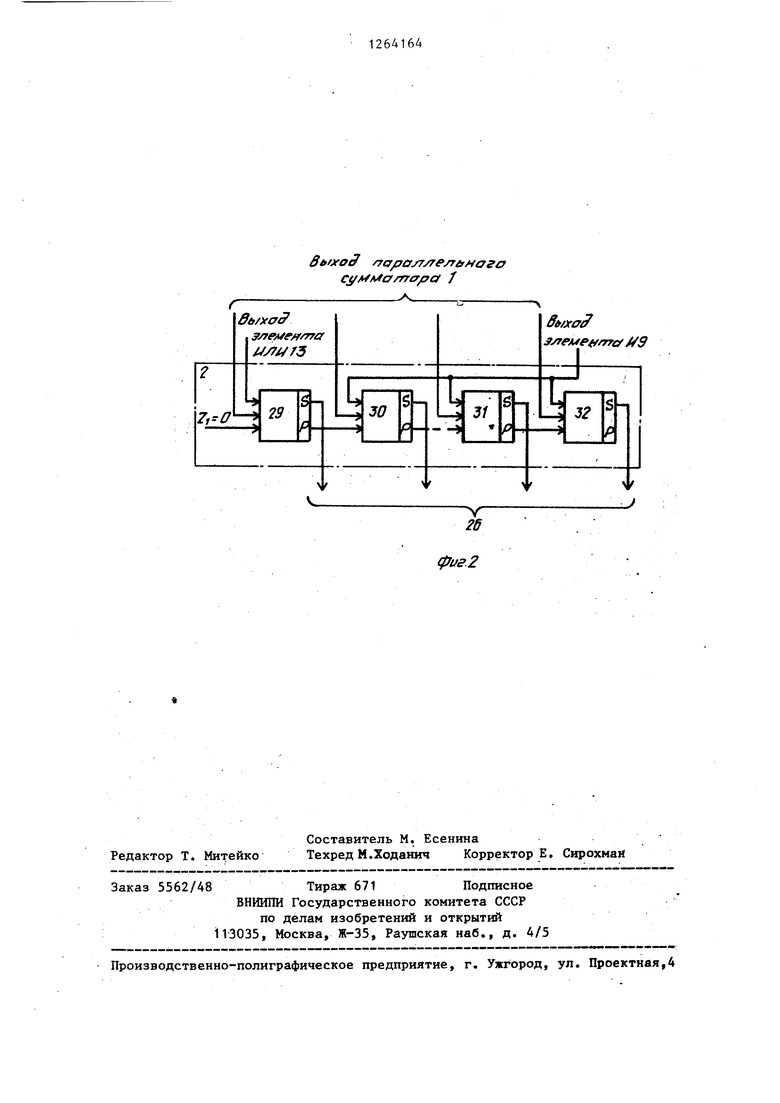

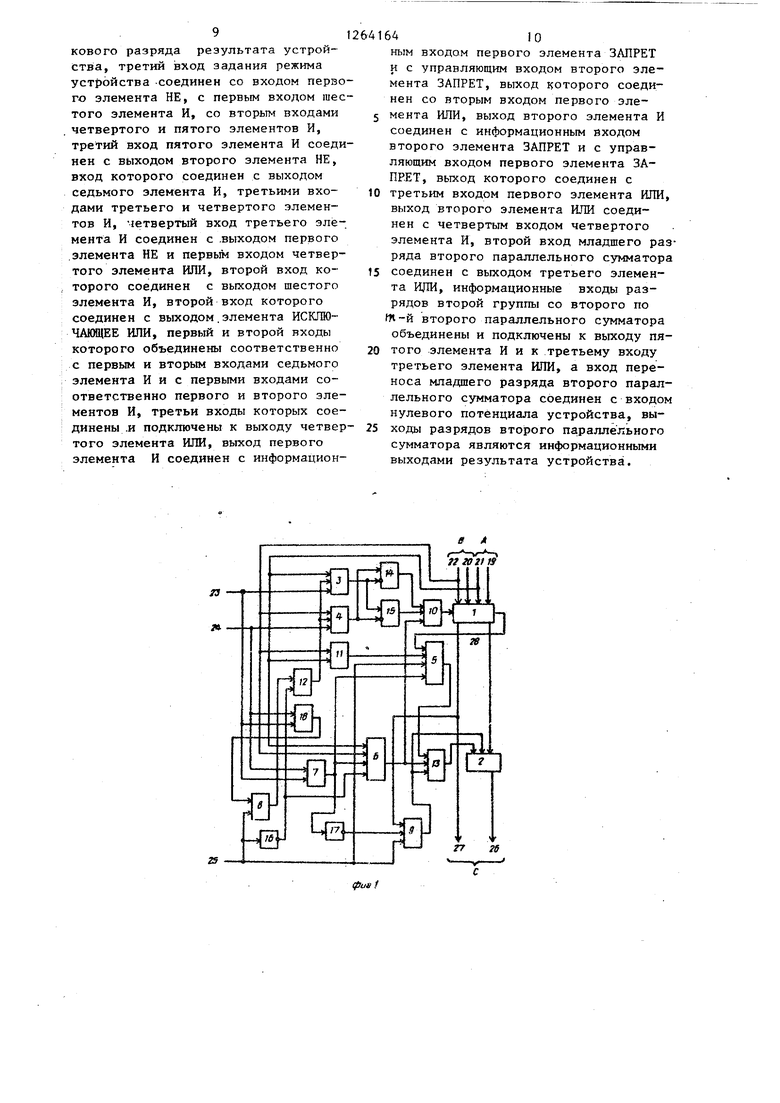

На фиг.1 представлена блок-схема устройства для суммирования двоичных чисел; на фиг,2 - блок-схема параллельного сумматора 2,

Устройство содержит (фиго1) параллельные сумматоры 1 и 2, элементы И 3-9, ИЛИ 10--П, ЗАПРЕТ 14 и 15 НЕ 16 и 17, элемент ИСКЛЮЧАЩЕЕ ИЛИ 18, информационные входы 19 и 20 слагае н 1Х и входы 21 и 22 знаков, входы задания режима 23, 24 и 25, информационные выходы результата 26 выход знакового разряда 27 результата, выход 28 переноса параллельного сумматора 1,

Параллельный сумматор (фиг.2) coдepжиt последовательно соединенные одноразрядные сумматоры 29-32.

Устройство для суммирования двоичных чисел работает следукщим образом,

, Числа А и В, поступакнцие на соответствующие входы 19, 21 и 20 и 22 устройства, представлены ri числовыми и двумя знаковыми разрядами, а результат С на выходах 26 и 27 устройства представлен также h числовыми и знаковыми разрядам -.

Если число А, поступакщее на входы 19 и 21, представлено в дополнительном модифицированном коде, то на входе 23 задания режима устройства должен быть нулевой сигнал, а если вобратном модифицированном коде, то на входе 23 задания режима уст- . ройства должен быть единичньш сигнал. Если число В, поступающее на входы 20, 22, представлено в дополнительном модифицированном коде, то на. входе 24 задания рвжт-ia устройства должен быть, нулевой сигнал5 а если в обратном модифицированном коде, то на-входе 24 задания режима устройства должен быть единичгаш сигнал. Если результат суммирования С должен быть представлен в дополнительном модифицированном коде то на входе 25 задания режима устройства должен быть нулевой сигнал, а если Б обратном кодифицированном

коде, то на входе 25 задания режима устройства должен быть единичный сигнал.

Пусть числа А и В представлены в дополнительных модифицированных коAaxj а результат суммирования представлен в дополнительном модифицированном коде. В этом случае на входах 23, 24 и 25 задания режима устройства присутствуют нулевые сигнал При этом на выходе элементаНЕ 16,а также на выходах элементов И 9, ИЖ 10 и 13 присутствуют нулевые сигналы. В этом случае на выходе параллельного сумматора 1 будет результат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется числом О.,,0 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В - в дополнительном модифицированном коде.

Пусть числа А и В представлены в дополнительных модифицированных кодах, а результат суммирования С представлен в обратном модифицированном коде а В этом случае на входах 23,24 задания режима устройства присутствуют нулевые сигналы, а на входе 25 задания режима устройства присутствует единичный сигнал. При этом на выходе элемента ИЛИ 10 присутствует нулевой сигнал.

Если на выходе параллельного сумматора 1 есть положительный результат суммирований чисел А и В,представленный в дополнительном модифицированном коде, то числовая часть этого результата суммируется с числом 0...0 в параллельном сумматоре 2. Если на выходе параллельного сумматора 1 есть отрицательный результат суммирования чисел А и В, представленный в дополнительном модифицированном коде, то на выходе элемента И 9 присутствует единичный сигнал, так как на выходе элемента НЕ 17, выходе знака параллельного сумматора t и входе 25 задания режима устройства присутствуют единичные сигналы При этом числовая . часть результата, полученного на выходе параллельного сумматора 1, суммируется с числом 1... 1 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат суммирования чисел А и В в обратном модифицированном коде. Пусть число А представлено в обратном модифицированном коде, число В - в дополнительном модифицированном коде, а результат суммирования С представлен в дополнительном модифицированном коде. В этом случае на входе 23 задания режима устройства присутствует единичный сигнал, а на входах 24, 25 задания режима устройства присутствуют нуле вые сигналы элементов. При этом на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 1 и НЕ 16, а следовательно, и на выхо де элемента ИЛИ 12 присутствуют еди ничные сигналы. Если число А отрица тельное, а число В положительное ил отрицательное, то на выходе элемента И 3 присутствует единичньй сигнал, а на выходе элемента И 4 - нулевой сигнал, вследствие чего на вы ходе элемента ЗАПРЕТ 15, а следовательно, и на выходе элемента ИЛИ 10 присутствуют единичные сигналы и в младший оазряд параллельного сумматора 1 поступает дополнительная еди ница. Если числа А и В положительные или число А положительное, а число В отрицательное, то в младший разряд сумматора 1 дополнительная единица не поступает. При этом на выходе параллельного сумматора 1 бу дет результат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется с числом 0...0 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде. Пусть число А представлено в дополнительном модифицированном коде, число В - в обратном модифицированном коде, а результат суммирования С представлен в дополнительном модифицированном коде. В этом случае на входе 24 задания режима устройства присутствует единичньй сигнал, а на входах 23 и 25 задания режима устройства присутствуют нулеаые (;игна:ия. При этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18, выходах элементов НЕ 16 и ИЛИ 12 присутствуют единичные сигналы. Если число В отрицательное, а число А положительное или отрицательное, то на выходе элемента И 4 присутствует единичный сигнал, а на выходе элемента И 3 - нулевой сигнал,вследствие чего на выходе элемента ЗАПРЕТ 14, а следовательно, и на выходе элемента ИЛИ 10 присутствуют единичные сигналы и в младший разряд параллельного сумматора 1 поступает дополнительная единица. Если числа (сумматора 1) А и В положительные или число А положительное, а число В отрицательное, то в младший разряд сумматора 1 дополнительная единица не поступает. При этом на выходе параллельного сумматора будет результат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется с числом 0...0 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде. Если число А представлено.в обратном модифицированном коде, а число В - в дополнительном модифицированном коде или число А представлено в дополнительном модифицированном коде, а число В - в обратном модифицированном коде и результат суммирования должен быть представлен в обратном модифицированном коде, то процессы формирования результата суммирования чисел А и В в дополнительном модифицированном коде на выходе параллельного сумматора 1 аналогичны описанному. Если на вьгходе параллельного сумматора 1есть положительньй результат суммирования чисел А и В, представленный в дополнительном модифицированном коде, то числовая этого результата суммируется с числом 0...0 в параллельном сумматоре 2. Если на выходе паралельного сумматора 1 есть отрицательный результат суммирования . чисел А и В, представленный в дополнительном модифицированном коде, то на выходе элемента И 9 присутствует единичный сигнал, так как на выходе элемента НЕ 17, выходе зна, .5 дса параллельного сумматора 1 и входе 25 задания режима устройства ест единичные сигналы. При этом числовая часть результата, полученного н выходе параллельного сумматора 1, суммируется с числом 1... 1 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и зн ковом выходе параллельного сумматора 1 будет результат С суммироваНИН чисел А и В в обратном модифицированном коде. Пусть числа А и В представлены в обратных модифицированных кодах, а результат суммирования С должен быть представлен в дополнительном модифицированном коде. В этом случае на входах 23 и 24 задания режима устройства присутствуют единичные сигналы, а на входе 25 задания режима устройства - нулевой сигнал. При этом на выходах элементов И 7, НЕ 16, а также и на выходе элемента ИЛИ 12 присутствуют единичные сигналы, а на выходе элемента НЕ 1 а следовательно, и элемента И 9 - н левой сигнал. Если числа А и В положительные, то на выходах элементов ИЛИ 10 и 1 присутствуют нулевые сигналы. При этом на выходе параллельного сумма тора 1 будет результат суммирования чисел А и В, числовая часть кото рого суммируется с число О... О в параллельном сумматоре 2. В итоге выходе параллельного сумматора 2 и знаковом выходе параллельного сумм тора 1 будет результат С суммирова ния чисел в дополнительном модифиц рованном коде.. Если числа А и В отрицательные, то только на выходе элемента И 6, а следовательно, и на выходах элементов ИЛИ 10 и 13 присутствуют ед . ничные сигналы. В.этом случае в младшие разряды параллельных торов 1 и 2 поступают дополнительные единицы. При этом числовая час результата, полученного на выходе параплельного сумматора 1, суммируется с числом 0...01 в параллель ном сумматоре 2, В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 также будет результат С суммирования чисел в дополнительном модифицированном коде. 46 Если число А отрицательное, а число В положительное, то на выходах элементов И 3 и И 4 присутствуют единичньй и нулевой сигналы, вследствие чего на выходе элемента ЗАПРЕТ 15, а следовательно, и на выходе элемента ИЛИ 10 присутствуют единичные сигналы и в младший разряд параллельного сумматора 1 поступает дополнительная единица. При этом на выходе параллельного сумматора 1 будет результат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется с числом G...O в параллельном сумматоре. 2. В итоге на выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде. Если число А положительное,а число В отрицательное, то на выходах элементов И 3 и И 4 присутствуют нулевой и единичньй сигналы, вследствие чего на выходе элемента ЗАПРЕТ 14, а следовательно, и на выходе элемента ИЛИ 10 присутствуют единичные сигналы и в младший разряд параллельного сумматора 1 поступает дополнительная единица. При этом на выходе параллельного сумматора 1 будет результат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется с числом 0..0 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора -1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде. Пусть числа А и В представлены в обратных- модифицированных кодах, а результат суммирования С представлен также в обратном модифицированном коде. В этом случае на входах 23, 24, 25 задания режима устройства присутствуют единичные сигналы. При этом на выходах элементов ИСКПЮЧАКЩЕЕ ИЛИ 18, И 8, НЕ 16, И 6, ИЛИ 12, НЕ 17, И 9 присутствуют нулевые сигналы. Если числа А и В положительные, то на выходах элементов ИЛИ 10 и 13 присутствуют нулевые сигналы. При этом на выходе параллельного сумматора 1 будет результат суммирования чисел А и В, числовая часть которого суммируется с числом 0,..0 в параллельном сумматоре 2. В итоге н выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в обратном моди фицированном коде. Если числа А и В отрицательные, то на выходе 28 переноса параллельного сумматора 1 присутствует единичньй сигнал, вследствие чего на выходе элемента И 5, а следовательно, и на выходе элемента ИЛИ 13 при сутствуют единичные сигналы и в младший разряд параллельного сумматора 2 поступает дополнительная еди ница. При этом числовая часть результата, полученного на выходе параллельного сумматора 1, суммируется с числом О... 01 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в обратном модифицированном коде. Если число А отрицательное, а число В положительное или число А положительное, а число В отрицательное и на выходе переноса 28 параллельного сумматора 1 присутствует единичный сигнал, то на выходах элементов И 5, ИЛИ 13 присутствуют единичные сигналы и в младший разряд параллельного сумматора 2 посту пает дополнительная единица. При этом числовая часть результата, полученного на выходе параллельного сумматора 1, суммируется с числом 0.,.01 в параллельном сумматоре 2. В итоге на выходе параллельного сум матора 2 и знаковом выходе параллельного сумматора . 1 будет результат С суммирования чисел А и В в обратном модифицированном коде. Если число А отрицательное, а число В положительное или число А положительное, а число В отрицательное и на выходе 28 переноса параллельного сумматора 1 присутствуе нулевой сигнал, то на выходах элементов И 5, ИЛИ 13 присутствуют ну левые сигналы. При этом числовая часть результата, полученная на вы ходе параллельного сумматора 1, сум мируется с числом 0,..0 в параллел ном сумматоре 2, В итоге на выходе параллельного сумматора 1 будет ре48зультат С суммирования чисел А и В в обратном модифицированном коде. Формула изобретения Устройство для суммирования двоичных чисел, содержащее первый параллельный сумматор, первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый и второй элементы ЗАПРЕТ, причем входы знаковых разрядов первого -и второго операндов устройства соединены с соответствующими входами знаковых разрядов первого параллельного сумматора, информационные входы первого, и второго операндов устройства соединены соответственно с первой и второй группами входов первого параллельного сумматора, вход переноса младшего разряда которого соединен с выходом первого элемента ШШ, первые входы первого и второго элементов И соединены соответственно с первым и вторым входами задания режима устройства, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности суммирования чисел в обратных кодах и представления результата как в дополнительном так и в обратном кодах, в устройство введены четвертый, пятый, шестой, седьмой элементы И, третий и четвертый элементы ШШ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй элементы НЕ, второй параллельный сумматор, причем входы знаковых разрядов первого и второго операндов соединены со вторыми входами соответственно первого и второго элементов И, соответственно первым и вторым входами второ.го элемента ШШ, первым и вторым входами третьего элемента И, выход которого соединен с первыми входами первого и третьего элементов ШШ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом переноса первого параллельного сумматора, выходы разрядов суммы которого соединены с информационными входами первой группы второго параллельного сумматора, первый вход пятого элемента И соединен с выходом знакового разряда первого параллельного сумматора и с выходом знанового разряда результата устройства, третий зход задания режима устройства -соединен со входом перво го элемента НЕ, с первым входом шее того элемента И, со вторым входами четвертого и пятого элементов И, третий вход пятого элемента И соеди нен с выходом второго элемента НЕ, вход которого соединен с выходом седьмого элемента И, третьими входами третьего и четвертого элементов И, четвертый вход третьего элемента И соединен с .выходом первого .элемента НЕ и первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, второй вход которого соединен с выходом.элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого объединены соответственно с первым и вторым входами седьмого элемента И и с первыми входами соответственно первого и второго элементов И, третьи входы которых соединены .и подключены к выходу четвер того элемента ИЛИ, выход первого элемента И соединен с информацион410ным входом первого элемента ЗАПРЕТ и с управляющим входом второго элемента ЗАПРЕТ, выход которого соединен со вторым входом первого элемента ИЛИ, выход второго элемента И соединен с информационным входом второго элемента ЗАПРЕТ и с управляющим входом первого элемента ЗАПРЕТ, выход которого соединен с третьим входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с четвертым входом четвертого элемента И, второй вход младшего разряда второго параллельного сумматора соединен с выходом третьего элемента ИДИ, информационные входы разрядов второй группы со второго по i-ft второго параллельного сумматора объединены и подключены к выходу пятого элемента И и к третьему входу третьего элемента ИЛИ, а вход переноса младшего разряда второго параллельного сумматора соединен с входом нулевого потенциала устройства, выходы разрядов BTojporo параллельного сумматора являются информационными выходами результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1270757A1 |

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1193665A1 |

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Устройство для суммирования двоичных чисел | 1986 |

|

SU1343409A1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1198511A1 |

| Устройство для сложения чисел | 1984 |

|

SU1218383A1 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1087987A1 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1103223A2 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - расширение области применения за счет обеспечения возможности суммирования чисел в обратных кодах и представления результата суммирования как в дополнительном, так и обратном коде. Устройство для суммирования двоичных чисел содержит первый параллельный сумматор, три элемента И, два элемента ЗАПРЕТ и первый элемент ИЛИ, причем разряды первого числового входа первого параллельного сумматора соединены с первой входной числовой шиной устройства, разряды второго числового входа соединены со второй входной числовой шиной устройства, I разряды первого и второго входов знака первого параллельного сумматора соединены с соответствующими входными шинами знака устройства и первым и вторым входами первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, а выход первого элемента ШШ соединен со входом переноса младшего разряда первого параллельного сумматора, первый вход задания режима устройства соединен с первым входом второго элемента И, второй вход § задания режима устройства соединен (Л с первым входом третьего элемента И, прямой вход элемента ЗАПРЕТ соединен с инверсным входом второго элемента ЗАПРЕТ, а инверсный вход первого элемента ЗАПРЕТ соединен с прямым входом второго элемента ЗАПРЕТ, Новым в устройстве явля1С ется введение второго параллель ного сумматора, четвертого, пятого, шестого и седьмого элементов И, второго, третьего и четвертого эле ментов ИПИ, элемента ИСКЛЮЧАЩЕЕ ИЛИ первого и второго элементов НЕ, которые соответствукярм образом соединены между собой и с соответствующими другими элементами, входами и выходами устройства. 2 ил,

Bbfjfoff 7сг ал/7е ег е7го ct/Aff a/TTffpcf /

вь/ха улеме г/тта //y7///J

29

7,--г7

J

v

26

fpifff.Z

| Самофалов К.Г., Корнейчук В.И., Тарасенко В.П, Электронные цифровые вычислительные машины | |||

| Киев: Вища школа, 1976, с | |||

| Прибор для запора стрелок | 1921 |

|

SU167A1 |

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1193665A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-03-04—Подача