Изобретение предназначено для использования в автоматике и вычислительной технике, в частности при реализации -арифметических устройств специализированных цифровых вычислительных машин.

Цель изобретения - упроЕ1ение устройства.

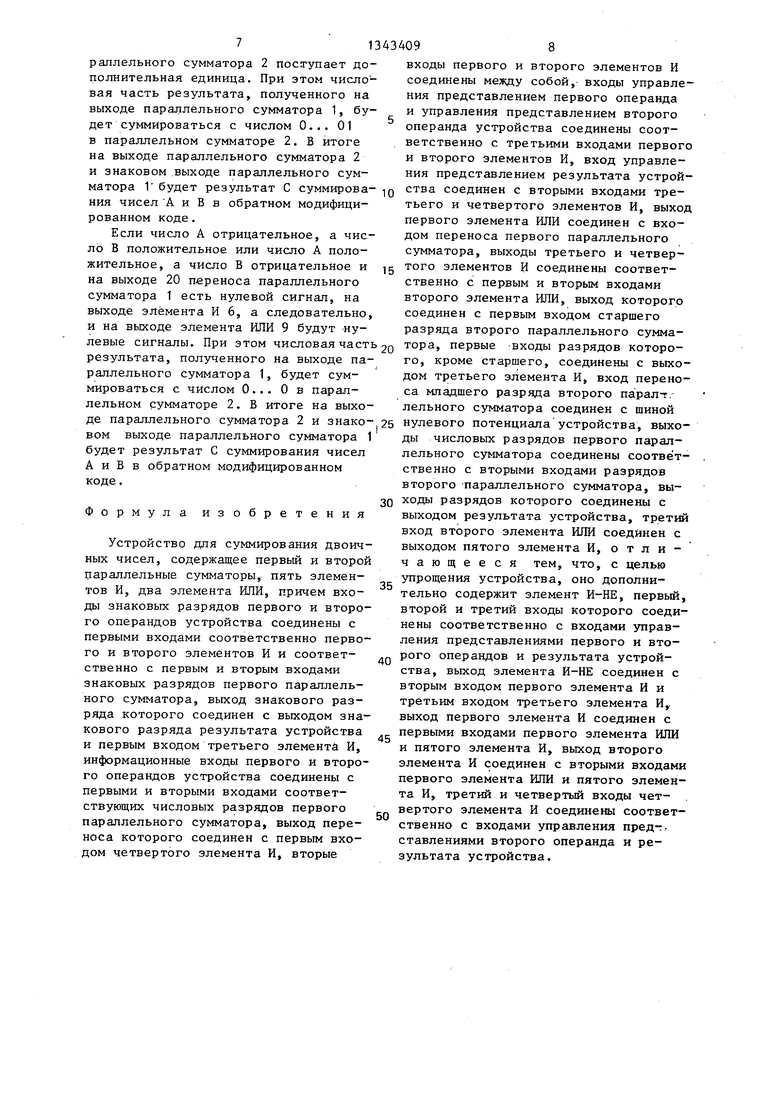

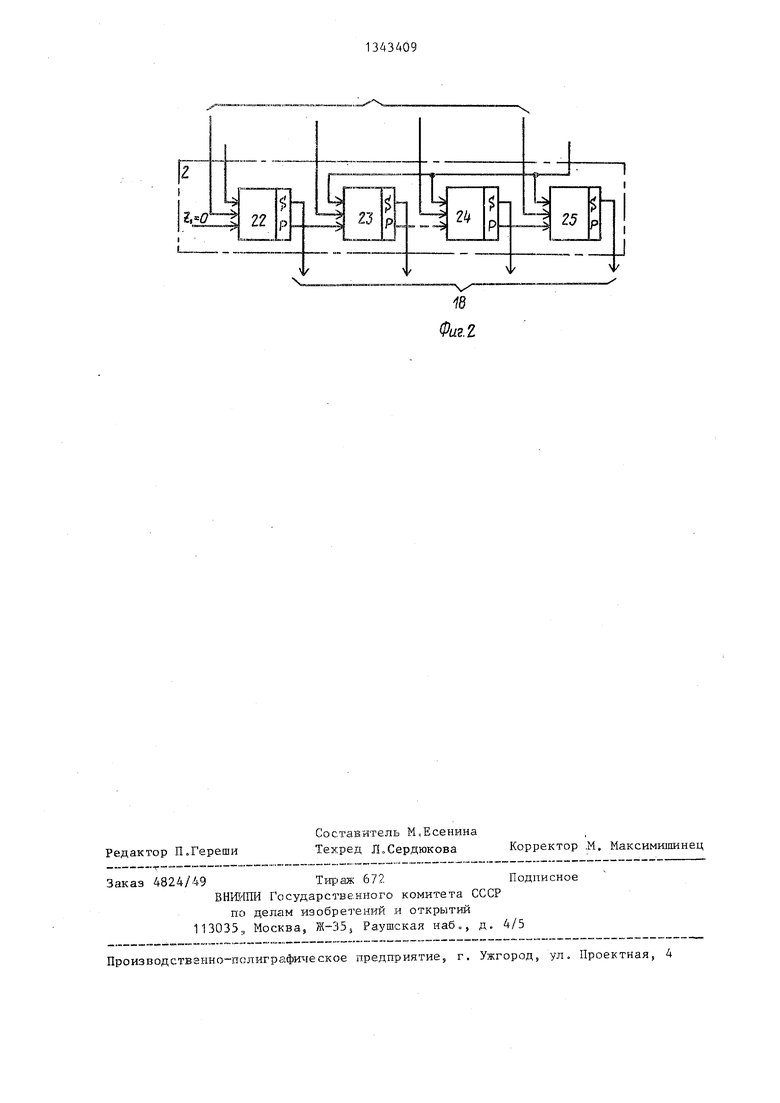

На фиг.1 представлена функциональная схема устройства для суммирования двоичных чисел; на фиг, 2 - функциональная схема параллельного сумматора.

Устройство содержит параллельные сумматоры 1 и 2, элементы И 3-7, ИЛИ 8 и 9, И-НЕ 10, входы 11 и 12 цш рро- вых разрядов слагаемых и выходы 13 и 14 знаковых разрядов слагаемых, вxoд управления представлением первого и второго операндов и результа- та, соответственно, выходы 18 числовых разрядов и выход 19 знакового разряда результата, выход.20 переноса параллельного сумматора 1, вход 21 переноса младшего разряда второго параллельного сумматора 1,

Параллельный сумматор 2 содержит .последовательно соединенные одноразрядные -сумматоры 22-25.

Устройство для суммирования двоичных чисел работает следующим образом

Числа А и БЭ поступающие на соответствующие входы 11., 13 и 12 р 14 устройства, представлены п числовыми и двумя знаковыми разрядами,, а результат С на выходах 18 и 19 устройства представлен п числовыми и двумя знаковыми разрядами. Если число А, поступающее на входы 11 и 13, представлено в дополнительном модифицированном коде, на входе 15 устройства должен быть нулевой сигнал, а если число А представлено в обратном модифицированном коде,, на входе 15 устройства должен быть единичный сигнал.

Аналогично, если число В, поступающее на входы 12 и 14, представлено в дополнительном модифицированном коде, на входе 16 устройства должен быть нулевой сигнал, а если число В представлено в обратном модифицированном коде, на входе 16 устройства должен быть единичный сигнал. Если результат с уммирования С должен быть представлен в дополнительном модифицированном коде, на входе 17 устройства должен быть нулевой.сигнал, а

5

о

5

0

5

0

5

0

5

если результат суммирования С должен быть представлен в обратном модифицированном коде, на входе 17 устройства должен быть единичный сигнал.

Если числа А и В представлены в дополнительных модифицированных кодах, а результат су1чмирования С также должен быть представлен в дополнительном модифицированном коде, на входах 15-17 устройства будут нулевые сигналы. При этом на выходах элементов И 3-7 и ИЛИ 8 и 9 будут нулевые сигналы. В этом случае на выходе параллельного сумматора 1 будет результат суммирования чисел А и В в дополнительном модифицированном коде, числовая часть которого суммируется с числом О ... О в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде.

Если числа А и В представлены в дополнительных модифицированных кодах, а результат суммирования С должен быть представлен в обратном модифицированном коде, на входах 15 и 16 устройства будут нулевые сигналы, а на входе 17 устройства будет единичный сигнал. При этом на выходах элементов И 3-6 и ИЛИ 8 будут нулевые сигналы.

Если на выходе параллельного сумматора 1 есть положительный результат суммирования чисел А и В, представленный в дополнительном модифицированном коде, числовая часть этого результата будет суммироваться с числом О ... О в параллельном сумматоре 2. Если на выходе параллельного сумматора 1 есть отрицательный результат суммирования чисел А и В, представ- ленньш в дополнительном модифицированном коде, на.выходе элемента И 7 будет единичный сигнал, так как на выходе элемента И-НЕ 10, выходе знакового разряда параллельного сумматора 1 и входе 17 задания режима устройства есть единичные сигналы. При этом числовая часть результата, полученного на выходе параллельного сумматора 1, будет суммироваться с числом 1 ... 1 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в обратном модифицированном коде.

Если число А представлено в обратном модифицированном коде, число В - в дополнительном модифицированном коде, а результат суммирования С должен быть представлен в дополнительном модифицированном коде, на входе 15 устройства будет единичный сигнал, а на входах 16 и 17 устройства будут нулевые сигналы. При этом на выходах элементов И 4-7 и ИЛИ 9 будут нулевые сигналы. Если число А отрицательное, а число В положительное .или отрицательное, на выходе элемента И 3 будет единичный сигнал, а следовательно, и на выходе элемента ИЛИ 8 будет единичный сигнал и в младший разряд параллельного сумматора 1 поступает дополнительная единица.

Если числа А и В положительные или число А положительное, а число В отрицательное, в младший разряд сумма

Если число А представлено в обратном модифицированном коде, а число В - в дополнительном модифицированном коде или число А представлено в до- 15 полнительном модифицированном коде, а число В - в обратном модифицированном коде и результат суммирования должен быть представлен в обратном модифицированном коде, процессы формирования результата суммирования чисел А и В в дополнительном модифицированном коде на выходе параллельного сумматора 1 аналогичны описанному. Если на выходе параллельного

тора 1 дополнительная единица поступать не будет. При этом на выходе параллельного сумматора 1 будет резуль- 25 сумматора 1 есть положительный результат суммирования чисел А и В в допол- тат суммирования чисел А и В, пред- нительном модифицированном коде, чис- ставленньй в дополнительном модифици- ловая часть которого суммируется с рованном коде, числовая часть этого числом О ... О в параллельном сумма- результата будет суммироваться с чис- торе 2. В итоге на выходе параллель- зо О ... О в параллельном сумматоного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде.

Если число А представлено в дополнительном модифицированном коде, число В - в обратном модифицированном коде,,а результат суммирования С должен быть представлен в дополнительном модифицированном коде, на входе 16 устройства будет единичный сигнал, а на входах 15 и 17 устройства будут нулевые сигналы. При этом на выходах элементов И 3 и 5-7 будут нулевые сигналы. Если число В отрицательное, а число А положительное или отрицательное, на выходе элемента И 4 будет единичный, сигнал, а следовательно, и на выходе элемента РШИ 8 будет единичный сигнал и в младший разряд параллельного сумматора 1 поступает дополнительная единица.

Если числа А и Б положительные ипи число В положительное, а число А отрицательное, в младший разряд сумматора 1 дополнительная единица поступать не будет. При этом на выходе параллельного сумматора 1 будет результат суммирования чисел А и В в допол35

40

45

50

55

ре 2.

Если на выходе параллельного сумматора 1 есть отрицательный результат суммирования чисел А и В, представленный в дополнительном модифицированном коде, на выходе элемента И 7 будет единичный сигнал, так как на выходе элемента И-НЕ 10, выходе знака параллельного сумматора 1 и входе 17 устройства есть единичные сигналы. При этом числовая часть результата, полученного на выходе параллельного сумматора 1, будет суммироваться с |Числом 1 ... 1 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в обратном модифицированном коде.

Если числа А и В представлены в обратных модифицированных кодах, а результат суммирования С должен быть представлен в дополнительном модифицированном коде, на выходах 15 и 16 устройства будут единичные сигналы, а на выходе 17 устройства - нулевой сигнал. При этом на выходах элементов И 6 и 7 будут нулевые сигналы. Если числа А и В положительные, на

нительном модифицированном коде, числовая часть :которого суммируется с числом О ... О в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в дополнительном модифицированном коде.

Если число А представлено в обратном модифицированном коде, а число В - в дополнительном модифицированном коде или число А представлено в до- полнительном модифицированном коде, а число В - в обратном модифицированном коде и результат суммирования должен быть представлен в обратном модифицированном коде, процессы формирования результата суммирования чисел А и В в дополнительном модифицированном коде на выходе параллельного сумматора 1 аналогичны описанному. Если на выходе параллельного

сумматора 1 есть положительный результат суммирования чисел А и В, пред- ставленньй в дополнительном модифици- рованном коде, числовая часть этого результата будет суммироваться с чис- О ... О в параллельном суммато

ре 2.

Если на выходе параллельного сумматора 1 есть отрицательный результат суммирования чисел А и В, представленный в дополнительном модифицированном коде, на выходе элемента И 7 будет единичный сигнал, так как на выходе элемента И-НЕ 10, выходе знака параллельного сумматора 1 и входе 17 устройства есть единичные сигналы. При этом числовая часть результата, полученного на выходе параллельного сумматора 1, будет суммироваться с |Числом 1 ... 1 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в обратном модифицированном коде.

Если числа А и В представлены в обратных модифицированных кодах, а результат суммирования С должен быть представлен в дополнительном модифицированном коде, на выходах 15 и 16 устройства будут единичные сигналы, а на выходе 17 устройства - нулевой сигнал. При этом на выходах элементов И 6 и 7 будут нулевые сигналы. Если числа А и В положительные, на

513434096

выходах элементов И 3-5, а следова-рованном коде, числовая часть кототельно, н на выходах элементов ИЛИ 8роге суммируется с числом 0... О в

и 9 будут нулевые сигналы., При этомпараллельном сумматоре 2. В итоге на

на выходе параллельного сумматора 1выходе параллельного сумматора 2 и будет результат суммвдования чисел А знаковом выходе параллельного суммаи В, числовая часть которого суммщэу-тора 1 будет результат С суммирования

ется с числом О ... О в параллельномчисел А и В в дополнительном модифисумматоре 2. В итоге на выходе парал-цированном коде.

лельного сумматора 2 и знаковом выхо- -JQ Если числа А и В представлены в

де параллельного сумматора 1будетобратных модифицированных кодах, а

результат С суммирования чисел в до-результат cylvlмиpoвaния С должен быть

полнительном модифицированном коде представлен также в обратном моди фиЕсли числа А и В отрицательные,цированном коде, на входах 15-17 на выходах элементов И 3-5, а следо- 15 устройства будут единичные сигналы,

вательно, и на выходах элементов ШШПри этом на выходах элементов И 3-5

8 и 9 будут единичные сигналы. В этоми 7, а следовательно, и на выходе

случае в младшие разряды параллельныхэлемента ИЛИ 8 будут нулевые сигналы,

сумматоров 1 и 2 поступают дополни-Если числа А и Б положительные, на тельные единицы. Числовая часть ре- 20 выходе 20 переноса параллельного сумзультата, полученного на выходе па-Матора 1 будет нулевой сигнал. Следораллельного сумматора 1, будет сумми-вательноз на выходах элементов И 6

роваться с числом 0..... 01 в парал-и ИЛИ 9 будут нулевые сигналы. При

лельном суммато ре 2. В итоге на выхо-этом на выходе параллельного суммато- де параллельного сумматора 2 и знако- 25 Р будет результат суммирования чивом выходе параллельного сумматора 1сел А и В, числовая часть которого

также будет результат С суммированиясуммируется с числом 0... О в паралчисел в дополнительном модифицирован-лельном сумматоре 2. В итоге на выхоном коде.,де параллельного сумматора 2 и знакоЕсли число А отршдательное а чис- 30 ° выходе параллельного сумматора 1

ло В положительноеэ на выходах эле-будет результат С суммирования чисел

ментов И 3 и И 4 будут соответственноА и В в обратном модифицированном

единичный и нулевой сигналы вслед-коде.

ствие чего на выходе элемента ИЛИ 8 Если числа А и В отрицательные, будет единичный сигнал и в младшийна выходе 20 переноса параллельного разряд параллельного сумматора 1 пос-сумматора 1 будет единичный сигнал, тупает дополнительная: единица. Привследствие чего на выходе элемента этом на выходе параллельного сумма-И 6, а следовательно, и на выходе тора 1 будет результат суммированияэлемента ИЛИ 9 будут единичные сигна- чисел А и В в дополнительном модифи- . лы и в младший разряд параллельного цированном коде, числовая часть кото-сумматора 2 поступает дополнительная рого суммируется с числом 0... О вединица. При этом числовая часть ре- параллельном сумматоре 2. В итоге назультата, полученного на выходе па- выкоде параллельного сумматора 2 ираллельного сумматора 1, будет сумми- знаковом выходе параллельного сумма-роваться с числом 0... 01 в парал- тора 1 будет результат С суммированиялельном сумматоре 2. В итоге на выхо- чисел А и В в дополнительном модифи-де параллельного с-умматора 2 и знако- цированном коде овом выходе параллельного сумматора 1

Если число А положительное,, а чис-будет результат .С суммирования чи- ло В отрицательное, на вы ;;одах элег „ сел А и В в обратном модифицированном

|МентоБ И 3 и 4 будут соответственно.коде.

нулевой и единичный сигналы, вслед- Если число А отрицательное, а чисствие чего на выходе элемента ИЛИ 8ло В положительное или ч|1сло А поло-:

будет единичный сигнал н в младшийжительное,. а число В отрицательное и

разряд параллельного сумматора 1 пос-на выходе 20 переноса параллельного

тупает дополнительная единица. Присумматора 1 есть единичный сигнал, на

э-том на выходе параллельного суммато-выходе элемента И 6, а следовательно,

ра 1 будет результат сумми;рования чи-и на выходе элемента ИЛИ 9 будут едисел А и В в дополнительном модифици-ничные сигналы и в младший разряд параллельного сумматора 2 поступает дополнительная единица. При этом числовая часть результата, полученного на выходе параллельного сумматора 1, будет суммироваться с числом 0... 01 в параллельном сумматоре 2. В итоге на выходе параллельного сумматора 2 и знаковом выходе параллельного сум15

матора 1 будет результат С суммирова- -|Q ства соединен с вторыми входами трения чисел А и В в обратном модифицированном коде.

Если число А отрицательное, а число В положительное или число А положительное, а число В отрицательное и на выходе 20 переноса параллельного сумматора 1 есть нулевой сигнал, на выходе элемента И 6, а следовательно, и на выходе элемента ИЛИ 9 будут -нулевые сигналы. При этом числовая часть 2о результата, полученного на выходе параллельного сумматора 1, будет суммироваться с числом О... О в параллельном сумматоре 2. В итоге на выхотьего и четвертого элементов И, выход первого элемента ИЛИ соединен с входом переноса первого параллельного сумматора, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первым входом старшего разряда второго параллельного сумматора, первые гвходы разрядов которого, кроме старшего, соединены с выходом третьего элемента И, вход переноса младшего разряда второго парал-г. лельного сумматора соединен с шиной

де параллельного сумматора 2 и знако- 25 нулевого потенциала устройства, выховом выходе параллельного сумматора 1 будет результат С суммирования чисел А и В в обратном модифицированном коде.

Формула изобретен и я

Устройство для суммирования двоичных чисел, содержащее первый и второй параллельные сумматоры, пять элементов И, два элемента ИЛИ, причем входы знаковых разрядов первого и второго операндов устройства соединены с первыми входами соответственно первого и второго элементов И и соответственно с первым и вторым входами знаковых разрядов первого параллельного сумматора, выход знакового разряда которого соединен с выходом знакового разряда результата устройства и первым входом третьего элемента И, информационные входы первого и второго операндов устройства соединены с первыми и вторыми входами соответствующих числовых разрядов первого параллельного сумматора, выход переноса которого соединен с первым входом четвертого элемента И, вторые

30

35

40

45

50

ды числовых разрядов первого параллельного сумматора соединены соответственно с вторыми входами разрядов второго -параллельного сумматора, выходы разрядов которого соединены с выходом результата устройства, третий вход второго элемента ИЛИ соединен с выходом пятого элемента И, отличающееся тем, что, с целью упрощения устройства, оно дополнительно содержит элемент И-НЕ, первый, второй и третий входы которого соединены соответственно с входами управления представлениями первого и второго операндов и результата устройства, выход элемента И-НЕ соединен с вторым входом первого элемента И и третьим входом третьего элемента И,, выход первого элемента И соединен с первыми входами первого элемента ИЛИ и пятого элемента И, выход второго элемента И соединен с вторыми входами первого элемента ИЛИ и пятого элемента И, третий и четвертый входы чет- . вертого элемента И соединены соответственно с входами управления пред-, ставлениями второго операнда и результата устройства.

входы первого и второго элементов И соединены меладу собой,- входы управления представлением первого операнда и управления представлением второго операнда устройства соединены соответственно с третьими входами первого и второго элементов И, вход управления представлением результата устрой

ства соединен с вторыми входами тре

тьего и четвертого элементов И, выход первого элемента ИЛИ соединен с входом переноса первого параллельного сумматора, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с первым входом старшего разряда второго параллельного сумматора, первые гвходы разрядов которого, кроме старшего, соединены с выходом третьего элемента И, вход переноса младшего разряда второго парал-г. лельного сумматора соединен с шиной

0

5

0

5

0

ды числовых разрядов первого параллельного сумматора соединены соответственно с вторыми входами разрядов второго -параллельного сумматора, выходы разрядов которого соединены с выходом результата устройства, третий вход второго элемента ИЛИ соединен с выходом пятого элемента И, отличающееся тем, что, с целью упрощения устройства, оно дополнительно содержит элемент И-НЕ, первый, второй и третий входы которого соединены соответственно с входами управления представлениями первого и второго операндов и результата устройства, выход элемента И-НЕ соединен с вторым входом первого элемента И и третьим входом третьего элемента И,, выход первого элемента И соединен с первыми входами первого элемента ИЛИ и пятого элемента И, выход второго элемента И соединен с вторыми входами первого элемента ИЛИ и пятого элемента И, третий и четвертый входы чет- . вертого элемента И соединены соответственно с входами управления пред-, ставлениями второго операнда и результата устройства.

22

Ч.

Редактор П.Гереши

Составитель М Есенина Техред Л Сердюкова

Заказ 4824/49Тираж 672.Подписное

ВНГО1ПИ Государственного комитета СССР

по делам изобретений и открытий 113035., Москва, Ж-ЗЗ Раушская наб., д. 4/5

Производстванно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

8

Фм.г

Корректор .М. Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1264164A1 |

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1270757A1 |

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1193665A1 |

| Устройство для суммирования последовательных кодов | 1984 |

|

SU1254472A1 |

| Устройство для сложения чисел | 1987 |

|

SU1469503A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - упрощение устройства. Устройство содержит два параллельных 15 16 сумматора 1 и 2, пять элементов И 3-7, два элемента ИЛИ 8 и 9, элемент И-НЕ 10, которые соответствующим образом соединены между собой и с тремя входами задания режима устройства, входами знаковых разрядов и информационными входами первого и второго операндов устройства, выходом знакового разряда и информационными выходами устройства. Устройство вьшолняет суммирование двоичных чисел, каждое из которых может быть предназначено в дополнительном или обратном модифицированном коде, а результат суммирова-. ния формирует в дополнительном или обратном модифицированном коде при выигрьше в оборудовании в 2 -раза по сравнению с прототипом (в схеме управления) . 2 ил. -.Д , , 12 ft t ill О to (Л 00 4 СО N О со

| Устройство для суммирования двоичных чисел | 1984 |

|

SU1193665A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования двоичных чисел | 1985 |

|

SU1264164A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-07—Публикация

1986-04-07—Подача