(Л

сриг.1

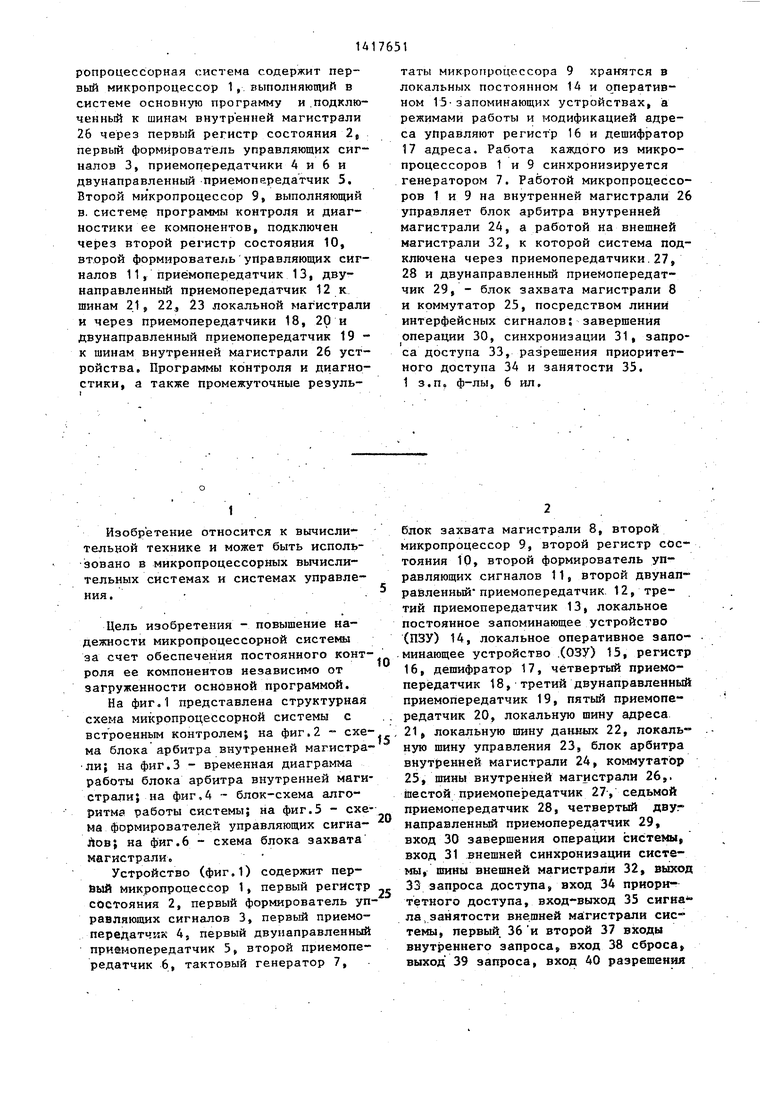

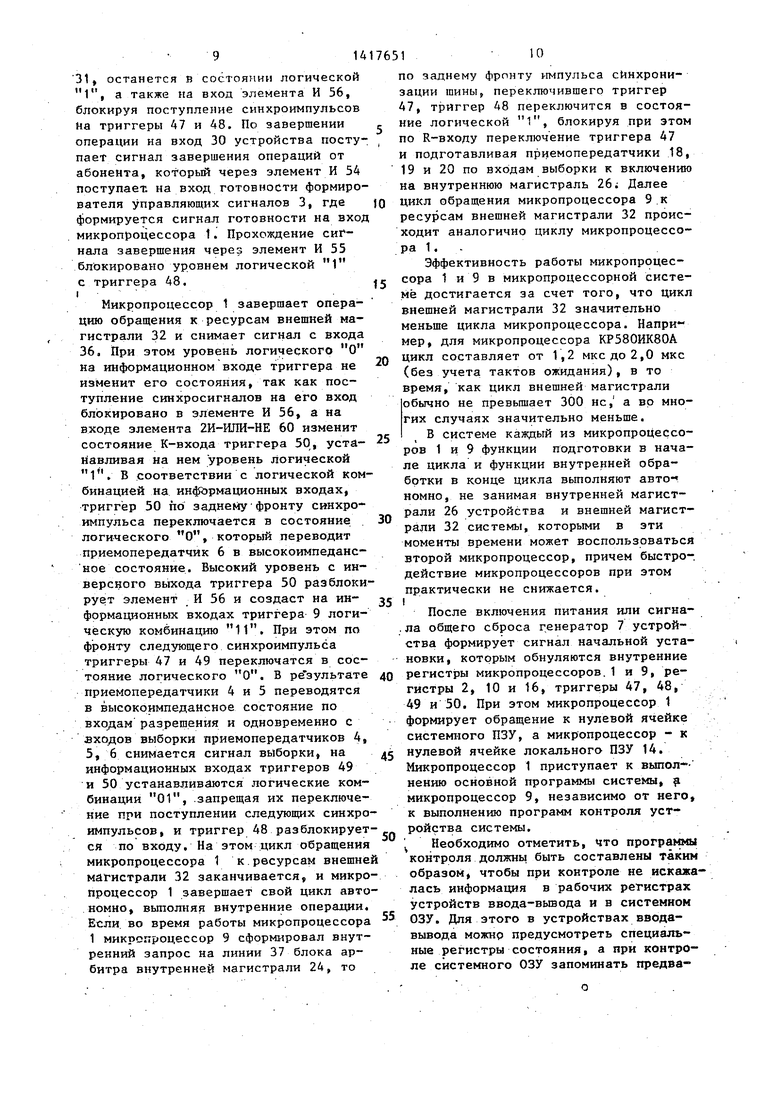

ропроцессорная система содержит первый микропроцессор 1, выполняющий в системе основную программу и.подключенный к шинам внутренней магистрали 26 через первый регистр состояния 2, первый формирователь управляющих сигналов 3, приемопередатчики 4 и 6 и двунаправленный приемопередатчик 5, Второй ми кропроцессор 9, выполняющий в. системе программы контроля и диагностики ее компонентов, подключен через второй регистр состояния 10, второй формирователь управляющих сигналов 11, приёмопередатчик 13, двунаправленный приемопередатчик 12 к шинам 21, 22, 23 локальной магистрали и через приемопередатчики 18, 20 и двунаправленный приемопередатчик 19- к шинам внутренней магистрали 26 устройства. Программы контроля и диагностики, а также промежуточные результаты микропроцессора 9 хранятся в локальных постоянном 14 и оперативном 15-запоминающих устройствах, а режимами работы и модификацией адреса управляют регистр 16 и дешифратор 17 адреса. Работа каждого из микропроцессоров 1 и 9 синхронизируется генератором 7. Работой микропроцессоров 1 и 9 на внутренней магистрали 26 управляет блок арбитра внутренней магистрали 24, а работой на внешней магистрали 32, к которой система подключена через приемопередатчики.27, 28 и двунаправленный приемопередатчик 29, - блок захвата магистрали 8 и коммутатор 25, посредством линии интерфейсных сигналов; завершения операции 30, синхронизации 31, запроса доступа 33, разрешения приоритетного доступа 34 и занятости 35. 1 з.п. ф-лы, 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Устройство для сопряжения микропроцессора с магистралью | 1985 |

|

SU1302287A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство сопряжения многопроцессорной системы | 1987 |

|

SU1575195A1 |

| Многомашинная вычислительная система | 1990 |

|

SU1798798A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных вычисли тельных системах и системах управления. Цель изобретения - повьшение йа- дежности микропроцессорной ёистемы путем обеспечения постоянного контроля ее компо 1ентоп независимо от загруженности основной программой. МиК- 26

1

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных вычислительных системах и системах управления.

Цель изобретения - повышение надежности микропроцессорной системы за счет обеспечения постоянного контроля ее компонентов независимо от загруженности основной программой.

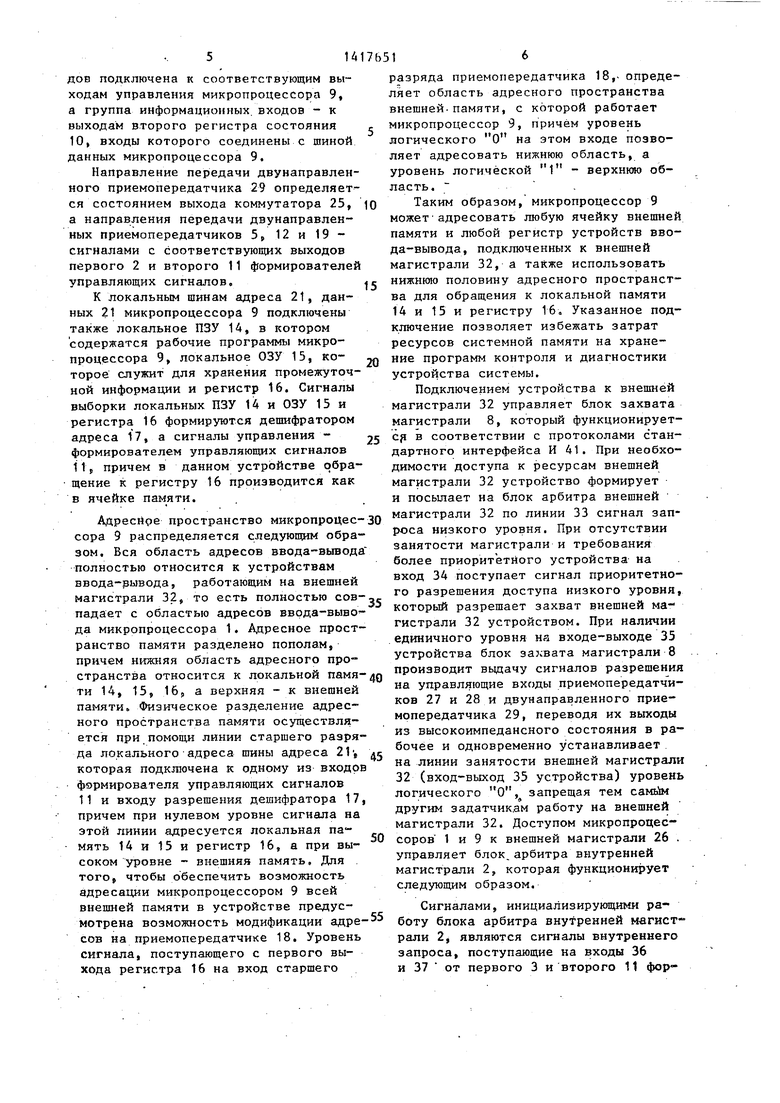

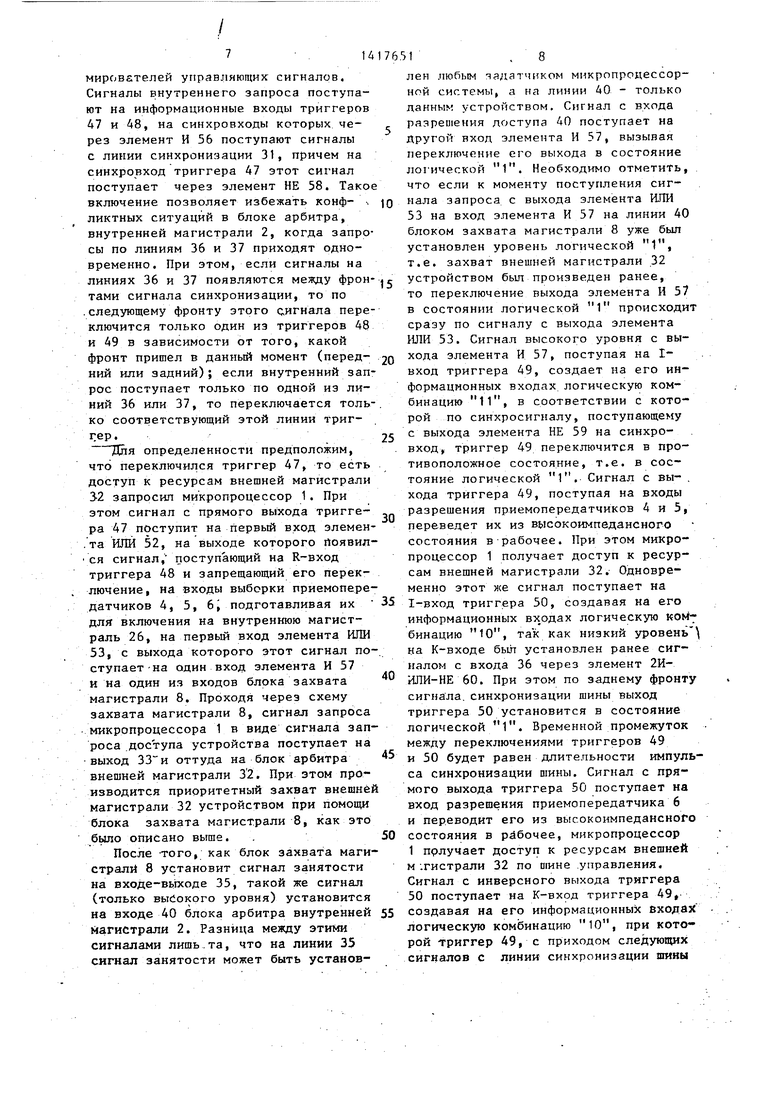

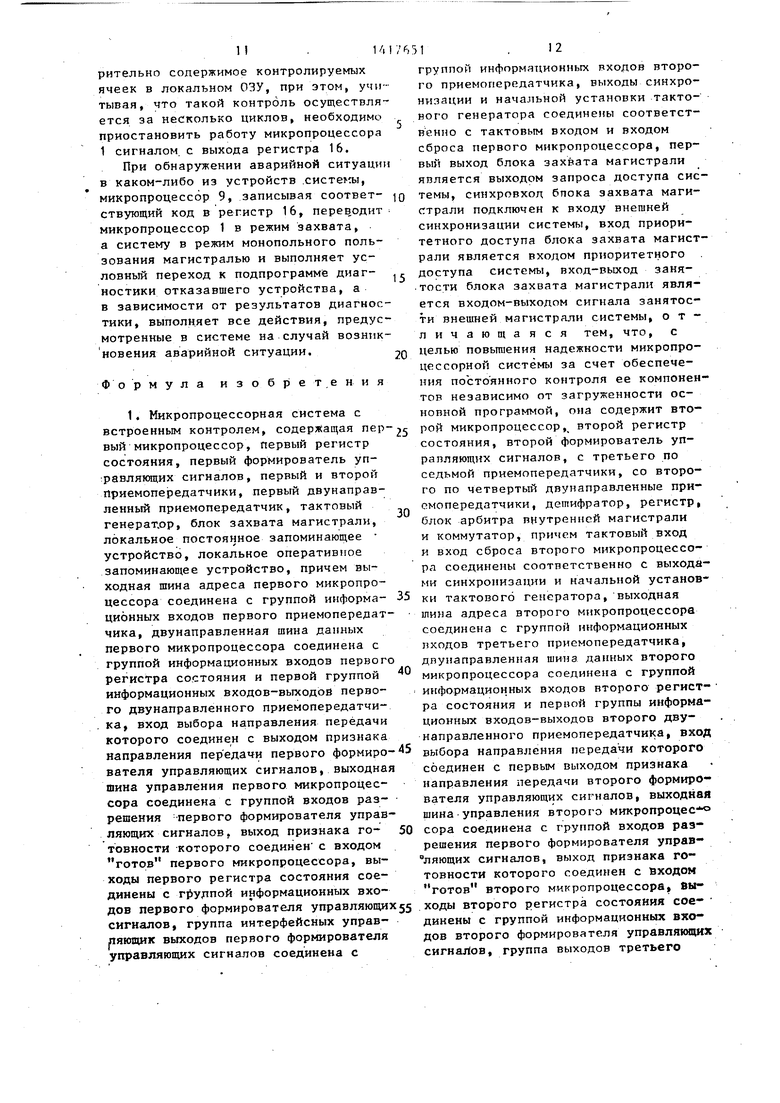

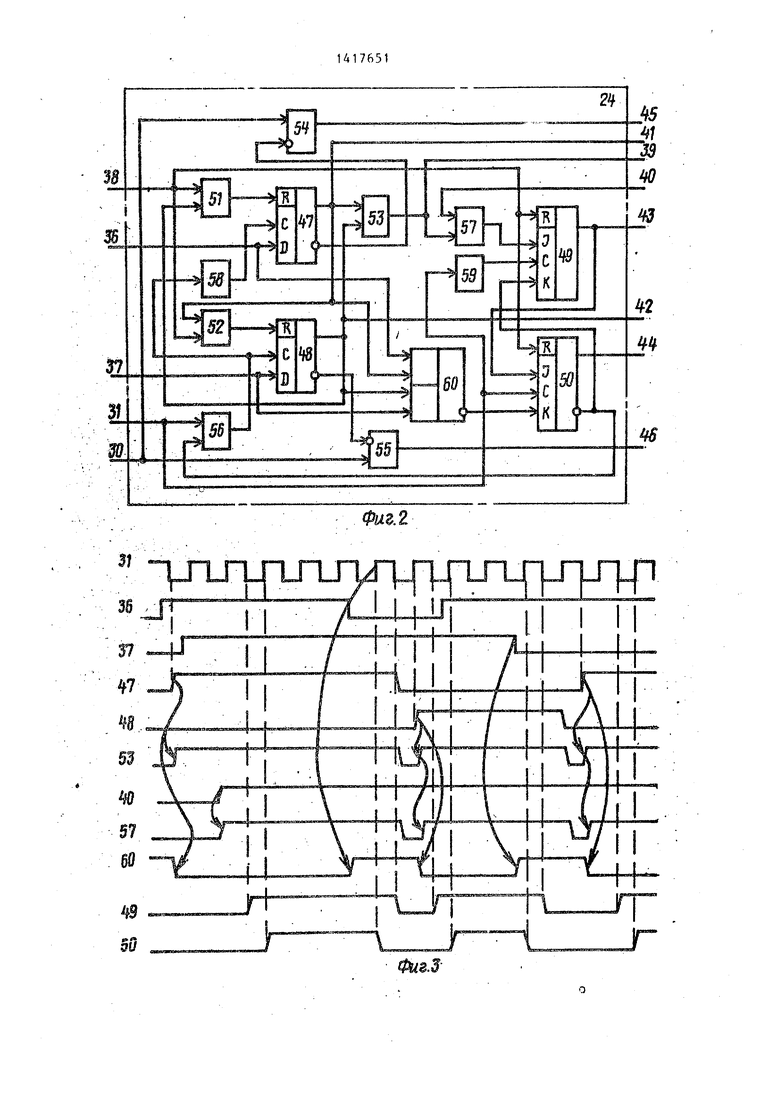

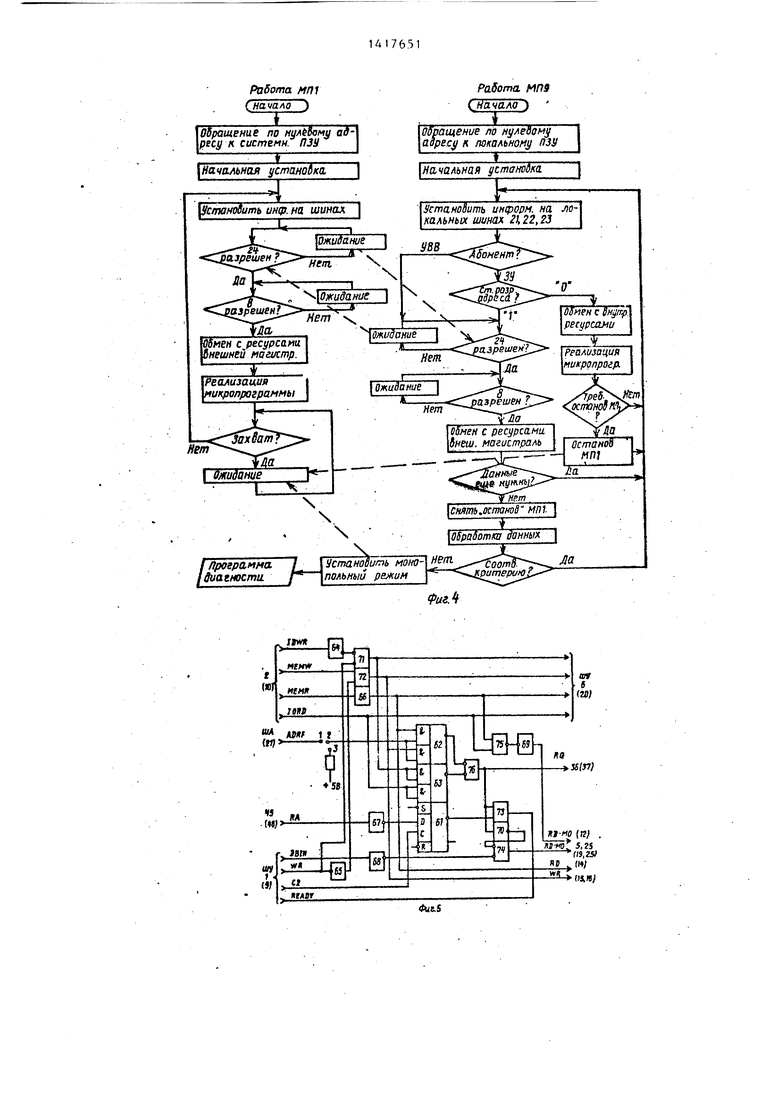

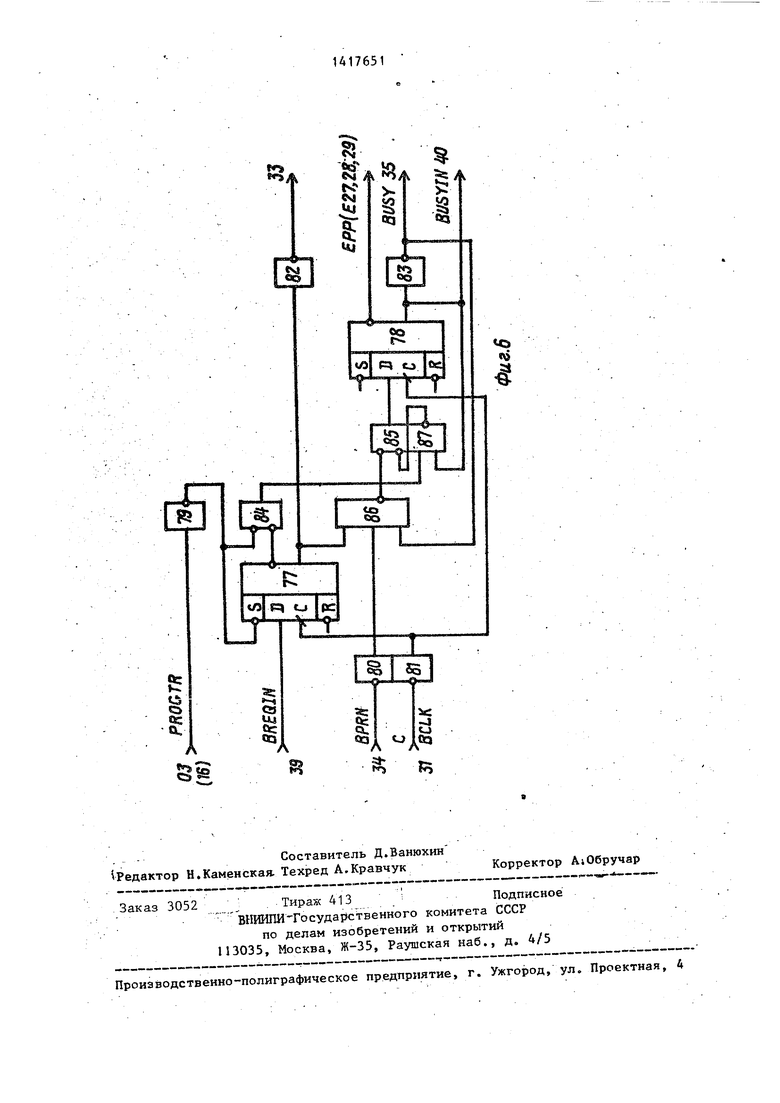

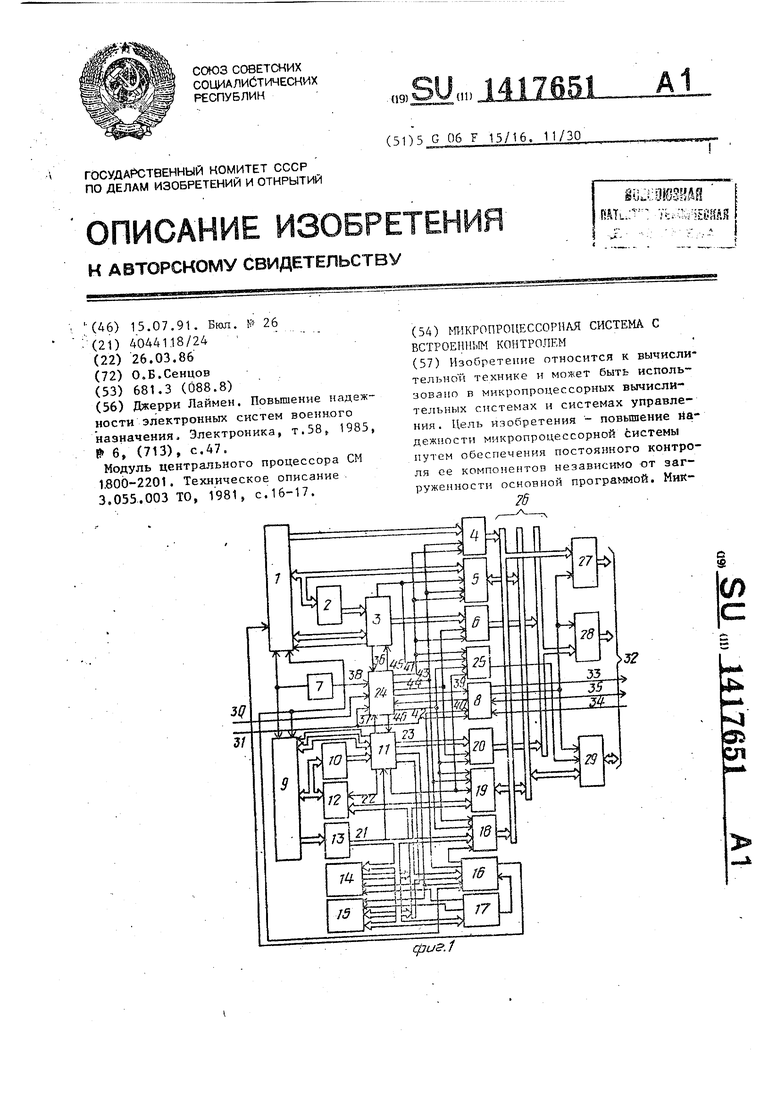

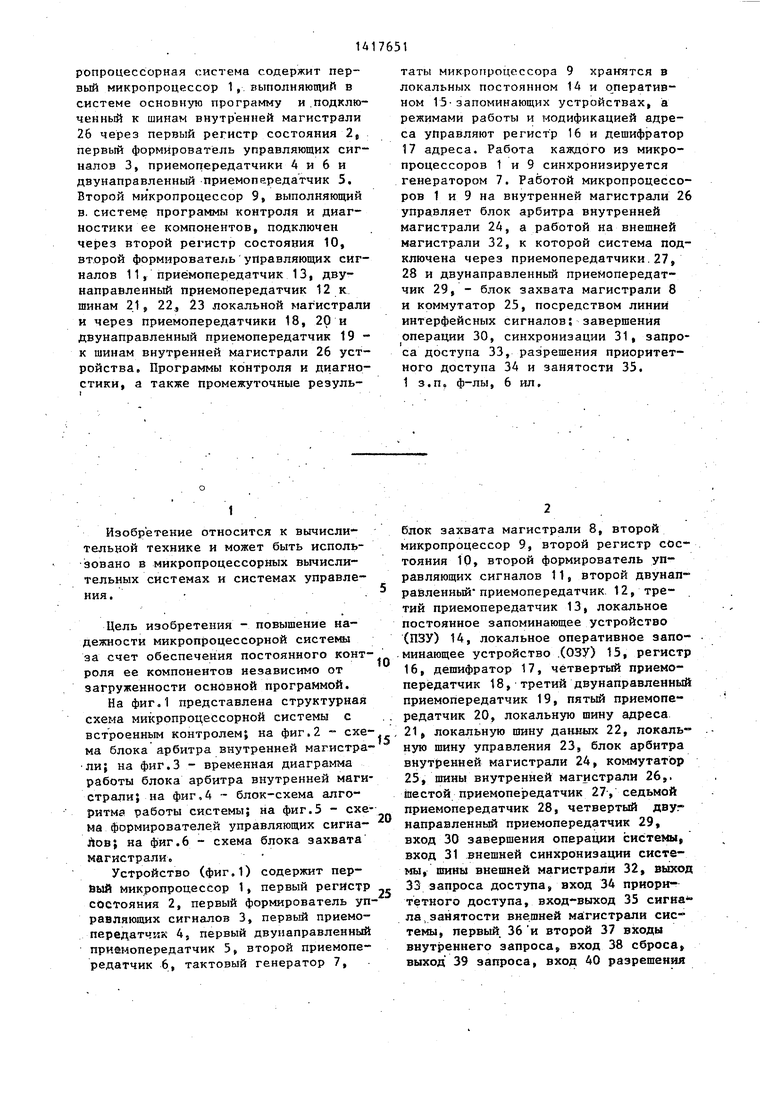

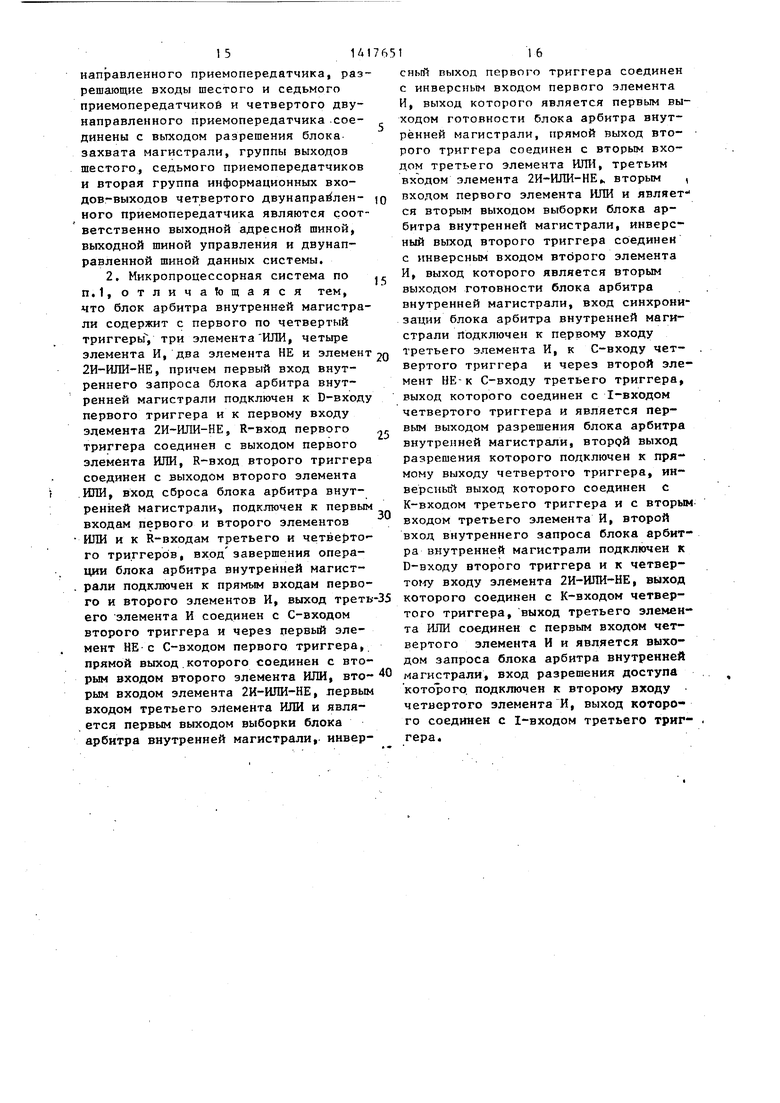

На фиг,1 представлена структурная схема микропроцессорной системы с встроенным контролем$ на фиг.2 - схема блока арбитра внутренней магистра- ли; на фиг.З - временная диаграмма работы блока арбитра внутренней магистрали} на фиг,4 блок-схема алгоритма работы системы; на фиг.З - схема формирователей управляющих сигна- Лов; на фиг.6 - схема блока захвата магистрали,

Устройство (фиг.1) содержит пер- йый Микропроцессор 1, первый регистр состояния 2, первый формирователь управляющих сигналов 3, первый приемопередатчик 4, первый двунаправленный приёмопередатчик 5, второй приемопередатчик 6, тактовый генератор 7,

-

блок захвата магистрали 8, второй микропроцессор 9, второй регистр состояния Ю, второй формирователь управляющих сигналов 11, второй двунаправленный приемопередатчик. 12, третий приемопередатчик 13, локальное постоянное запоминающее устройство (ПЗУ) 14, локальное оперативное запоминающее устройство .(ОЗУ) 15, регистр 16, дешифратор 17, четвертый приемопередатчик 18, третий двунаправленный приемопередатчик 19, пятый приемопередатчик 20, локальную шину адреса 21, локальную шину данных 22, локальную шину управления 23, блок арбитра внутренней магистрали 24, коммутатор 25, шины внутренней магистрали 26,, йестой приемопередатчик 27, седьмой приемопередатчик 28, четвертый двуг направленный приемопередатчик 29, вход 30 завершения операции системы, вход 31 внешней синхронизации системы, шины внешней магистрали 32, выход 33 запроса доступа, вход 34 приоритетного доступа, вход-выход 35 сигнала, занятости внешней ма:гистрали системы, первый 36 и второй 37 входы внутреннего запроса, вход 38 сброса, выход 39 запроса, вход 40 разрешения

- lA

доступа, первый 41 и второй 42 РЫходы выборки, первый 43 и второй 44 выходы разрешения, первый 45 и второй 46 выходы готовности блока арбитра внутренней магистради.

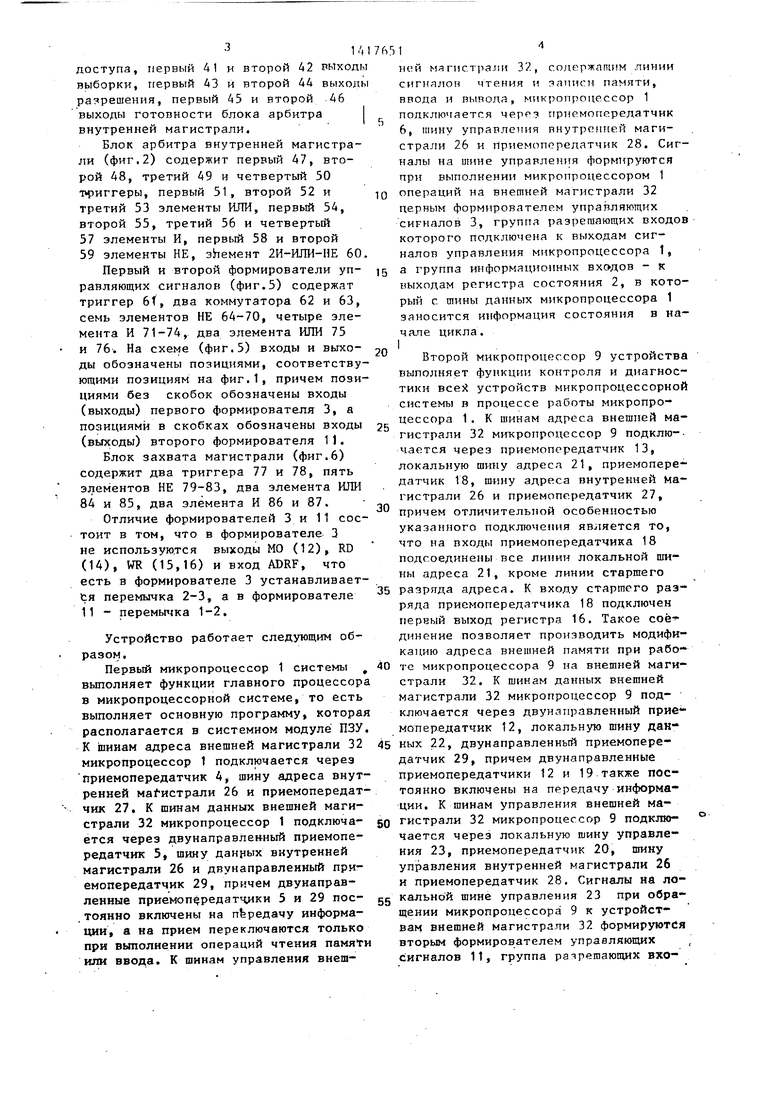

Блок арбитра внутренней магистрали (фиг.2) содержит первый 47, второй 48, третий 49 и четвертый 50 тч иггеры, первый 51, второй 52 и третий 53 элементы ИЛИ, первый 54, второй 55, третий 56 и четвертый 57 элементы И, первьй 58 и второй 59 элементы НЕ, эЬемент 2И-ИЛИ-НЕ 60

Первый и второй формирователи управляющих сигналов (фиг.5) содержат триггер 61, два коммутатора 62 и 63, семь элементов НЕ 64-70, четыре элемента И 71-74, два элемента ИЛИ 75 и 76. На схеме (фиг.5) входы и выходы обозначены позициями, соответствующими позициям на фиг.1, причем позициями без скобок обозначены входы (выходы) первого формирователя 3, а позициями в скобках обозначены входы (выходы) второго формирователя 1J.

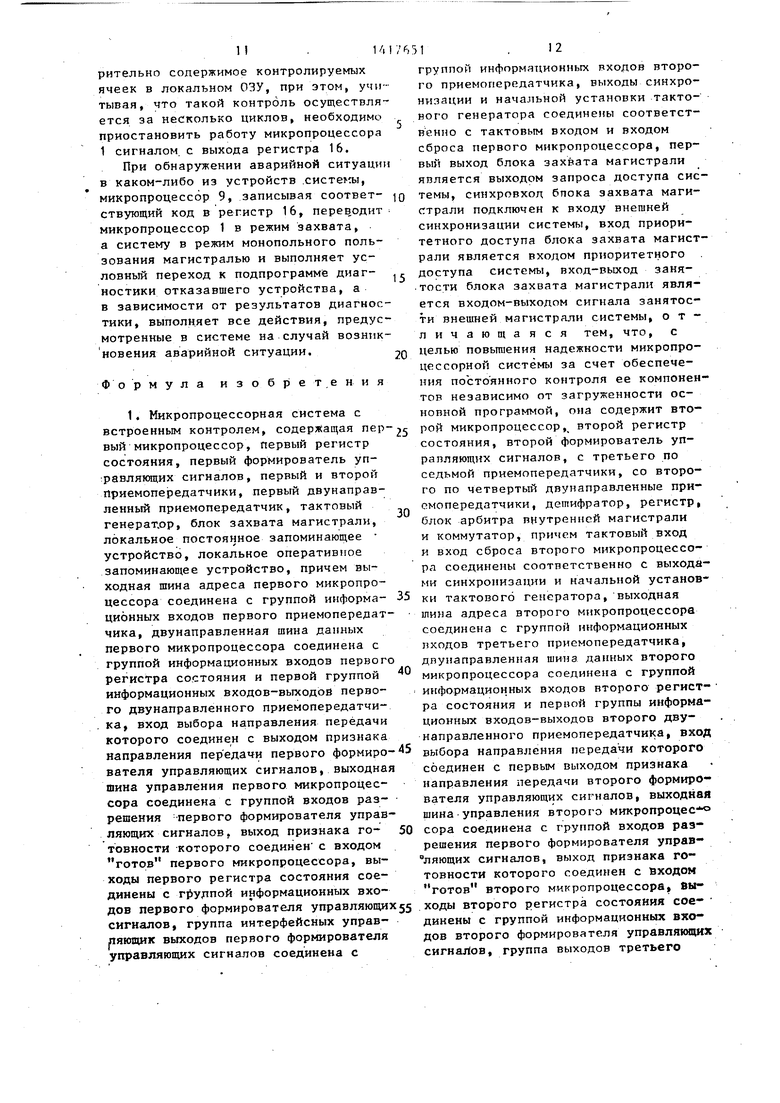

Блок захвата магистрали (фиг.6) содержит два триггера 77 и 78, пять элементов НЕ 79-83, два элемента ИЛИ 84 и 85, два элемента И 86 и 87.

Отличие формирователей 3 и 11 состоит в том, что в формирователе 3 не используются выходы МО (12), RD (14), WR (15,16) и вход ADRF, что есть в формирователе 3 устанавливается перемычка 2-3, а в формирователе 11 - перемычка 1-2.

Устройство работает следующим образом.

Первый микропроцессор 1 системы , вьтолняет функции главного процессора в микропроцессорной системе, то есть выполняет основную программу, которая располагается в системном модуле ПЗУ. К шинам адреса внешней магистрали 32 микропроцессор 1 подключается через приемопередатчик 4, шину адреса внутренней магистрали 26 и приемопередатчик 27, К шинам данных внешней магистрали 32 микропроцессор 1 подключается через двунаправленный приемопередатчик 5, шину данрых внутренней магистрали 26 и двунаправленный приемопередатчик 29, причем двунаправленные приемопередатчики 5 и 29 постоянно включены на передачу информации, а на прием переключаются только при вьтолнении операций чтения памяти или ввода. К шинам управления внеш0

5

fv4

ной магистрали 3., содержап(им линии снгиялоп чтения ч записи памяти, ввода и вывода, мякропгюиессор 1 J. подключается черрз приемопередатчик 6, шину управления пнутрсние.й магистрали 26 и приемопередатчик 28. Сигналы на шине управления формтфуются при выполнении микроироцессором 1

0 операций на внешней магистрали 32 первым формирователем управляющих сигналов 3, группа разрешающих входов которого подключена к выходам сиг- налои управления микропроцессора 1,

5 а группа информационных входов - к выходам регистра состояния 2, в который с шины данных микропроцессора 1 заносится информация состояния в начапе цикла. 1

Второй микропроцессор 9 устройства выполняет функции контроля и диагностики всеЯ устройств микропроцессорной системы в процессе работы микропроцессора 1. К шинам адреса внешней магистрали 32 михроироцессор 9 подклю-- чается через приемопередатчик 13, локальную шину адреса 21, приемопередатчик 18, шину адреса внутренней магистрали 26 и приемопередатчик 27, причем отличительной особенностью указанного подключения является то, что на входы приемопередатчика 18 подсоединены все линии локальной шины адреса 21, кроме линии старшего

5 разряда адреса. К входу старшего разряда приемопередатчика 18 подключен первый выход регистра 16. Такое соё- динение позволяет производить модификацию адреса внешней памяти при рабо0 те микропроцессора 9 на внешней магистрали 32. К шинам данных внешней магистрали 32 микропроцессор 9 подключается через двунаправленный приемопередатчик 12, локальную шину дан5 ных 22, двунаправленный приемопередатчик 29, причем двунаправленные приемопередатчики 12 и 19 также постоянно включены на передачу информации. К шинам управления внешней ма0 гистрали 32 микропроцессор 9 подклю- ° чается через локальную шину управления 23, приемопередатчик 20, шину управления внутренней магистрали 26 и приемопередатчик 28. Сигналы на лоg кальной шине управления 23 при обращении микропроцессора 9 к устройствам внешней магистрали 32 формируются вторым формирователем управляющих , сигналов 11, группа разрешающих вхо-

0

flOB подключена к соответствующим выходам управления микропроцессора 9, а группа информационных, входов - к выходам второго регистра состояния

10,входы которого соединены с шиной данных микропроцессора 9,

Направление передачи двунаправленного приемопередатчика 29 определяется состоянием выхода коммутатора 25, а направления передачи двунаправленных приемопередатчиков 5, 12 и 19 - сигналами с соответствующих выходов первого 2 и второго 11 формирователей управляющих сигналов,

К локальным шинам адреса 21, данных 21 микропроцессора 9 подключены также локальное ПЗУ 14, в котором содержатся рабочие программы микропроцессора 9, локальное ОЗУ 15, ко торое служит для хранения промежуточной информации и регистр 16. Сигналы выборки локальных ПЗУ 14 и ОЗУ 15 и регистра 16 формируются дешифратором адреса 17, а сигналы управления - формирователем управляющих сигналов

11,причем в данном устройстве обращение к регистру 16 производится как в ячейке памяти.

Адресное пространство микропроЦес-30 магистрали 32 по линии 33 сигнал запроса низкого уровня. При отсутствии занятости магистрали и требования более приоритетного устройства на вход 34 поступает сигнал приоритетного разрешения доступа низкого уровня, который разрешает захват внешней магистрали 32 устройством. При наличии единичного уровня на входе-выходе 35 устройства блок захвата магистрали 8

сора 9 распределяется следующем образом. Вся область адресов ввода-вывода полностью относится к устройствам ввода-вывода, работающим на внешней магистрали 32, то есть полностью совпадает с областью адресов ввода-вывода микропроцессора 1. Адресное пространство памяти разделено пополам, причем ншкняя область адресного про™

35

роса низкого уровня. При отсутствии занятости магистрали и требования более приоритетного устройства на вход 34 поступает сигнал приоритетного разрешения доступа низкого уровня, который разрешает захват внешней магистрали 32 устройством. При наличии единичного уровня на входе-выходе 35 устройства блок захвата магистрали 8

странства относится к локальной памя-40 ПРОИЗВОДИТ вьщачу сигналов разрешения

ти 14, 15, 16j а верхняя - к внешней памяти. Физическое разделение адресного пространства памяти осуществляется при помощи линии старшего разряда локального-адреса шины адреса 21, 5 которая подключена к одному из входов формирователя управляющих сигналов 11 и входу разрешения дешифратора 17, причем при нулевом уровне сигнала на этой линии адресуется локальная па мять 14 и 15 и регистр 16, а при высоком уровне - внешняя память. Для того, чтобы обеспечить возможность адресации микропроцессором 9 всей внешней памяти в устройстве предус™

50

на управляющие входы приемопередатчиков 27 и 28 и двунаправленного приемопередатчика 29, переводя их выходы из высокоимпедансного состояния в рабочее и одновременно устанавливает на линии занятости внешней магистрали 32 (вход-выход 35 устройства) уровень логического О, запрещая тем самьЫ другим задатчикам работу на внешней магистрали 32. Доступом микропроцессоров 1 и 9 к внешней магистрали 26 . управляет блок.арбитра внутренней магистрали 2, которая функционирует следующим образом.

Сигналами, инициализирующими рамотрена возможность модификации адре- боту блока арбитра внутренней магнстсов на приемопередатчике 18. Уровень сигнала, поступающего с первого выхода регистра 16 на вход старшего

17()516

разряда приемопередатчика 18,- определяет область адресного пространства внешней-памяти, с которой работает . микропроцессор 9, причём уровень логического О на этом входе позволяет адресовать нижнюю область, а уровень логической 1 - верхнюю область. .

0 Таким образом, микропроцессор 9 может адресовать любую ячейку внешней памяти и любой регистр устройств ввода-вывода, подключенных к внешней магистрали 32, а тайже использовать нижнюю половину адресного пространства для обращения к локальной памяти 14 и 15 и регистру 16. Указанное подключение позволяет избежать затрат ресурсов системной памяти на хране20 ние программ контроля и диагностики устройства системы.

Подключением устройства к внешней магистрали 32 управляет блок захвата магистрали 8, который функционирует25 Cfi в соответствии с протоколами стандартного интерфейса И 41. При необходимости доступа к ресурсам внешней магистрали 32 устройство формирует и посылает на блок арбитра внешней

15

магистрали 32 по линии 33 сигнал зап

роса низкого уровня. При отсутствии занятости магистрали и требования более приоритетного устройства на вход 34 поступает сигнал приоритетного разрешения доступа низкого уровня, который разрешает захват внешней магистрали 32 устройством. При наличии единичного уровня на входе-выходе 35 устройства блок захвата магистрали 8

ПРОИЗВОДИТ вьщачу сигналов разрешения

на управляющие входы приемопередатчиков 27 и 28 и двунаправленного приемопередатчика 29, переводя их выходы из высокоимпедансного состояния в рабочее и одновременно устанавливает на линии занятости внешней магистрали 32 (вход-выход 35 устройства) уровень логического О, запрещая тем самьЫ другим задатчикам работу на внешней магистрали 32. Доступом микропроцессоров 1 и 9 к внешней магистрали 26 . управляет блок.арбитра внутренней магистрали 2, которая функционирует следующим образом.

Сигналами, инициализирующими работу блока арбитра внутренней магнстрали 2, являются сигналы внутреннего

запроса, поступающие на входы 36

и 37 от первого 3 и второго 11 фор-

мирователей управляющих сигналов. Сигналы внутреннего запроса поступают на информационные входы триггеров 47 и 48, на синкровходы которых через элемент И 56 поступают сигналы с линии синхронизации 31, причем на синхровход триггера 47 этот сигнал поступает через элемент НЕ 58. Такое включение позволяет избежать конф- ч ликтных ситуаций в блоке арбитра, внутренней магистрали 2, когда запросы по линиям 36 и 37 приходят одновременно. При этом, если сигналы на

линиях 36 и 37 появляются между фрон-.с устройством был произведен ранее.

20

25

30

тами сигнала синхронизации, то по .следующему фронту этого сигнала переключится только один из триггеров 48 и 49 в зависимости от того, какой фронт пришел в данный момент (передний или задний); если внутренний запрос поступает только по одной из линий 36 или 37, то переключается только соответствующий этой линии три:- гер.

1&я определенности предположим, что переключился триггер 47, то есть доступ к ресурсам внешней магистрали 3-2 запросил микропроцессор 1 . При этом сигнал с прямого выхода триггера 47 поступит на первый вход злемен- .та ИЛИ 52, на выходе которого появил- ся сигнал, поступающий на R-вход триггера 48 и запрещающий его переключение , на входы выборки приемопередатчиков 4, 5, 6i подготавливая их 35 для включения на внутреннюю магистраль 26, на первый вход элемента ИЛИ 53, с выхода которого этот сигнал поступает -на один вход элемента И 57 и на один из входов блока захвата магистрали 8. Проходя через схему захвата магистрали 8, сигнал запроса микропроцессора 1 в виде сигнала запроса доступа устройства поступает на выход оттуда на блок арбитра внешней магистрали 32, При этом производится приоритетный захват внешней магистрали 32 устройством при помощи блока захвата магистрали 8, как это было описано выше. .50

После -того, как блок захвата магистрали 8 установит сигнал занятости на входе-вьЬсоде 35, такой же сигнал (только высокого уровня) установится на входе 40 блока арбитра внутренней 55 магистрали 2. Разница между этими сигналами лишь.та, что на линии 35 сигнал занятости может быть установ40

то переключение выхода элемента И в состоянии логической 1 происх сразу по сигналу с выхода элемент ИЛИ 53. Сигнал высокого уровня с хода элемента И 57, поступая на I вход триггера 49, создает на его формационных входах логическую ко бинацию 11, в соответствии с ко рой по синхросигналу, поступающе с выхода элемента НЕ 59 на синхро вход, триггер 49 переключится в п тивоположное состояние, т.е. в со тояние логической 1. Сигнал с в хода триггера 49, поступая на вход разрешения приемопередатчиков 4 и переведет их из высокоимпедансного состояния в рабочее. При этом мик процессор 1 получает доступ к ресу сам внешней магистрали 32. Одновр менно этот же сигнал поступает на 1-вход триггера 50, создавая на е информационных входах логическую к бинацию 10, так как низкий урове на К-входе был установлен ранее си налом с входа 36 через элемент 2И- ИЛИ-НЕ 60. При этом по заднему фро сигнала, синхронизации шины выход триггера 50 установится в состояни логической 1. Временной промежут между переключениями триггеров 49 и 50 будет равен длительности имп са синхронизации шины. Сигнал с пр мого выхода триггера 50 поступает вход разрешения приемопередатчика и переводит его из вьюокоимпедансн состояния в рабочее, микропроцессо 1 прлучает доступ к ресурсам внешн м .гистрали 32 по ашне .управления. Сигнал с инверсного выхода триггер 50 поступает на К-вход триггера 49 создавая на его информационных вхо логическую комбинацию 10, при ко рой триггер 49, с приходом следующ сигналов с линии синхронизации ши

лен любым яадатчиком микропроцессорной системы, а на линии 40 - только данным устройством. Сигнал с входа разрешения доступа 40 поступает на другой вход элемента И 57, вызывая переключение его выхода в состояние логической 1. Необходимо отметить, что если к моменту поступления сигнала запроса с выхода элемента ИЛИ 53 на вход элемента И 57 на линии 40 блоком захвата магистрали 8 уже был установлен уровень логической 1, т.е. захват внешней магистрали 32

0

5

0

5 0

0

то переключение выхода элемента И 57 в состоянии логической 1 происходит сразу по сигналу с выхода элемента ИЛИ 53. Сигнал высокого уровня с выхода элемента И 57, поступая на I- вход триггера 49, создает на его информационных входах логическую комбинацию 11, в соответствии с которой по синхросигналу, поступающему с выхода элемента НЕ 59 на синхровход, триггер 49 переключится в противоположное состояние, т.е. в состояние логической 1. Сигнал с вы- , хода триггера 49, поступая на входы разрешения приемопередатчиков 4 и 5, переведет их из высокоимпедансного состояния в рабочее. При этом микропроцессор 1 получает доступ к ресурсам внешней магистрали 32. Одновременно этот же сигнал поступает на 1-вход триггера 50, создавая на его информационных входах логическую ком-;- бинацию 10, так как низкий уровень на К-входе был установлен ранее сигналом с входа 36 через элемент 2И- ИЛИ-НЕ 60. При этом по заднему фронту сигнала, синхронизации шины выход триггера 50 установится в состояние логической 1. Временной промежуток . между переключениями триггеров 49 и 50 будет равен длительности импульса синхронизации шины. Сигнал с прямого выхода триггера 50 поступает на вход разрешения приемопередатчика 6 и переводит его из вьюокоимпедансного состояния в рабочее, микропроцессор 1 прлучает доступ к ресурсам внешней м .гистрали 32 по ашне .управления. Сигнал с инверсного выхода триггера 50 поступает на К-вход триггера 49,- создавая на его информационных входах логическую комбинацию 10, при которой триггер 49, с приходом следующих сигналов с линии синхронизации шины

II «И

31, останется в состоянии логической 1, а также на вход элемента И 56, блокируя поступление синхроимпульсов На триггеры 47 и 48. По завершении операции на вход 30 устройства посту- пает сигнал завершения операций от абонента, который через элемент И 54 поступает, на вход готовности формирователя управляющих сигналов 3, где формируется сигнал готовности на вход микропроцессора 1. Прохождение сигнала завершения через элемент И 55 блокировано уровнем логической с триггера 48.

Микропроцессор 1 завершает операцию обращения к ресурсам внешней магистрали 32 и снимает сигнал с входа 36, При этом уровень логического О на информационном входе триггера не изменит его состояния, так как поступление синхросигналов на его вход блокировано в элементе И 56, а на входе элемента 2И-Ш1И-НЕ 60 изменит состояние К-входа триггера 50, устанавливая на нем уровень логической 1. В соответствии с логической комбинацией на информационных входах, триггер 50 по заднему фронту синхроимпульса переключается в состояние логического О, который переводит приемопередатчик 6 в высокоимпеданс- ное состояние. Высокий уровень с инверсного выхода триггера 50 разблокирует элемент И 56 и создаст на информационных входах триггера 9 логическую комбинацию 11, При этом по

фронту следующего синхроимпульса триггеры 47 и 49 переключатся в состояние логического О, В ре эультате приемопередатчики 4 и 5 переводятся в высокоимпедансное состояние по входам разрешения и одновременно с входов выборки приемопередатчиков 4, 5, 6 снимается сигнал выборки, на информационных входах триггеров 49 и 50 устанавливаются логические комбинации 01, .запрещая их переключение при поступлении следующих синхроимпульсов, и триггер 48 разблокируется по входу. На этом цикл обращения микропроцессора 1 к ресурсам внешней магистрали 32 заканчивается, и микропроцессор 1 завершает свой цикл автономно, выполт1яя внутренние операции, Если во время работы микропроцессора 1 микропроцессор 9 сформировал внутренний запрос на линии 37 блока арбитра внутренней магистрали 24, то

15

с jg

20

25

1763110

по заднему фронту импульса синхронизации шины переключившего триггер 47, триггер 48 переключится в состояние логической 1, блокируя при этом по R-входу переключение триггера 47 и подготавливая приемопередатчики 18, 19 и 20 по входам выборки к включению на внутреннюю магистраль 26; Далее цикл обращения микропроцессора 9.к ресурсам внешней магистрали 32 происходит аналогично циклу микропроцессора 1 , Эффективность работы микропроцессора 1 и 9 в микропроцессорной системе достигается за счет того, что цикл внешней магистрали 32 значительно меньше цикла микропроцессора. Напри мер, для микропроцессора КР580ИК80А цикл составляет от 1,2 мксдо2,0 мкс (без учета тактов ожидания), в то время, как цикл внешней магистрали обычно не превьш1ает 300 не, а во многих случаях значительно меньше,

В системе каждый из микропроцессоров 1 и 9 функции подготовки в начале цикла и функции внутренней обработки в конце цикла вьтолняют авто- номно, не занимая внутренней магистрали 26 устройства и внешней магистрали 32 системы, которыми в эти моменты времени может воспользоваться второй микропроцессор, причем быстро-, действие микропроцессоров при этом

практически не снижается. I После включения питания или сигнала общего сброса ценератор 7 устройства формирует сигнал начальной установки, которым обнуляются внутренние регистры микропроцессоров. 1 и 9, регистры 2, 10 и 16, триггеры 47, 48, 49 и 50, При этом микропроцессор 1 формирует обращение к нулевой ячейке системного ПЗУ, а микропроцессор - к нулевой ячейке локального ПЗУ 14, Микропроцессор 1 приступает к выпол-- нению основной программы системы, микропроцессор 9, независимо от него, к выполнению программ контроля устройства системы.

Необходимо отметить, что программы контроля должны быть составлены таким образом, чтобы при контроле не искажалась информация в рабочих регистрах устройств ввода-вывода и в системном ОЗУ. Для этого в устройствах ввода- вывода можно предусмотреть специальные регистры состояния, а при контроле системного ОЗУ запоминать предва30

35

40

45

50

55

11

рительно содержимое контролируемых ячеек в локальном ОЗУ, при этом, учитывая, что такой контроль осуществляется за несколько циклов, необходимо приостановить работу микропроцессора 1 сигналом, с выхода регистра 16.

При обнаружении аварийной ситуации в каком-либо из устройств .систе сы, микропроцессор 9, записывая соответствующий код в регистр 16, переводит микропроцессор 1 в режим захвата, а систему в режим монопольного пользования магистралью и выполняет условный переход к подпрограмме диагностики отказавшего устройства, а в зависимости от результатов диагностики, выполняет все действия, предусмотренные в системе на случай вознпк- новения аварийной ситуации.

Формула изобрет.ения 1. Микропроцессорная система с

встроенным контролем, содержащая пер-25 рой микропроцессор, второй регистр

30

вый микропроцессор, первый регистр состояния, первый формирователь управляющих сигналов, первый и второй приемопе редатчики, первый двунаправленный приемопередатчик, тактовый генерат.ор, блок захвата магистрали, локальное постоянное запоминающее устройство, локальное оператив1 ое запоминающее устройство, причем выходная шина адреса первого микропроцессора соединена с группой информа- 35 ционных входов первого приемопередатчика, двунаправленная шина данных первого микропроцессора соединена с группой информационных входов первого регистра состояния и первой группой информационных входов-выходов первого двунаправленного приемопередатчика, вход выбора направления передачи которого соединен с выходом признака

40

состояния, второй формирователь уп- рапляющих сигналов, с третьего по седьмой приемопередатчики, со второго по четвертьй двунаправленные приемопередатчики, дешифратор, регистр, блок арбитра внутренней магистрали и коммутатор, причем тактовый вход и вход сброса второго микропроцессора соединены соответственно с выхода ми синхронизации и начальной установ ки тактового генератора, выходная шина адреса второго микропроцессора соединена с группой информационных иходов третьего приемопередатчика, двунаправленная шина данных второго микропроцессора соединена с группой информационных входов второго регист ра состояния и первой группы информа ционных входов-выходов второго двунаправленного приемопередатчика, вход

направления пер едачи первого формиро- З выбора направления передачи которого

вателя управляющих сигналов, выходная шина управления первого микропроцессора соединена с группой входов разрешения -первого формирователя управляющих сигналов, выход признака го- 50 товности которого соединен с входом готов первого микропроцессора, выходы первого регистра состояния соединены с rpyjinofi информационных входов первого формирователя управляющих55 ходы второго регистра состояния сое- сигналов, группа интерфейсных управляющих выходов первого формирователя управляющих сигналов соединена с

соединен с первым выходом признака направления передачи второго формиро вателя управляющих сигналов, выходна шина управления второго микропроцес- сора соединена с группой входов разрешения первого формирователя управ- ляющих сигналов, выход признака готовности которого соединен с входом готов второго микропроцессора, быдинены с группой информационных входов второго формирователя управляющих сигналов, группа выходов третьего

10

20

15

f,51 , 12

группой информационньгх входов второго приемопередатчика, выходы синхронизации и начальной установки тактового генератора соединены соответственно с тактовым входом и входом сброса первого микропроцессора, первый выход блока захвата магистрали является выходом запроса доступа системы, синхровход блока захвата магистрали подключен к входу внешней синхронизации системы, вход приоритетного доступа блока захвата магистрали является входом приоритетного доступа системы, вход-вькод занятости блока захвата магистрали является входом-выходом сигнала занятости внешней магистрали системы, отличающаяся тем, что, с целью повышения надежности микропроцессорной системы за счет обеспечения постоянного контроля ее компонентов независимо от загруженности основной программой, она содержит вто-

состояния, второй формирователь уп- рапляющих сигналов, с третьего по седьмой приемопередатчики, со второго по четвертьй двунаправленные приемопередатчики, дешифратор, регистр, блок арбитра внутренней магистрали и коммутатор, причем тактовый вход и вход сброса второго микропроцессора соединены соответственно с выходами синхронизации и начальной установки тактового генератора, выходная шина адреса второго микропроцессора соединена с группой информационных иходов третьего приемопередатчика, двунаправленная шина данных второго микропроцессора соединена с группой информационных входов второго регист- ра состояния и первой группы информационных входов-выходов второго двунаправленного приемопередатчика, вход

выбора направления передачи которого

ходы второго регистра состояния сое-

соединен с первым выходом признака направления передачи второго формирователя управляющих сигналов, выходная шина управления второго микропроцес- сора соединена с группой входов разрешения первого формирователя управ- ляющих сигналов, выход признака готовности которого соединен с входом готов второго микропроцессора, быходы второго регистра состояния сое-

динены с группой информационных входов второго формирователя управляющих сигналов, группа выходов третьего

ir

141765

приемопередатчика соединена с г руппа- ми информационных входов четвертого приемопередатчика и дешифратора, с группами адресных входов локального постоянного запоминающего устройства и локального оперативного запоминающего устройства, группа-интерфейсных управляющих выходов второго формирователя управляющих сигналов соедине- на с группой информационных входов пятого приемопередатчика, выход первого разряда регистра соединен с входом старшего разряда группы информационных входов четвертого приемопередатчика, выход второго разряда регистра соединен с входом захвата первого микропроцессора, выход третьего разряда регистра соединен с входом установки монопольного режима блок.а захвата магистрали-, вторая группа информационных входов-выходов второго двунаправленного приемопередатчика соединена с первой группой информационных вх одов-выходов третьего двунап- равленного приемопередатчикаj- с группой информационных выходов локального постоянного запоминающего устройства, с двyнaпpaвJJeннoй информационной шиной локального оперативного запоминающего устройства и с груйпой информа- ционных входов регистра вход сброса .которого соединен с выходом начальной установки тактового генератора, вто- . рой выход признака направления передачи второго -формирователя управляю- щих сигналов соединен с входом выбора направления передачи третьего двунаправленного приемопередатчика и с первым информационным входом коммутатора, - входы выборки локального постояннего запоминающего устройства,- локального- оперативного запоминающего устройства и регистра соединены соот- ветственно с первым, вторым и.третьим выходами-дешифратора, .выход признака записи второго формирователя управляющих сигналов соединен с входами записи локального оперативного запоминающего устройства и регистра, выход признака чтения второго формирователя управляющих сигналов соединен с вхо дом чтения локашьного постоянного запоминающего устройства, выход стар шего разряда группы выходов третьего приемопередатчика соединен с padpe- шающим входом второго формирователя управляющих сигналов, первый и второй входы внутреннего запроса блока ар

5

Q „ 5 О . 5 0 5

11 t

GjdTpa внутренней магистрали соединены с выходами пру знака запроса соответственно первого и второго формирователей управляюс I/ сигналов, .вход сброса блока арбитра внутренней магистрали соединен с выходом начальной установки тактового генератора, вы- - код разрешения блока захвата магистрали соединен с входом разрешения доступа блока арбитра внутренней магистрали, входы синхронизации и завершения операции которого подключены соответственно к входу внешней синхронизации и к входу завершения операции системы, входы выборки первого и BTQporo приемопередатчиков и первый управляющий вход коммутатора соединены с первым выходом выборки блока арбитра внутренней магистрали второй выход выборки которого сое-динен с входами выборки четвертого и пятого приемопередатчиков, третьего двунаправленного приемопередатчика и с вторым управляющим входом коммутатора, входы разрешения первого и четвертого приемопередатчиков и первого и третьего двунаправленных приемопередатчиков соединены с первым выходом разрешения блока арбитра внутренней магистрали, второй выход разрешения которого соединен с входами разрешения второго и пятого приемопередатчи ков, выход запроса блока арбитра внутренней магистрали соединен с входом запроса блока захвата магистрали, первый и второй выходы готовности блока арбитра внутренней магистрали соединены с входами готовности соответственно первого и второго формирователей управляющих сигналов, выход признака направления передачи первого формирователя управляющих сигналов соединен со вторым информационным входом коммутатора, выход которого соединен с входом выбора направления передачи четвертого двунаправленного приемопередатчиг а, группы выходов первого и четвертого приемопередатчиков образуют группу информационных входов шестого приемопередатчика, группы выходов второго и пятого приемопередатчиков образуют группу информационных входов седьмого приемопередатчика, вторые группы информационных входов-выходов первого и третьего двунаправленных приемопередатчиков образуют первую группу информационных входов-выходов четвертого дву- :

15

направленного приемопередатчика, разрешающие входы шестого и седьмого приемопередатчиков и четвертого двунаправленного приемопередатчика соединены с выходом разрешения блока- захвата магистрали, группы выходов шестого, седьмого приемопередатчиков и вторая группа информационных входов-выходов четвертого двунаправленного приемопередатчика являются соответственно выходной адресной шиной, выходной шиной управления и двунаправленной шиной данных системы.

2, Микропроцессорная система по п,1, отличаТощаяся тем, что блок арбитра внутренней магистрали содержит с первого по четвертый триггеры, три элемента ИЛИ| четыре элемента И, дна элемента НЕ и элемент 2И-ИЛИ-НЕ, причем первый вход внутреннего запроса блока арбитра внутренней магистрали подключен к D-входу первого триггера и к первому входу элемента 2И-ИЛИ-НЕ, R-вход первого триггера соединен с выходом первого элемента ИЛИ, R-вход второго триггера соединен с выходом второго элемента .ИЛИ, вход сброса блока арбитра внутренней магистрали подключен к первым входам первого и второго элементов ИЛИ и к R-входам третьего и четвертого триггеров, вход завершения операции блока арбитра внутренней магистрали подключен к прямым входам первого и второго элементов И, выход третьего элемента И соединен с С-входом второго триггера и через первый элемент НЕ с С-входом первого триггера, прямой выход.которого соединен с вторым входом второго элемента ИЛИ, вто рым входом элемента 2И-ИЛИ-НЕ, лервым входом третьего элемента ИЛИ и является первым выходом выборки блока арбитра внутренней магистрали, инвер10

15

20

1765116

cHbft выход первого триггера соединен с инверсным входом первого элемента И, выход которого является первым выходом готовности блока арбитра внутренней магистрали, прямой выход второго триггера соединен с вторым входом третьего элемента ИЛИ, третьим входом элемента 2И-ИЛИ-НЕ вторым , входом первого элемента ИЛИ и является вторым выходом выборки блока арбитра внутренней магистрали, инверсный выход второго триггера соединен с инверсным входом второго элемента И, выход которого является вторым выходом готовности блока арбитра внутренней магистрали, вход синхронизации блока арбитра внутренней магистрали Подключен к первому входу третьего элемента И, к С-входу четвертого триггера и через второй элемент НЕ-к С-входу третьего триггера, выход которого соединен с 1-входом четвертого триггера и является первым выходом разрешения блока арбитра внутренней магистрали, вторрй выход разрешения которого подключен к прямому выходу четвертого триггера, ин- версиьй выход которого соединен с К-входом третьего триггера и с вторым входом третьего элемента И, второй вход внутреннего запроса блока арбит- ра внутренней магистрали подключен к D-входу второго триггера и к четвер- TOi Tf входу элемента 2И-ИЛИ-НЕ, выход 35 которого соединен с К-входом четвертого триггера, выход третьего элемента ИЛИ соединен с первым входом четвертого элемента И и является выходом запроса блока арбитра внутренней 40 магистрали, вход разрешения доступа . подключен к второму входу четвертого элемента И, выход которого соединен с 1-входом третьего триггера.

25

30

hjy

Работа мпт

Ctfgva/ o )

JL

Обращение по нилёоомиао- ресу к системн. ПЗУ

Начальная дстаноЬка.

1гюнхить инф. Ни шинах.

1 т

нет.

0)киданае оазрешен -

Да,

Нет

Обмен с ресурсами Ьнешней магистр.

хреализания уп/кролрограммы

Работа. МП9

С дуало J

JL

Ооращение т нулевому адресу к покам ному ПЗУ

Гяо. чальная устаноока.

/ста.нодить цн/рорм. на ло- кальных шинах. 21,22,23

1

0 киданиё

Обмен с ресурсами, бнеш. магистраль

а

Joo/nff. - - Dumept/ oL

| Джерри Лаймен | |||

| Повышение надежности электронных систем военн.ого назначения | |||

| Электроника, т.58 1985, В 6, (713), с.47 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-07-15—Публикация

1986-03-26—Подача