4 СО N) Сл

СО Од

мейства микроЭВМ Электроника-60, и ориентирована на использование иниI Изобретение относится к области вычислительной техники и предназначено для создания многомашинных систем с общим полем периферийных устройств.

Цель изобретения - повышение производительности и сокращение аппаратурных затрат.

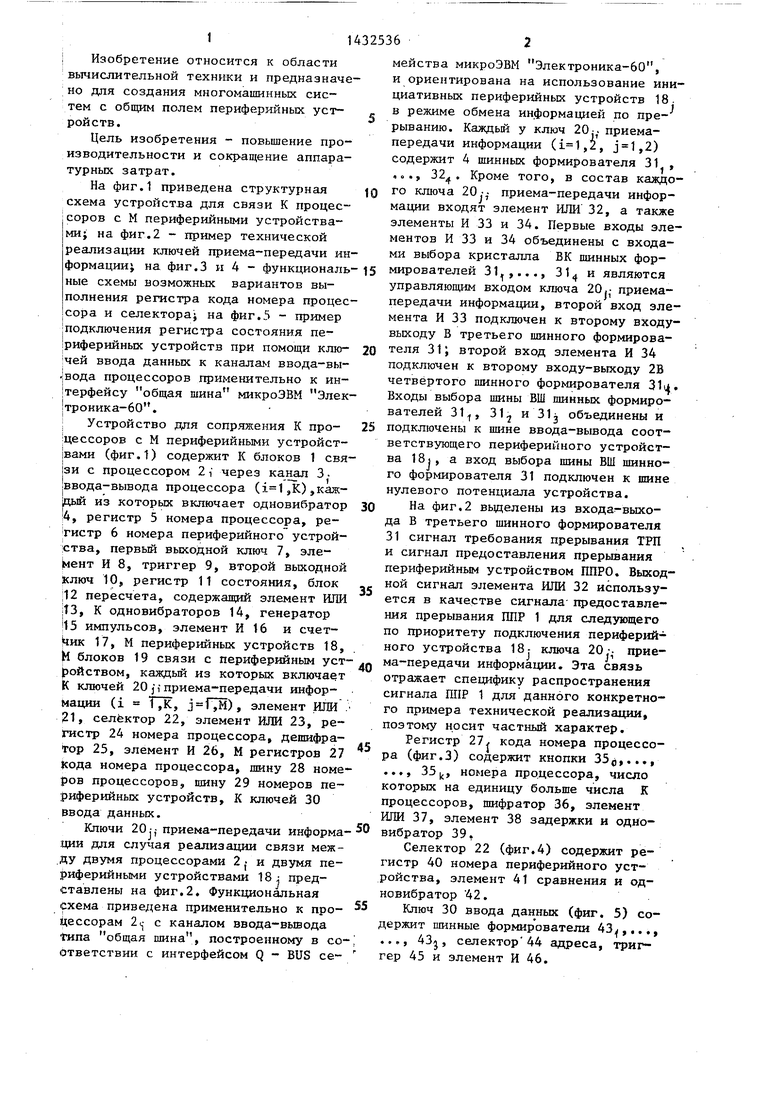

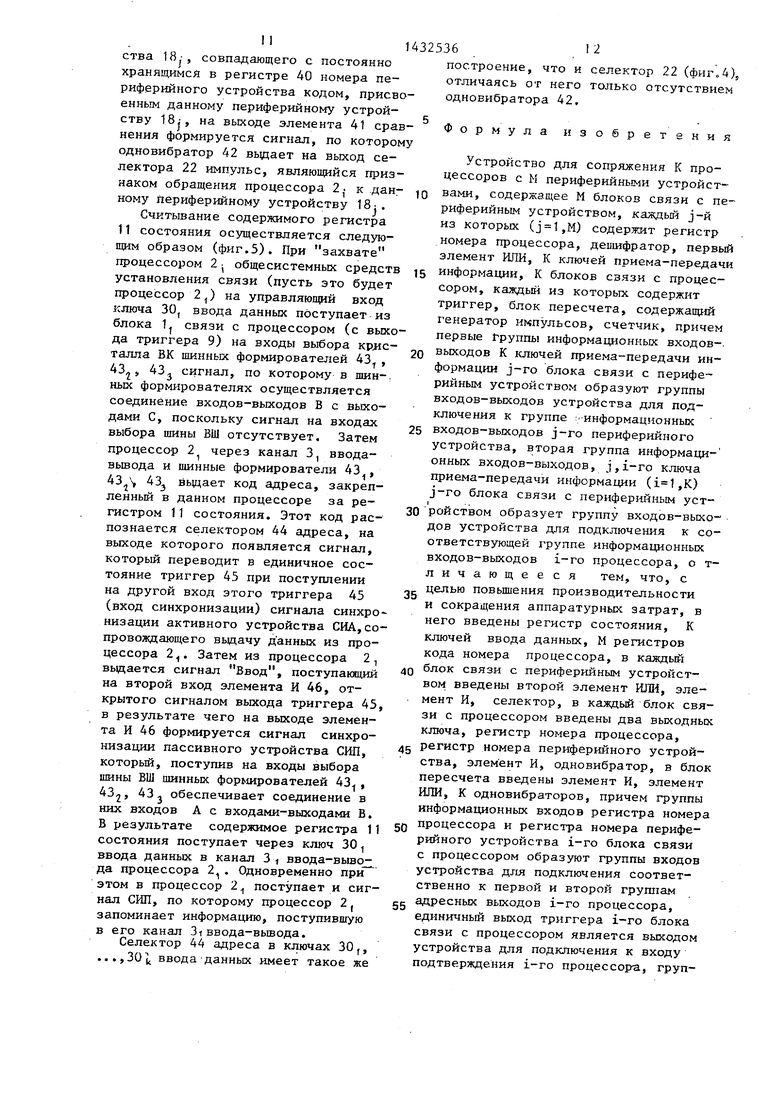

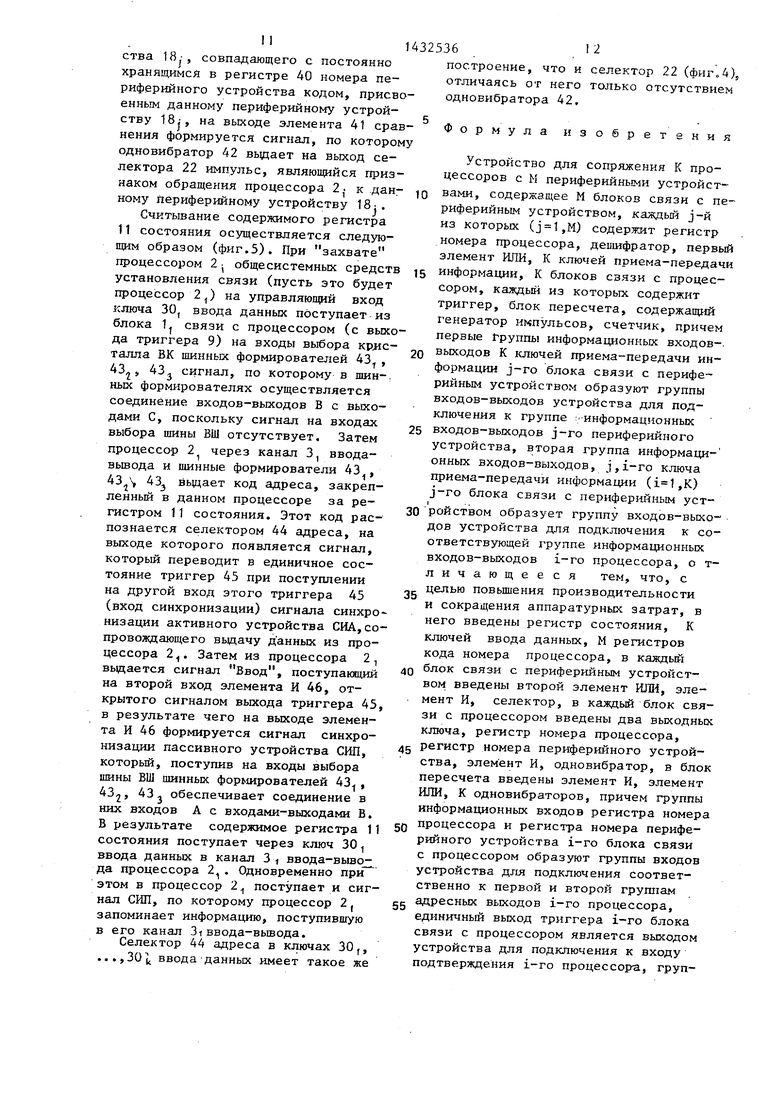

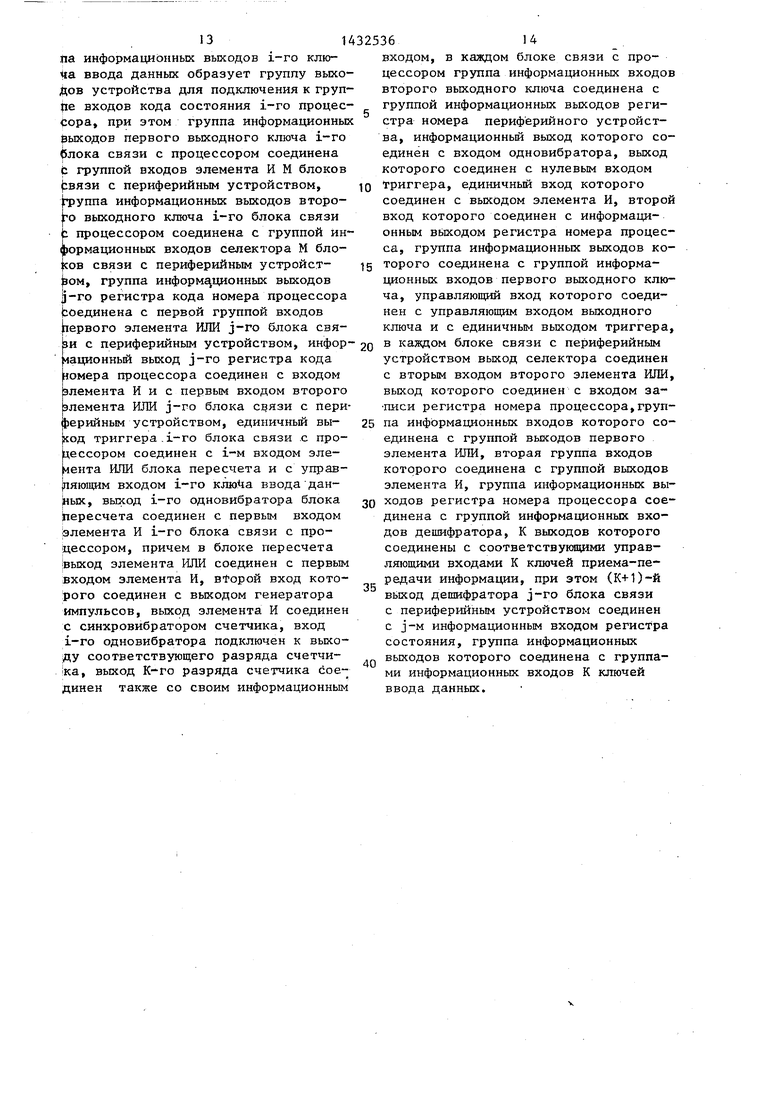

На фиг.1 приведена структурная схема устройства для связи К процес- I соров с М периферийными устройства- ми; на фиг.2 - пример технической реализации ключей приема-передачи информации; на фиг.З и 4 - функциональ- 5 мирователей 31,,..., 31 и являются ные схемы возможных вариантов выполнения регистра кода номера процес- icopa и селектора} на фиг.З - пример подключения регистра состояния пе- риферийных устройств при помощи клю- 20 чей ввода данных к каналам ввода-вы- вода процессоров применительно к ин- |терфейсу общая шина микроЭВМ Элек- |троника-60.вателей 31,,

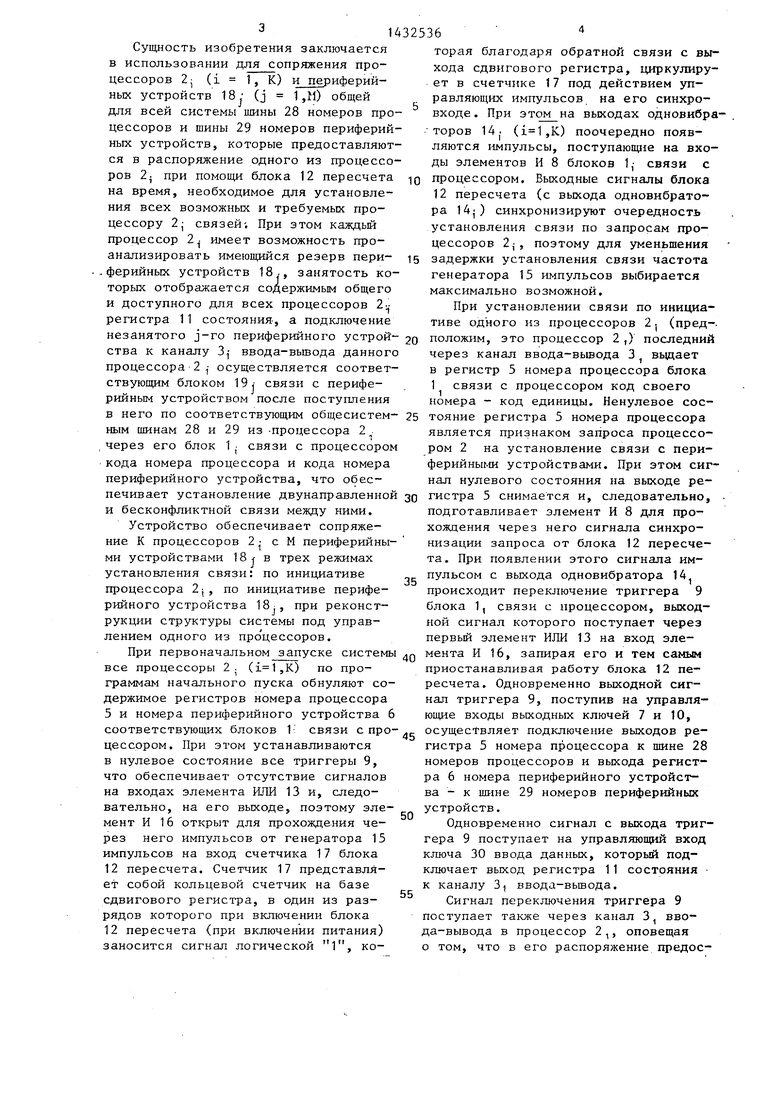

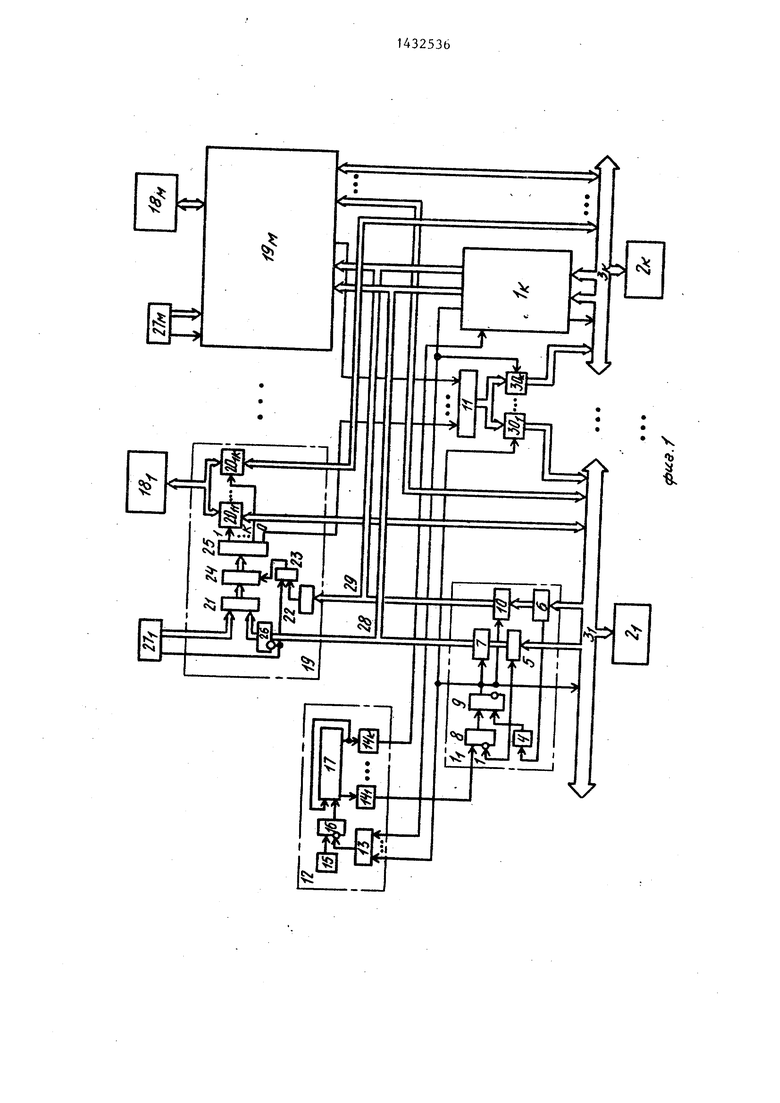

циативных периферийных устройств 18. в режиме обмена информацией по прерыванию. Каждьй у ключ 20;. приема- передачи информации (,2, ,2) содержит 4 шинных формирователя 31 , ,0., 32. Кроме того, в состав каждого ключа 20-,- приема-передачи информации входят элемент ИЛИ 32, а также элементы И 33 и 34. Первые входы элементов И 33 и 34 объединены с входами выбора кристалла ВК шинных форуправляющим входом ключа 20.- приема- передачи информации, второй вход элемента И 33 подключен к второму входу- выходу В третьего шинного формирователя 31; второй вход элемента И 34 подключен к второму входу-выходу 2В четвёртого шинного формирователя ЗЦ. Входы выбора шины ВШ шинных формиро31 и 31з

объединены и

Устройство для сопряжения К про- 25 подключены к шине ввода-вывода соот14325362

мейства микроЭВМ Электроника-60, и ориентирована на использование иниециативных периферийных устройств 18. в режиме обмена информацией по прерыванию. Каждьй у ключ 20;. приема- передачи информации (,2, ,2) содержит 4 шинных формирователя 31 , ,0., 32. Кроме того, в состав каждого ключа 20-,- приема-передачи информации входят элемент ИЛИ 32, а также элементы И 33 и 34. Первые входы элементов И 33 и 34 объединены с входами выбора кристалла ВК шинных формирователей 31,,..., 31 и являются вателей 31,,

управляющим входом ключа 20.- приема- передачи информации, второй вход элемента И 33 подключен к второму входу- выходу В третьего шинного формирователя 31; второй вход элемента И 34 подключен к второму входу-выходу 2В четвёртого шинного формирователя ЗЦ. Входы выбора шины ВШ шинных формиро1,,..., 31 и являются

31 и 31з

объединены и

шине ввода-вывода соот

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Многопроцессорная вычислительная система | 1988 |

|

SU1589287A1 |

| Устройство для контроля вычислительного процесса ЭВМ | 1988 |

|

SU1596332A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1987 |

|

SU1471198A1 |

| Устройство для управления процессом намотки | 1986 |

|

SU1390618A1 |

| Устройство для подключения абонентов к магистрали ЭВМ | 1987 |

|

SU1444795A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

35

|цессоров с М периферийными устройствами (фиг.1) содержит К блоков 1 свя- |зи с процессором 21 через канал 3 1ввода-вывода процессора (,К),каж- ЙБЙ из которых включает одновибратор 30 14, регистр 5 номера процессора, ре- гистр 6 номера периферийного устройства, первый выходной ключ 7, эле- Иент И 8, триггер 9, второй выходной ключ 10, регистр 11 состояния, блок :12 пересчета, содержащий элемент ИЛИ ;13, К одновибраторов 14, генератор |15 импульсов, элемент И 16 и счет- ик 17, М периферийных устройств 18, Н блоков 19 связи с периферийным устройством, каждьй из которых включает К ключей 20J1приема-передачи информации (i 1 ,К., j f7M), элемент ИЛИ . 21, селектор 22, элемент ИЛИ 23, регистр 24 номера процессора, дешифратор 25, элемент И 26, М регистров 27 Кода номера процессора, шину 28 номеров процессоров, шину 29 номеров периферийных устройств, К ключей 30 рвода данных.

ветствующего периферийного устройства 18I, а вход выбора шины ВШ шинного формирователя 31 подключен к шине нулевого потенциала устройства.

На фиг.2 вьщелены из входа выхо- да В третьего шинного формирователя 31 сигнал требования прерывания ТРП и сигнал предоставления прерывания периферийным устройством ППРО. Выходной сигнал элемента ИЛИ 32 используется в качестве сигнала предоставления прерывания ГШР 1 для следующего по приоритету подключения периферийного устройства 18: ключа 20; прие- д- ма-передачи информации. Эта связь отражает специфику распространения сигнала 1ШР 1 для данного конкретного примера технической реализации, поэтому носит частный характер.

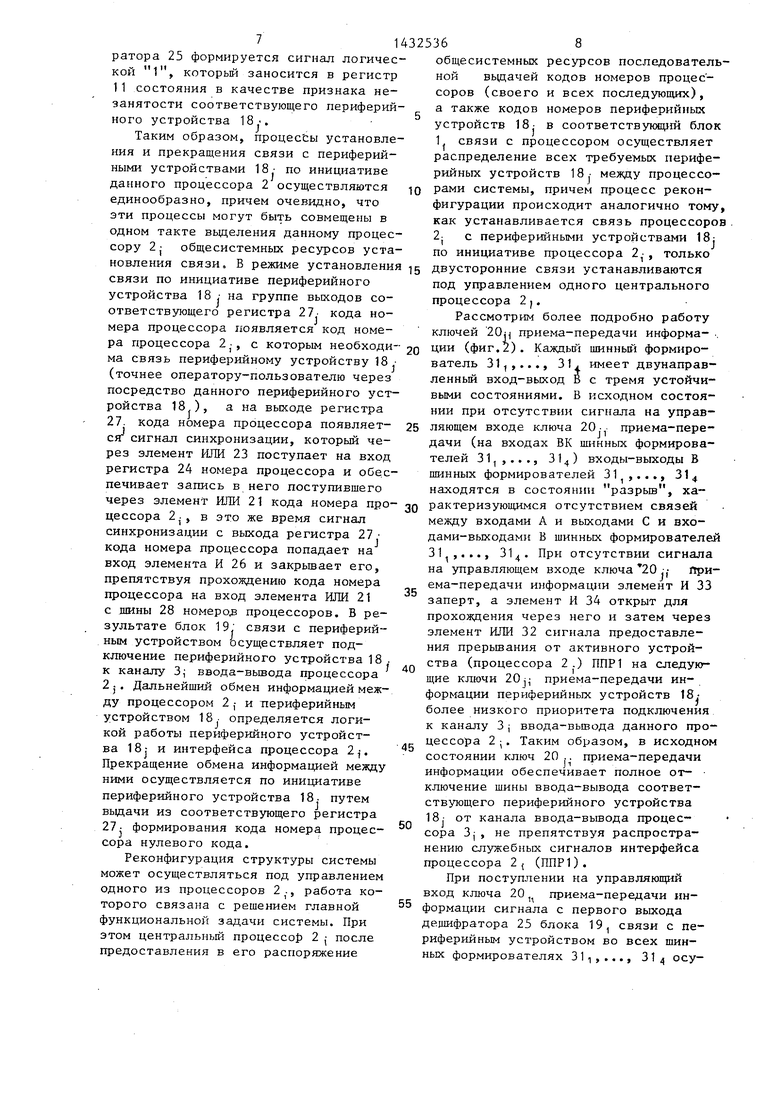

Регистр 27. кода номера процессо/ лп г

45

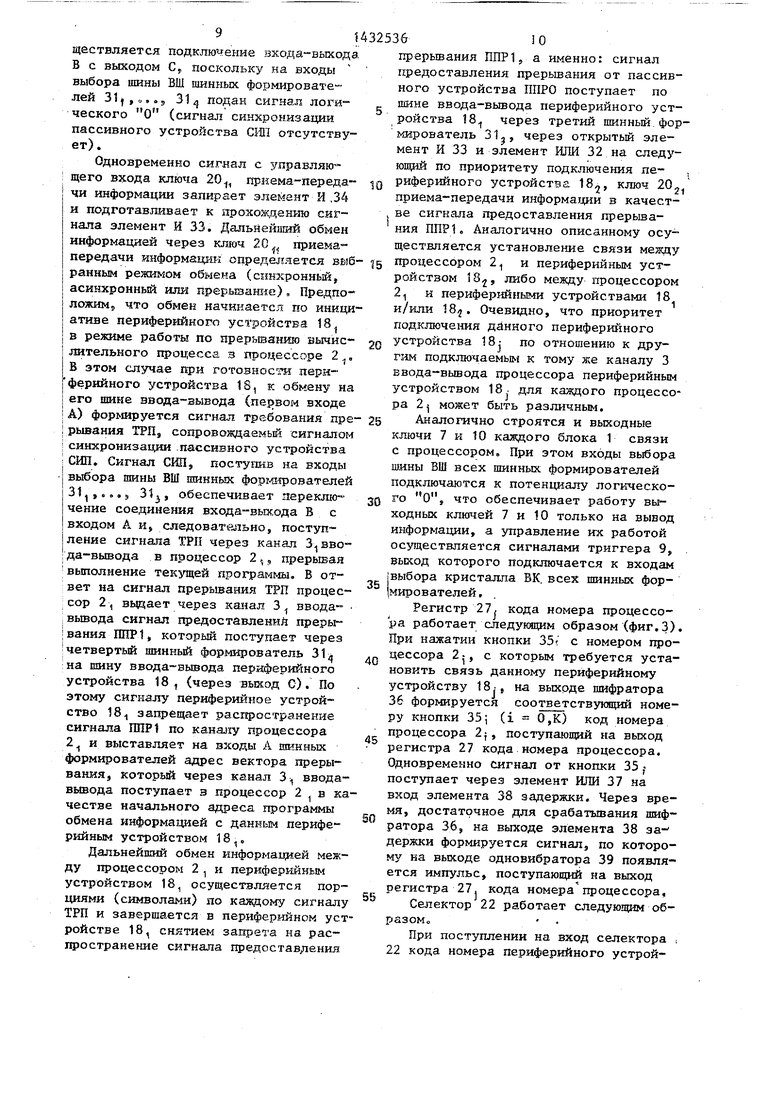

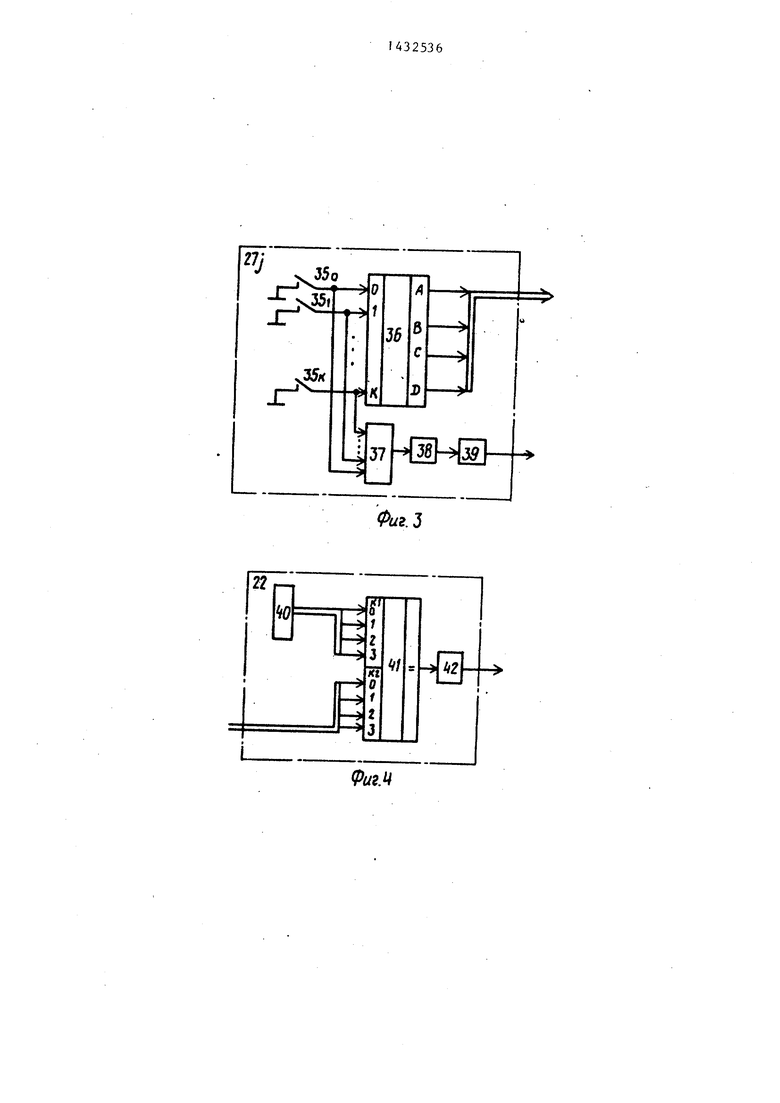

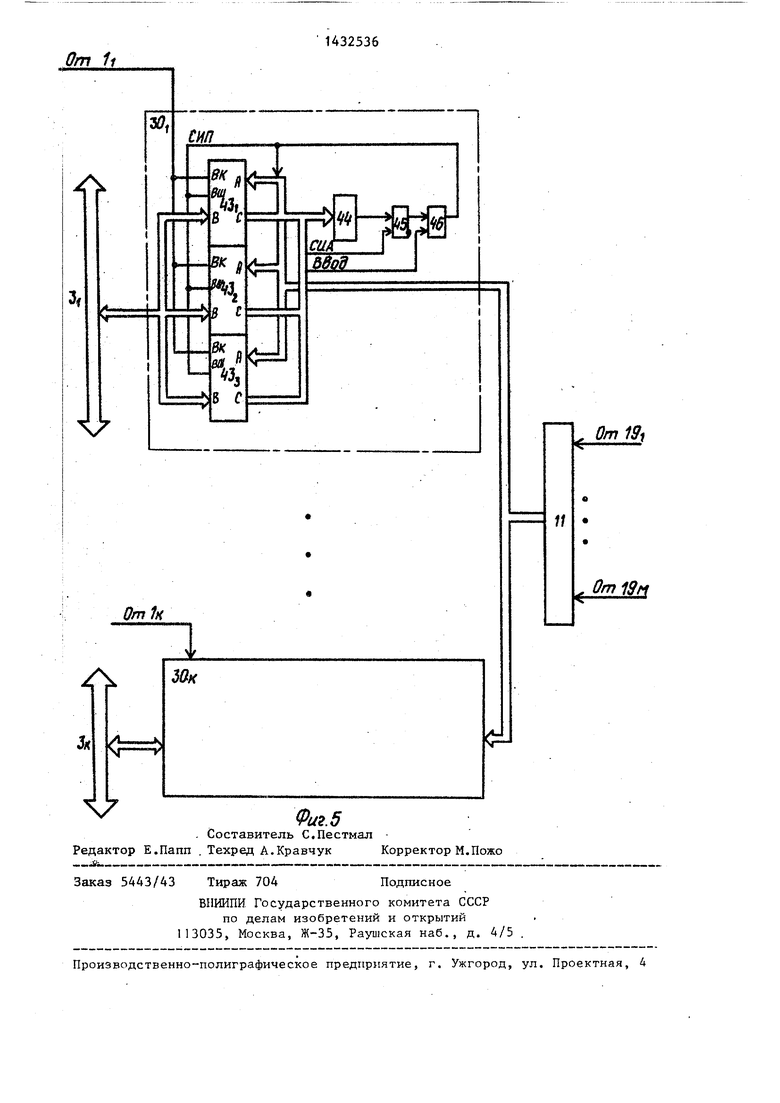

ра (фиг.З) содержит кнопки 35,,..., ..., 351, номера процессора, число которых на единицу больше числа К процессоров, шифратор 36, элемент ИЛИ 37, элемент 38 задержки и одноКлючи 20;,-приема-передачи информа- вибратор 39, ции для случая реализации связи меж- Селектор 22 (фиг.4) содержит раду двумя процессорами 2 и двумя пе-гистр 40 номера периферийного уст- риферийными устройствами 18j пред-ройства, элемент 41 сравнения и од- ставлены на фиг.2, Функциональнаяновибратор 42.

«Л

схема приведена применительно к процессорам 2i; с каналом ввода-вьшода типа общая шина, построенному в со-, ответствии с интерфейсом Q - BUS сеКлюч 30 ввода (фиг. 5) содержит шинные формирователи 43,,.., ..,, 43j, селектор 44 адреса, триггер 45 и элемент И 46,

5

0

ветствующего периферийного устройства 18I, а вход выбора шины ВШ шинного формирователя 31 подключен к шине нулевого потенциала устройства.

На фиг.2 вьщелены из входа выхо- да В третьего шинного формирователя 31 сигнал требования прерывания ТРП и сигнал предоставления прерывания периферийным устройством ППРО. Выходной сигнал элемента ИЛИ 32 используется в качестве сигнала предоставления прерывания ГШР 1 для следующего по приоритету подключения периферийного устройства 18: ключа 20; прие- - ма-передачи информации. Эта связь отражает специфику распространения сигнала 1ШР 1 для данного конкретного примера технической реализации, поэтому носит частный характер.

Регистр 27. кода номера процессо/ лп г

5

ра (фиг.З) содержит кнопки 35,,..., ..., 351, номера процессора, число которых на единицу больше числа К процессоров, шифратор 36, элемент ИЛИ 37, элемент 38 задержки и одно вибратор 39, Селектор 22 (фиг.4) содержит рагистр 40 номера периферийного уст- ройства, элемент 41 сравнения и од- новибратор 42.

Ключ 30 ввода (фиг. 5) содержит шинные формирователи 43,,.., ..,, 43j, селектор 44 адреса, триггер 45 и элемент И 46,

Супщость изобретения заключается в использовании для сопряжения процессоров 2j (i 1, К) и периферий- ных устройств 18; (j 1,М) общей для всей системы шины 28 номеров процессоров и шины 29 номеров периферийных устройств, которые предоставляются в распоряжение одного из процессоров 2- при помощи блока 12 пересчета на время, необходимое для установления всех возможных и требуемых процессору 2j связей; При этом каждьй процессор 2 имеет возможность проанализировать имеющийся резерв пери- . ферийных устройств 18,, занятость которых отображается содержимьм общего и доступного для всех процессоров регистра 11 состояния, а подключение

процессора 2 - осуществляется соответствующим блоком 19 связи с периферийным устройством после поступления

незанятого j-ro периферийного устрой- 2о положим, это процессор 2 ,) последний ства к каналу 3,- ввода-вьтода данного через канал ввода-вьшода 3, вьщает

в регистр 5 номера процессора блока 1 связи с процессором код своего номера - код единицы. Ненулевое сос- в него по соответствующим общесистем- 25 тояние регистра 5 номера процессора ным шинам 28 и 29 из -процессора 2, через его блок 1 связи с процессором кода номера процессора и кода номера периферийного устройства, что обеспечивает установление двунаправленной зо гистра 5 снимается и, следовательно,

подготавливает элемент И 8 для прохождения через него сигнала синхронизации запроса от блока 12 пересчета. При появлении этого сигнала им- „. пульсом с выхода одновибратора 14,

OD

является признаком запроса процессором 2 на установление связи с пери- фepийны и устройствами. При этом сигнал нулевого состояния на выходе реи бесконфликтной связи между ними.

Устройство обеспечивает сопряжение К процессоров 2 - с М периферийны45

ми устройствами 18j в трех режимах установления связи: по инициативе процессора 2|, по инициативе периферийного устройства 18., при реконструкции структуры системы под управлением одного из про цессоров.

При первоначальном запуске системы Q все процессоры 2; (,К) по программам начального пуска обнуляют содержимое регистров номера процессора 5 и номера периферийного устройства 6 cooтвeтcтвyюш x блоков 1- связи с процессором. При этом устанавливаются в нулевое состояние все триггеры 9, что обеспечивает отсутствие сигналов на входах элемента ИЛИ 13 и, следовательно, на его выходе, поэтому элемент И 16 открыт для прохождения через него импульсов от генератора 15 импульсов на вход счетчика 17 блока 12 пересчета. Счетчик 17 представляет собой кольцевой счетчик на базе сдвигового регистра, в один из разрядов которого при включении блока 12 пересчета (при включении питания) заносится сигнал логической 1, ко50

55

происходит переключение триггера 9 блока 1, связи с процессором, выходной сигнал которого поступает через первый элемент ИЛИ 13 на вход элемента И 16, запирая его и тем самым приостанавливая работу блока 12 пересчета. Одновременно выходной сигнал триггера 9, поступив на управляющие входы выходных ключей 7 и 10, осуществляет подключение выходов регистра 5 номера процессора к шине 28 номеров процессоров и вьпсода регистра 6 номера периферийного устройства - к шине 29 номеров периферийных устройств.

Одновременно сигнал с выхода триггера 9 поступает на управляющий вход ключа 30 ввода данных, который подключает выход регистра 11 состояния к каналу 3 ввода-вьшода.

Сигнал переключения триггера 9 поступает также через канал 3, ввода-вывода в процессор 2,, оповещая о том, что в его распоряжение предосторая благодаря обратной связи с выхода сдвигового регистра, циркулирует в счетчике 17 под действием управляющих импульсов на его синхро- входе. При этом на выходах одновибра- торов 14f (,K) поочередно появляются импульсы, поступающие на входы элементов И 8 блоков связи с

процессором. Выходные сигналы блока 12 пересчета (с выхода одновибрато- ра 14|) синхронизируют очередность установления связи по запросам процессоров 2j, поэтому для уменьшения

задержки установления связи частота генератора 15 импульсов выбирается максимально возможной.

При установлении связи по инициативе одного из процессоров 2. (пред-.

в регистр 5 номера процессора блока 1 связи с процессором код своего номера - код единицы. Ненулевое сос- тояние регистра 5 номера процессора гистра 5 снимается и, следовательно,

является признаком запроса процессором 2 на установление связи с пери- фepийны и устройствами. При этом сигнал нулевого состояния на выходе ре

происходит переключение триггера 9 блока 1, связи с процессором, выходной сигнал которого поступает через первый элемент ИЛИ 13 на вход элемента И 16, запирая его и тем самым приостанавливая работу блока 12 пересчета. Одновременно выходной сигнал триггера 9, поступив на управляющие входы выходных ключей 7 и 10, осуществляет подключение выходов регистра 5 номера процессора к шине 28 номеров процессоров и вьпсода регистра 6 номера периферийного устройства - к шине 29 номеров периферийных устройств.

Одновременно сигнал с выхода триггера 9 поступает на управляющий вход ключа 30 ввода данных, который подключает выход регистра 11 состояния к каналу 3 ввода-вьшода.

Сигнал переключения триггера 9 поступает также через канал 3, ввода-вывода в процессор 2,, оповещая о том, что в его распоряжение предоставлены общесистемные средства системы. По этому сигналу процессор 2 считывает содержимое регистра 11 сос : тояния и анализирует содержимое разрядов, закрепленных за периферийными устройствами 18-, с которыми процессору 2 требуется установить связь. :Если эти устройства не заняты, приз- ;наком чего является наличие логичес- I кой 1 в соответствующих разрядах I регистра 1 состояния, то процессор |2 последовательно задает через ка- j нал 3 ввода-вьтода в регистр 6 но мера периферийного устройства коды I номеров требуемых процессору 2 пе- |риферийных -устройств 18,. Предполо- |Жим, что процессору 2, требуется не- :занятое другим процессорами 2у (i И 2,К) периферийное устройство 18,. 1Тогда он вьщает в регистр 6 номера периферийного устройства блока 1 |связи с процессором код единицы, ко- |торый поступает через открЪ1тьй вы- |ходной ключ 10 на шину 28 номеров периферийных устройств. Этот код распознается селектором 22 блока 19 ;Связи с периферийным устройством, ;На выходе селектора 22 формируется римпульс, которьй через элемент ИЛИ рЗ поступает на вход регистра 24 Номера процессора и синхронизирует запись в него кода номера первого оцессора 2, поступающего на информационный вход регистра 24 номе- jpa процессора с шинь 28 номеров процессоров через элемент ИЛИ 21. В со- Ьтветствии с кодом номера 2 на пер- вом выходе дешифратора 25 появляется сигнал логической 1, поступаю- 1ций на управляющий вход ключа приема йередачи информации 20, , по которому ключ приема-передачи информации 20 осуществляет подключение 1аины йвода-вывода периферийного устройства 18 к каналу 3 ввода-вьгоода Процессора 2 . Одновременно на (К+1)-м выходе дешифратора 25 появ- .пяется сигнал логического О поступающий в виде признака занятости периферийного устройства 18 в регистр 11 состояния. На этом сопряжение периферийного устройства 18, С процессором 2, завершается и даль нейюий обмен информацией между ними ведется по правилам интерфейса процессора 2,

Аналогично устанавливается связь процессора 2 и с другими периферий

5

0

5

0

5

0

5

0

5

ными устройствами 18- (j 2,М) последовательной выдачей кЬдов их номеров в регистр 6 номера периферийного устройства Из следовательно, на общесистемную шину 28 номеров периферийных устройств. После установления двусторонней связи с требуемым процессору 2 периферийным устройст- вом он освобождает общесистемные средства следующим образом: сначала процессор 2 выдает в первьй регистр 5 номера процессора нулевой код, сигнал признака которого запирает элемент И 8, затем процессор 2, заносит в регистр 6 номера периферийного устройства нулевой код, по сигналу признака которого одновибратор 4 формирует сигнал, переключающий в нулевое состояние триггер 9. Последний, переключившись, запирает первой 7 и второй 10 выходные ключи осво- бояодая тем самым шины номеров процессоров 28 и периферийных устройств 29.Одновременно сигнал переключения триггера 9 через элемент ШШ 13 открывает элемент И 16 для прохождения импульсов синхронизации на вход счетчика 17 и разрешает тем самым дальнейшую работу блока 12 пересчета.

Сопряжение других процессоров 2,- с оставшимися свободными периферийными устройствами 18.- осуществляется аналогично описанному.

Аналогично описанному осуществляется и освобождение периферийных устройств 18.- по инициативе процессора 2, после завершения обмена информа-. цией между ними. При этом процессор вьщает в регистр 5 номера процессора код своего номера, а после предоставления в его распоряжение общесистемных средств установления связей выдает в этот же регистр 5 нулевой код, а в регистр 6 номера периферийного устройства - последовательность кодов номеров освобожденнмк процессором 2j периферийных устройств 18 , В результате во все регистры 24 номера процессора блоков l9j связи с осво- бояздаемыми периферийными устройства- ми 18) заносится нулевой код, по которому на (1-К)-м выходах дешифрато- ра 25 сигналы логической 1 снимаются, чем обеспечивается отключение ключами - 20,,... 20 | приема-передачи информации периферийных устройств 18i от каналов 3 -ввода-вывода процессоров 2,, на (К+1)-м выходе дещифратора 25 формируется сигнал логической 1, который заносится в регистр 11 состояния в качестве признака незанятости соответствующего периферийного устройства 18.

Таким образом, процессы установления и прекращения связи с периферийными устройствами 18- по инициативе данного процессора 2 осуществляются единообразно, причем очевидно, что эти процессы могут быть совмещены в одном такте вьщеления данному процессору 2 общесистемных ресурсов уста10

общесистемных ресурсов последовател ной вьщачей кодов номеров процессоров (своего и всех последующих), а также кодов номеров периферийных устройств 18- в соответствующий бло 1 связи с процессором осуществляет распределение всех требуемых перифе рийных устройств 18/ между процессо рами системы, причем процесс реконфигурации происходит аналогично том как устанавливается связь процессор

2j с периферийными устройствами 18 по инициативе процессора 2-, только

новления связи, В режиме установления 5 двусторонние связи устанавливаются

связи по инициативе периферийного

под управлением одного центрального процессора 2),

устройства 18; на группе вькодов соответствующего регистра 27- кода номера процессора появляется код номера процессора 2-, с которым необходима связь периферийному устройству 18 (точнее оператору-пользователю через посредство данного периферийного устройства 18 ), а на выходе регистра 27. кода номера процессора появляется сигнал синхронизации, который через элемент ИЛИ 23 поступает на вход регистра 24 номера процессора и обеспечивает запись в него поступившего через элемент ИЛИ 21 кода номера процессора 2j, в это же время сигнал синхронизации с выхода регистра 27 кода номера процессора попадает на вход элемента И 26 и закрьшает его, препятствуя прохождению кода номера процессора на вход элемента ИЛИ 21 с шины 28 номеров процессоров. В результате блок 19 связи с периферийным устройством осуществляет подключение периферийного устройства 18 ,. к каналу 3, ввода-вьшода процессора 2;. Дальнейший обмен информацией между процессором 2 ,- и периферийным устройством 18 . определяется логикой работы периферийного устройства 18: и интерфейса процессора 2,-. Прекращение обмена информацией между ними осуществляется по инициативе периферийного устройства 18. путем выдачи из соответствующего регистра 27- формирования кода номера процессора нулевого кода.

Реконфигурация структуры системы может осуществляться под управлением одного из процессоров 2., работа которого связана с решением главной функциональной задачи системы. При этом центральный процессор 2 j после предоставления в его распоряжение

;

общесистемных ресурсов последовательной вьщачей кодов номеров процессоров (своего и всех последующих), а также кодов номеров периферийных устройств 18- в соответствующий блок 1 связи с процессором осуществляет распределение всех требуемых периферийных устройств 18/ между процессорами системы, причем процесс реконфигурации происходит аналогично тому, как устанавливается связь процессоров.

0

под управлением одного центрального процессора 2),

Рассмотрим более подробно работу ключей 20;j приема-передачи информа- .. ции (фиг./). Каждьп шинный формирователь 31,,..., 31, имеет двунаправ- ленньй вход-выход В с тремя устойчивыми состояниями. В исходном состоянии при отсутствии сигнала на управ- 5 ляющем входе ключа 20. приема-передачи (на входах ВК шинных формирователей 31,,..., 31) входы-выходы В

шинных формирователей 31, находятся в

состоянии разрьш.

314

ха

30

35

40

45

50

55

рактеризующимся отсутствием связей между входами А и выходами С и входами-выходами В шинных формирователей 31 ,..., 314 При отсутствии сигнала на управляющем входе ключа 20 .-, Приема-передачи информации элемент И 33 заперт, а элемент И 34 открыт для прохождения через него и затем через элемент ИЛИ 32 сигнала предоставления прерьшания от активного устройства (процессора 2.) ППР1 на следующие ключи 20jj приема-передачи ин- формации периферийных устройств 18.- более низкого приоритета подключения к каналу 3 , ввода-вьшода данного процессора 2;. Таким образом, в исходном состоянии ключ 20 ,. приема-передачи информации обеспечивает полное от- ключение шины ввода-вывода соответствующего периферийного устройства 18; от канала ввода-вывода процессора 3j, не препятствуя распространению служебных сигналов интерфейса процессора 2( (ППР1).

При поступлении на управляющий вход к.точа 20 приема-передачи информации сигнала с первого выхода дешифратора 25 блока 19, связи с периферийным устройством во всех шинных формирователях 31, ..., 31 осуществляется подключение входа-выхода В с выходом Cj поскольку на входы выбора шины ВШ шинньгх формирователей 31,0,.5 31 подан сигнал логического О (сигнал синхронизации пассивного устройства СШ1 отсутствует).

Одновременно сигнал с управляю™ щего входа ключа 20, приема-переда I чи информации запирает элемент И ,34 и подготавливает к прохождению сигнала элемент И 33. Дальйейзиий обмен I информацией через ключ 20,, приемапрерывания nnPlj а именно: сигнал предоставления прерывания от пассивного устройства ППРО поступает по шине ввода-вывода периферийного устройства 18 через третий шинный фор мирователь 31-, через открытый элемент И 33 и элемент РШИ 32 на следующий по приоритету подключения ле- риферийного устройства IS, ключ 20 приема-передачи информации в качестве сигнала предоставления прерывания ППР1, Аналогично описанному осуществляется установление связи межцу

20

передачи информад1-ш определяется fg процессором 2 и периферийным уст- ранным режимом обмена (слнхронньй,

i асинхронный ИЛИ прерьпзанне), Предположим;, что обмен начинается по инициI ативе периферийного устройства 18

I в режиме работы по прерыванию вычис лительного процесса з процессоре 2 , В этом случае при готовности периферийного устройства IS, к обмену на

i его шине ввода-вывода (перовом входе

I А) фop шpyeтcя сигнал требования пре- 25

I рывания ТРП, сопровойщаемьй сигналом

Гсинхронизации .пассивного устройства

СИП. Сигнал СИП, поступив на входы I выбора шины ВШ шинных формирователей 31,.,,, 31, обеспечивает переклю- чение соединения входа-вьжода В с I входом Аи, следовательно, поступление сигнала ТРП через канал I да-вывода в процессор 2 ,,, прерывая ;выполнение текущей программы, В ответ на сигнал прерьшания ТРП процес- :сор 2, вьщает через канал 3 ввода- ;вывода сигнал предоставлений преры- Iвания Ш1Р1J который поступает через четвертьй шинньй формирователь 31 :на шину ввода-вывода периферийного устройства 18, (через выход С), По этому сигналу периферийное устройство 18 запрещает распространение сигнала 1ШР1 по каналу процессора

30

35 i

ройством ISj, либо между процессором 2 и периферийньми устройствами 18 и/или 18. Очевидно, что приоритет подключения денного периферийного устройства 18; по отношению к другим подключаемьм к тому же каналу 3 ввода-вывода процессора периферийным устройством 18. для каждого процессо ра 2 может быть различным.

Аналогично строятся и выходные ключи 7 и 10 каждого блока 1 связи с процессором. При этом входы выбора шины ВШ всех шинных формирователей подключаются к потенциалу логического О, что обеспечивает работу выходных ключей 7 и 10 только на вывод информации, а управление их работой осуществляется сигналами триггера 9, выход которого подключается к входам выбора кристалла ВК. всех шинных фор40

45

|мирователей.

Регистр 27, кода номера процессора работает следу1сяцим образом (фиг.3 При нажатии кнопки 35; с номером про цессора 2:, с которым требуется уста новить связь данному периферийному устройству 18, на выходе шифратора 36 формируется соответствукиций номе ру кнопки 35i (i - О,К) код номера процессора 2|, поступающий на выход регистра 27 кода номера процессора. Одновременно сигнал от кнопки 35 , поступает через элемент ИЛИ 37 на вход элемента 38 задержки. Через вре мя, достаточное для срабатывания шиф ратора 36, на выходе элемента 38 задержки формируется сигнал, по которо му на выходе одновибратора 39 появля ется импульс, поступающий на выход регистра 27. кода номера процессора,

2 И выставляет на входы А шинных формирователей адрес вектора прерывания, который через канал 3, ввода- вывода поступает з процессор 2 , в качестве начального адреса программы обмена информацией с данным периферийным устройством 18,.

Дальнейший обмен информащгей между процессором 2 , и периферийным устройством 18, осуществляется порциями (cимвoлa ш) по ка;едому сигналу ТРП и завершается в периферийном устройстве 18, снятием запрета на распространение сигнала предостав/1ения

прерывания nnPlj а именно: сигнал предоставления прерывания от пассивного устройства ППРО поступает по шине ввода-вывода периферийного устройства 18 через третий шинный формирователь 31-, через открытый элемент И 33 и элемент РШИ 32 на следующий по приоритету подключения ле- , риферийного устройства IS, ключ 20 приема-передачи информации в качестве сигнала предоставления прерывания ППР1, Аналогично описанному осуществляется установление связи межцу

процессором 2 и периферийным уст-

i

ройством ISj, либо между процессором 2 и периферийньми устройствами 18 и/или 18. Очевидно, что приоритет подключения денного периферийного устройства 18; по отношению к другим подключаемьм к тому же каналу 3 ввода-вывода процессора периферийным устройством 18. для каждого процессора 2 может быть различным.

Аналогично строятся и выходные ключи 7 и 10 каждого блока 1 связи с процессором. При этом входы выбора шины ВШ всех шинных формирователей подключаются к потенциалу логического О, что обеспечивает работу выходных ключей 7 и 10 только на вывод информации, а управление их работой осуществляется сигналами триггера 9, выход которого подключается к входам выбора кристалла ВК. всех шинных фор

|мирователей.

Регистр 27, кода номера процессора работает следу1сяцим образом (фиг.3). При нажатии кнопки 35; с номером процессора 2:, с которым требуется установить связь данному периферийному устройству 18, на выходе шифратора 36 формируется соответствукиций номеру кнопки 35i (i - О,К) код номера процессора 2|, поступающий на выход регистра 27 кода номера процессора. Одновременно сигнал от кнопки 35 , поступает через элемент ИЛИ 37 на вход элемента 38 задержки. Через время, достаточное для срабатывания шифратора 36, на выходе элемента 38 за держки формируется сигнал, по которому на выходе одновибратора 39 появляется импульс, поступающий на выход регистра 27. кода номера процессора,

Селектор 22 работает следующим образом

При поступлении на вход селектора , 22 кода номера периферийного устройства 18.- , совпадающего с постоянно хранящимся в регистре 40 номера периферийного устройства кодом, присвоенным данному периферийному устройству 18;, на выходе элемента 41 сравнения формируется сигнал, по которому одновибратор 42 вьщает на выход селектора 22 импульс, являющийся признаком обращения процессора 2 к данj .

ному периферийному устройству 18

Считывание содерткимого регистра 11 состояния осуществляется следующим образом (фиг.5). При захвате процессором 2j общесистемных средст установления связи (пусть это будет процессор 2 ) на управляющий вход ключа 30, блока 1

, ввода данных поступает из связи с процессором (с выхда триггера 9) на входы выбора крлс талла ВК шинных формирователей 43,, , 43-, 43- сигнал, по которому в шинных формирователях осуществляется соединение входов-выходов В с вьгхо- дами С, поскольку сигнал на входах выбора шины ВШ отсутствует. Затем процессор 2 через канал 3, ввода- вьшода и шинные формирователи 43., 43 -, 43j вьщает код адреса, закреп- ленньш в данном процессоре за регистром 11 состояния. Этот код распознается селектором 44 адреса, на выходе которого появляется сигнал, который переводит в единичное состояние триггер 45 при поступлении на другой вход этого триггера 45 (вход синхронизации) сигнала синхронизации активного устройства СИЛ,сопровождающего вьщачу д анньк из процессора 2. Затем из процессора 2, вьдается сигнал Ввод, поступакиций на второй вход элемента И 46, открытого сигналом выхода триггера 45, в результата чего на выходе элемента И 46 формируется сигнал синхронизации пассивного устройства СИП, который, поступив на входы выбора щины ВШ шинных фop шpoвaтeлeй 43., , 43,

них входов

в результате содержимое регистра 11 состояния поступает через ключ 30 .| ввода данных в канал 3 ввода-вьшр да процессора 2. Одновременно при этом в процессор 2., поступает и сигнал СИП, по которому процессор 2, запоминает информацию, поступившую в его канал 3iввода-вьшода.

Селектор 44 адреса в ключах 30,, ...,30(j ввода данных имеет такое же

43 J обеспечивает соединение в А с входами-выходами В.

j .

у

1432536,1

построение, что и селектор 22 (фиг„4)5 отличаясь от него только отсутствием одновибратора 42.

овмуg

Формула изобретения

Устройство для сопряжения К процессоров с М периферийными устройство вами, содержащее М блоков связи с пе- риферийным устройством, каждьй j-й из которых (,M) содержит регистр номера процессора, дешифратор, первьй элемент ИЛИ, К ключей приема-передачи информации, К блоков сзязи с процессором, каждый из которых содержит триггер, блок пересчета, содержащий генератор импульсов, счетчик, причем первые Группы информационных входов-. 20 выходов К ключей приема-передачи информации j-ro блока связи с периферийным устройством образуют группы входов-выходов устройства для подключения к группе :/информационных 25 входов-выходов j-ro периферийного устройства, вторая группа информаци- онных входов-выходов, j,i-ro ключа приема-передачи информации (,К) j-ro блока связи с периферийным уст- 30 ройством образует группу входов-выходов устройства для подключения к соответствующей группе информационных входов-выходов i-ro процессора, о т- личающее ся тем, что, с целью повьшения производительности и сокращения аппаратурных затрат, в него введены регистр состояния, К ключей ввода данных, М регистров кода номера процессора, в каждый блок связи с периферийным устройством введены второй элемент ИЛИ, эле- мент И, селектор, в каждый блок связи с процессором введены два выходных ключа, регистр номера процессора, д регистр номера периферийного устройства, элемент И, одновибратор, в блок пересчета введены элемент И, элемент ИЛИ, К одновибраторов, причем группы информационных входов регистра номера процессора и регистра номера периферийного устройства i-ro блока связи с процессором образуют группы входов устройства дл ш подключения соответственно к первой и второй группам адресных выходов i-ro процессора, единичный выход триггера i-ro блока связи с процессором является выходом устройства для подключения к входу подтверждения i-ro процессора, груп35

40

50

55

па информационных выходов i-ro ключа ввода данных образует группу выходов устройства для подключения к группе входов кода состояния i-ro процессора, при этом группа информационны рыходов первого выходного ключа i-ro блока связи с процессором соединена с группой входов элемента И М блоков :вязи с периферийньм устройством, труппа информационных выходов второго выходного ключа i-ro блока связи : процессором соединена с группой информационных входов селектора М бло- ов связи с периферийным устройст- ом, группа информационных выходов регистра кода номера процессора Ьоединена с первой группой входов Ьервого элемента ИЛИ j-ro блока свя- Ьи с периферийным устройством, инфор | ационный выход j-ro регистра кода JHOMepa процессора соединен с входом элемента И и с первым входом второго элемента ИЛИ j-ro блока сдязи с периферийным устройством, единичньй вы- код триггера .i-ro блока связи .с профессором соединен с i-м входом эле- ента ИЛИ блока пересчета и с управ- |ляющим входом i-ro ввода данных, выход i-ro одновибратора блока Пересчета соединен с первым входом элемента И i-ro блока связи с про- дессором, причем в блоке пересчета выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого соединен с вькодом генератора импульсов, выход элемента И соединен с синхровибратором счетчика, вход i-го одновибратора подключен к выходу соответствующего разряда счетчи- ка, выход К-го разряда счетчика соединен также со своим информационным

5

о

5

0

5

0

ВХОДОМ, в каждом блоке связи с процессором группа информационных входов второго выходного ключа соединена с группой информационных выходов регистра номера периферийного устройства, информационньй выход которого соединен с входом одновибратора, выход которого соединен с нулевым входом Триггера, единичный вход которого соединен с выходом элемента И, второй вход которого соединен с информационным выходом регистра номера процесса, группа информационных выходов которого соединена с группой информационных входов первого выходного ключа, управляющий вход которого соединен с управляющим входом выходного ключа и с единичным выходом триггера, в каждом блоке связи с периферийным устройством выход селектора соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входом за- писи регистра номера процессора,группа информационных входов которого соединена с группой выходов первого элемента ИЛИ, вторая группа входов которого соединена с группой выходов элемента И, группа информационных выходов регистра номера процессора соединена с группой информационных входов дешифратора, К выходов которого соединены с соответствукяцими управляющими входами К ключей приема-передачи информации, при этом (К+1)-й выход дешифратора j-ro блока связи с периферийным устройством соединен с J-M информационным входом регистра состояния, группа информационных выходов которого соединена с группами информационных входов К ключей ввода данных.

/Г.,

J

С8ыу(,19Л.5азла 19г

Ы

CSoix. 2 за. 25 чзна 1Я

/

Ш

Н2г

С8ых -2 9Л. 2fft/3/ia щ .,

JLJL

Hi8,

.

сил

BK

««

ггб

BK

и

dd

двод

В

вк м/

3

в г

47

От1н

/

36f/f

г

От Iffi

Om19fi

| Чу Я | |||

| Организация ЭВМ и микропро- .граммирование | |||

| -М.: Мир, 1975, с | |||

| ИНЕРЦИОННО-АККУМУЛЯТОРНОЕ ПРИСПОСОБЛЕНИЕ ДЛЯ АВТОМАТИЧЕСКОГО ОТКРЫВАНИЯ И ЗАКРЫВАНИЯ ВЕРТИКАЛЬНОГО КЛИНОВОГО ЗАТВОРА ОРУДИЙ | 1912 |

|

SU510A1 |

| Авторское свидетельство СССР № 1153328, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Целью изобретения является повышение производительности и сокращение аппаратурных затрат | |||

| Устройство содержит М | |||

| блоков связи с периферийным устройством, М регистров кода номера процессора, К блоков связи с процессорами, К ключей ввода данных, регистр состояния и блок пересчета | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-20—Подача