одиночного импульса, а второй вход RS-триггера является входом синхронизатора, выходы третьего элемента И, олемента задержки, четвертого элемента И и пятого элемента И являются соответственно первым, вторым, третьим и четвертым выходами синхронизатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор синусоидальных сигналов | 1984 |

|

SU1215162A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU384115A1 |

| Цифровой генератор синусоидальных сигналов | 1987 |

|

SU1450068A1 |

| Устройство для передачи дискретных сигналов | 1984 |

|

SU1277419A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1709355A1 |

| Цифровой генератор синусоидальных сигналов | 1984 |

|

SU1223328A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

1. ЦИФРОВОЙ ГЕНЕРАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ, содержащий последовательно соединенные первый блок элементов И, первый накапливаю щий сумматор, последовательно соединенные первый регистр памяти и второй блок элементов И, синхронизатор, первый, второй и третий выходы которого соответственно соединены с установочным входом первого накапливающего сзгмматора, управляющим вхог: дом первого блока элементов И и с .управляющим входом второго блока элементов Н, и блок умножения кодов, при этом прямой и ия зерсиый выходы первого иакапливаннцего сумматора подключены соответственно к первому и второму входам блока умножения кодов, отличающийся тем, что, с целью обеспечения изменения по частоте выходных сигналов, в него введены последовательно соединенные второй, регистр памяти, третий блок элементов И, блок элементов ИЛИ и второй накапливающий сзт матор, выход которого соединен с информационным входом первого блока элементов И, выход второго блока элементов .И подключен к второму входу блока эле-ментов ИЛИ, управляющий вход третьего блока элементов И соединен с четвертым выходом синхронизатора, управляющий вход и управляющий выход второго накапливающего сумматора соеди,нены соответственно с первым выходом синхронизатора и входом синхронизатора 2. Генератор по п.1,о т л и чающийся тем, что синхронизатор содержит последовательно соединенные генератор тактовых импульсов, первый и второй элементы И, счетчик и дешифратор, последовательно соединенные генератор одиночного импульса и RS-триггер, выход которого подключен к второму входу первого ОЗ элемента И, инвертор, элемент задерж«ч| ки, третий, четвертый и пятый эле менты И, первые входы третьего, чет&9 вертого и пятого элементов И объединены с входом элемента задержки и подключены к выходу первого элемента И, вторые входы третьего, четвертого и пятого элементов И соответственно подключены к первому, второму и третьему выходам дешифратора, |вход и выход инвертора соответственно подключены к выходу пятого эле(Меита И,и к второму входу второго элемента И, установочный вход счет: чика соединен с выходом генератора

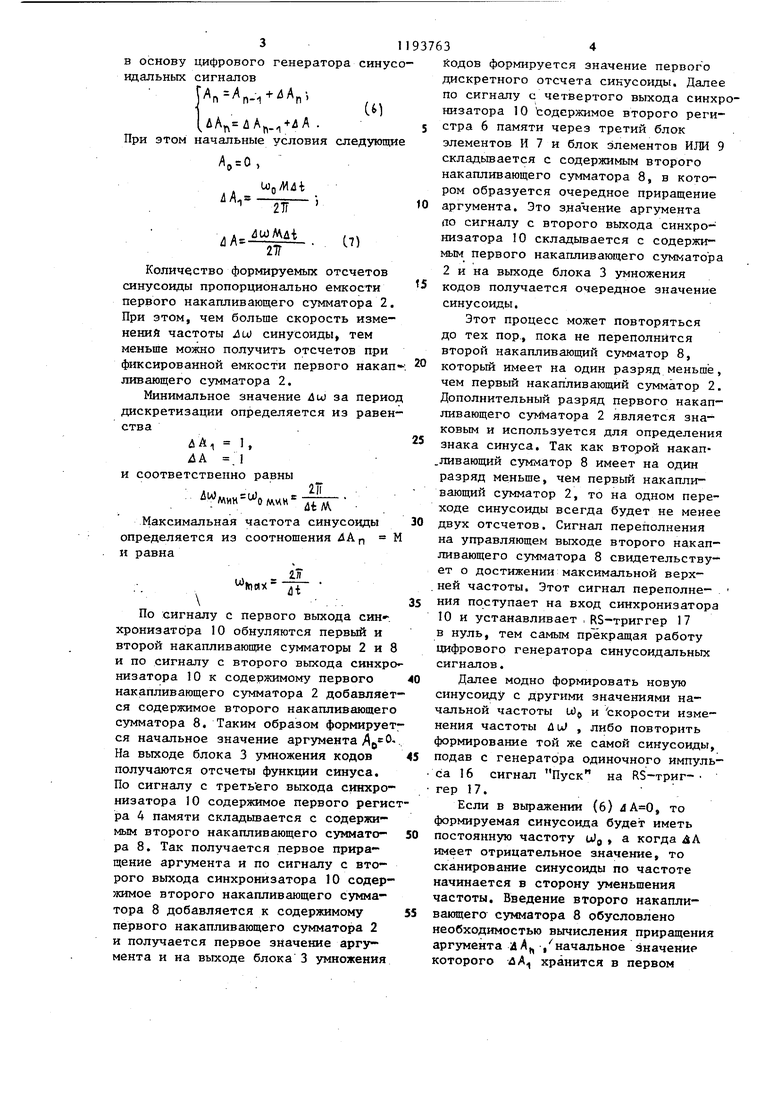

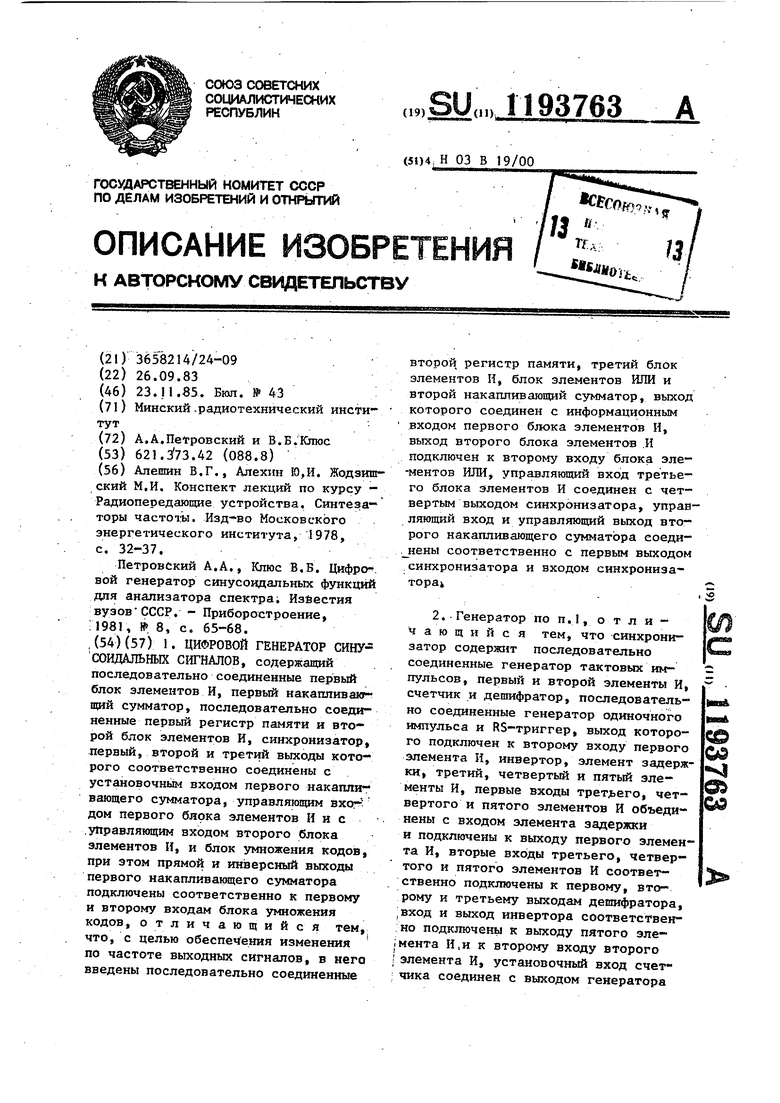

Изобретение относится к радиотехнике и может использоваться в цифровых системах формирования синусоидальных сигналов с изменяющейся во времени частотой. Цель изобретения - обеспечение изменения по частоте выходных сигналов. На фиг.1 представлена структурная электрическая схема цифрового генератора синусоидальных сигналов; на фиг.2 - структурная схема синхронизатора. Цифровой генератор синусоидальных сигналов содержит первый блок элемечтов И 1 , первый накапливающий сумма тор 2, блок 3 умножения кодов, первый регистр 4 памяти, второй блок элементов И 5, второй регистр 6 памяти, третий блок элементов И 7, второй накапливающий сумматор 8, . блок элементов ИЛИ 9, синхронизатор 10. При этом синхронизатор содер жит генератор .. 11 тактовых импульсов первый элемент И 12, второй элемент И 13, счетчик 14, дешифратор I5, генератор 16 одиночного импульса, RS-триггер 17,; элемент 18 задержки инвертор 19, третий элемент И 20, четвертый элемент И 21 и пятый элемент И 22. Цифровой генератор синусоидальных сигналов работает следующим образом В основу работы Цифрового генератора синусоидальных сигналов положен алгоритм, основанный на соотношении хСТГ-х ) S, |- s(n X для О С X I ИЛИ:в дискретном виде (-if (n-KM)M-(vKM)uAsiM)onui . (1) дпя любого п где А § М / п - амплитуда синусоида;dt - период дискретизации;rt 0,1,2 - текущий номер вырабатьшаемой дискреты; М - емкость первого накапливающего сумматора 2 без знакового разряда;К - число переполнений первого накапливающего сумматора 2. Аргумент синусоиды А и его риращение постоянны и пропорциональы частоте ш генерируемой синусоды. Дпя п-го отсчета синусоиды, аргуент А р равен + UJ.4t . Дпя получения синусоиды с изменяюейся частотой во времени вместо остоянной частоты и нужно подавлять значения частоты иУ, , измеяющейся при переходе от одного тсчета к другому А„ Ар.,+4А„ /1„.,4и;„д. (3) Для равномерного изменения частоы формируемой синусоиды значения ш задаются, следующим образом U)f,). ДЦ) , ( где . ДЫ - изменение частоты за время At, т.е. скорость сканирования синусоиды по частоте. На основании (4) приращение аргумента Л А будет определяться следующим образом .+4А , )A-k. () Из соотношений (З) и (5) определяются формулы изменения аргумента формируемой синусоиды, положенные в основу цифрового генератора синус идальных сигналов .,+4A . При этом начальные условия следующи U)gAl4t . л- tOMAi 4А-2|-. Количество формируемых отсчетов синусоиды пропорционально емкости первого накапливающего сумматора 2. При этом, чем больше скорость изменения частоты u) синусоиды, тем меньше можно получить отсчетов при фиксированной емкости первого накап ливающего сумматора 2, Минимальное значение йш за перио дискретизации определяется из равен ства Л А, 1, А .1 и соответственно равны VMviH .f . Максимальная частота синусоиды определяется из соотношения 4А р и равна ( . ;. По сигналу с первого выхода синхронизатора 10 обнуляются первый и второй накапливаюш е сумматоры 2 и и по сигналу с второго выхода синхр низатора 10 к содержимому первого накапливающего сумматора 2 добавляе ся содержимое второго накапливающег сумматора 8. Таким образом формируе ся начальное значение аргумента Др На выходе блока 3 умножения кодов получаются отсчеты функции синуса. По сигналу с третьего выхода синхро низатора 10 содержимое первого реги ра 4 памяти складьшается с содержимым второго накапливающего сумматора 8. Так получается первое приращение аргумента и по сигналу с второго выхода синхронизатора 10 содер жимое второго накапливающего сумматора 8 добавляется к содержимому первого накапливающего сумматора 2 и получается первое значение аргумента и на выходе блока 3 умножения йодов формируется значение первогЪ дискретного отсчета синусоиды. Далее по сигналу с четвертого выхода синхронизатора 10 Ьодсржимое второго регистра 6 памяти через третий блок элементов И 7 и блок элементов ИЛИ 9 складьгоается с содержимым второго накапливающего сумматора 8, в котором образуется очередное приращение аргумента. Это значение аргумента (То сигналу с второго выхода синхронизатора 10 складьшается с содержимым первого накапливающего сумматора 2 и на выходе блока 3 умножения кодов получается очередное значение синусоиды. Этот процесс может повторяться до тех пор., пока не переполнится второй накапливающий сумматор 8, который имеет на один разряд меньше, чем первый накапливающий сумматор 2. Дополнительный разряд первого накапливающего сумматора 2 является знаковым и используется для определения знака синуса. Так как второй накапливающий сумматор 8 имеет на один разряд ме|ньше, чем первый накапливающий сумматор 2, то на одном переходе синусоиды всегда будет не менее двух отсчетов, Сигнал переполнения на управляющем выходе второго накапливающего сумматора 8 свидетельствует о достижении максимальной верх- ней частоты. Этот сигнал переполнения поступает на вход синхронизатора 10 и устанавливает ,RS-триггер 17 в нуль, тем самым прекращая работу цифрового генератора синусоидальных сигналов. Далее модно формировать новую синусоиду с другими значениями начальной частоты tOj и скорости изменения частоты u(jJ , либо повторить формирование той же самой синусоиды, подав с генератора одиночного импульса 16 сигнал Пуск на RS-триг- гер 17. Если в выражении (б) , то формируемая синусоида будет иметь постоянную частоту Ы, а когда 4А имеет отрицательное значение, то сканирование синусоиды по частоте начинается в сторону уменьшения частоты. Введение второго накапливающего сумматора 8 обусловлено необходимостью вычисления приращения аргумента аА /начальное значение которого лА хранится в первом

регистре 4 памяти, а во втором ре гистре 6 памяти хранится значение изменения приращений аргумента Л А. Записьшая в регистры 4 и 6 различные значет1Я аргумента и его приращения; возможно формирование синусоиды с различными законами изменения по частоте. Если в качестве второго региЬтра 6 памяти использовать оперативное запоминающеее устройство, в ячейках которого записаны различные значения приращений аргумента, то в цифровом генераторе синусоидальных функций возможно программное управление скоростью качания синусоиды и частотным диапазоном посредством изменения содержимого запоминающего устройства,

В синхронизаторе 10 осуществляется формирование необходимых последовательностей управляющих сигналов. Управляющие сигналы формируются путем дешифраций соответствующих состояний счетчика 14, на вход которого поступают импульсы с генератора 11 тактовых импульсов. На первомчетвертом выходах синхронизатора при

этом формируются последовательности тактовых импульсов с различной за. держкой по отношению друг друга,

Дешифратор 15, инвертор 19, третий, 5 четвертый, пятый элементы И 20-22 и второй элемент И 13 образуют схему демультиплексора, который коммутирует выход генератора .11 тактовых импульсов на первый, третий и четвертые

0 выходы синхронизатора 10. Сигнал Пуск обнуляет счетчик 14 и после того, как счетчик 14 просчитывает три импульса, сигналы с выхода . инвертора 19/Через второй злемент

5 И 13 запрещают работу счетчика 14.

Таким образом, предлагаемый циф ровой генератор синусоидальных . сигналов позволяет формировать синусоидальные сигналы как фиксированной, так и переменной .частоты, при этом можно программно управлять законом изменения частоты синусоидальных сигналов, скорость качания синусоиды

5 и частотным диапазоном посредством изменения содержимого регистров памяти.

. /

| Алешин В.Г., Алехин Ю,И | |||

| Жодзишский М.И, Конспект лекций по курсу - Радиопередающие устройства | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Петровский А.А., Клюс В.Б | |||

| Цифро | |||

| вой генератор синусоидальных функций для анализатора спектра; Изйестия вузовСССР | |||

| - Приборостроение, ; 1981, № 8, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| , | |||

Авторы

Даты

1985-11-23—Публикация

1983-09-26—Подача