со ел

4 СО 00

Изобретение относится к импульсной технике, в частности к устройствам, в которых непрерывная серия импульсов преобразуется в серию импульсов требуемого вида, и может б1ить использбвано в различных систе мах с цикловой синхронизацией.

Цель изобретения - расширение функциональных возможностей путем получения на выходе преобразователя нескольких последовательностей импульсов и повышение надежности преобразователя путем сокращения числа элементов.

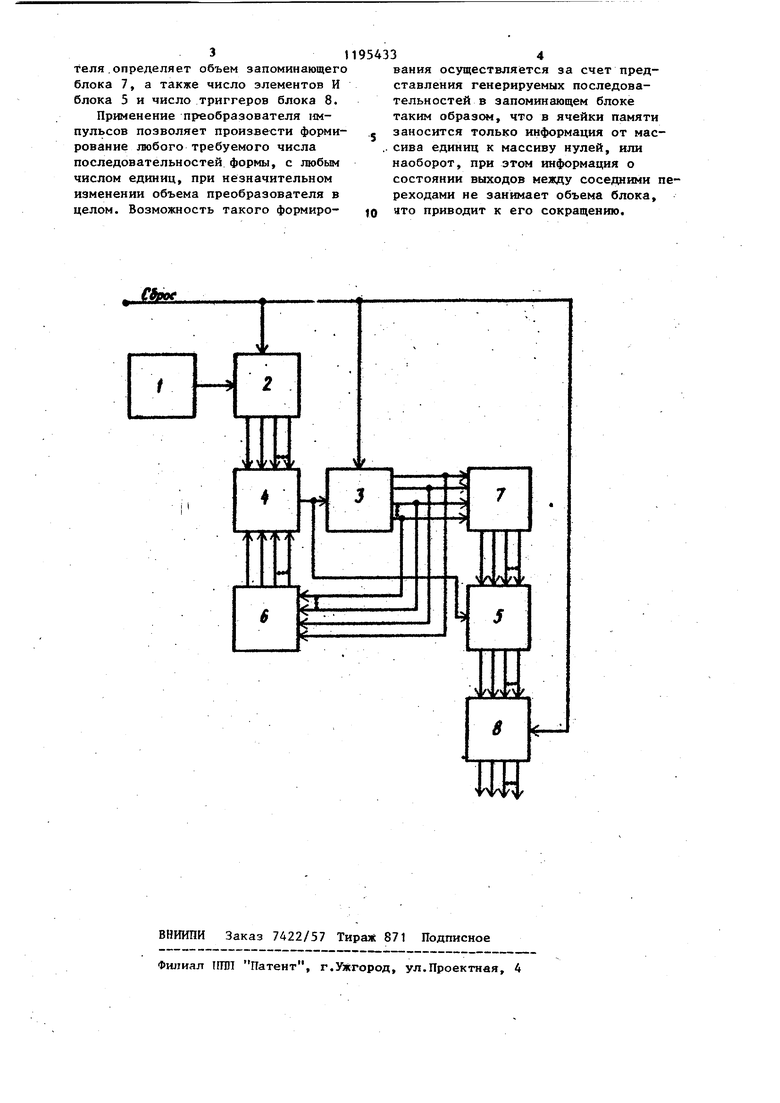

На чертеже представлена функциональная схема предлагаемого преобразователя .

Преобразователь последовательности импульсов содержит генератор 1 импульсов, первый 2 и второй 3 счетчики импульсов, блок 4 сравнения, блок 5 элементов И,первый 6 и второ

7запоминающие блоки, и блок 8 триггеров. Выход генератора 1 импульсов соединен с входом первого счетчика 2, выходы которого подключены к первым входам блока 4 сравнения. Выход блока 4 сравнения соединен с входом второго .счетчика 3 и с управляющим входом блока 5 элементов И. Выхода второго счетчика 3 подсоединены к входам первого 6 и второго 7 запоминающих блоков. Выходы первого запоминающего блока 6 соединены с вторыми входами блока 4 сравнения,

а выходы второго запоминающего блока 7 через блок 5 элементов И - С входом блока 8 триггеров. Выходы блока 8 триггеров являются выходами преобразователя последовательности импульсов. Обнуляющие входы первого 2 и второго 3 счетчиков и блока 8 триггеров подключены к шине сброса.

Преобразователь последовательности импульсов работает следующим образом.

.До начала работы в запоминающий блок 6 записываются коды моментов времени, в которые происходит изменение состояния одного или нескольк выходов преобразователя, причем болшему значению кода момента времени соответствует большее значение кода адреса ячейки запоминающего блока.

8запоминающий блок 7 записываются коды состояний выходов преобразователя в опрашиваемые моменты времени

Первоначально на счетчики 2 и 3, а также на блок 8 триггеров поступает сигнал сброса, устанавливающий на выходах обоих счетчиков 2 и 3 код со значением нуля, а ни выходах блока 8 триггеров - начальный

код вырабатываемых последовательностей. Нулевой код с выхода счетчик 3 подается на адресные входы с запоминающих блоков 6 и 7, на выходах которых присутствует код, записанный в их первые ячейки. Сигнал тактовой частоты с выхода генератора 1 импульсов поступает на вход счетчика 2, код на выходе которого с каждым тактом увеличивает свое значение на единицу. При совпадении кодов на выходе счетчика 2 и на выходе запоминающего блока 6 элемент 4 сравнения вырабатывает импульс, от- . крывающий блок 5 элементов И, при этом код, записанный в первой ячейке запоминающего блока 7, поступает через блок 5 элементов И на входы блока 8 триггеров и производит переключение соответствующих выходов

5 преобразователя последовательности импульсов. Импульс с выхода элемента 4 сравнения также производит переключение счетчика 2, код на выходе кото-рого принимает значение единицы, что соответствует адресу второй ячейки обоих запоминающих блоков 6 и 7. С этого момента времени на выходах обоих запоминающих блоков присутствует код, записанный во вторую ячейку. При последующем увеличении кода на выходе счетчика 2 до значения кода, записанного во второй ячейке запоминающего блока 6, происходит повторное срабатывание элемента 4 сравнения, и цикл переключения сигналов на выходе преобразователя повторяется. В течение интервала времени, в котором коды начала и конца определяются содержимым двух соседних ячеек запоминающего блока 6, сигналы, вырабатываемые на выходе преобразователя, сохраняются без .изменения. Период работы преобразователя в целом определяется числом разрядов счетчика 2, в соответствии с которым устанавливается ,количество разрядов запоминающего блока 6 и элемента 4 сравнения. Количествоизменений выходных сигналов преобразователя на одном периоде определяет число адресов обоих запоминающих блоков 6 и 7, а также соответствующее ему число разрядов счетчика 3. Требуемое число выходных сигналов преобразова3t

теля.определяет объем запоминающего блока 7, а также число элементов И блока 5 и число триггеров блока 8. Применение преобразователя импульсов позволяет произвести формирование любого требуемого числа последовательностей формы, с любым числом единиц, при незначительном изменении объема преобразователя в целом. Возможность такого формиро954334

вания осуществляется за счет представления генерируемых последовательностей в запоминающем блоке таким образом, что в ячейки памяти .J заносится только информация от мас.. сива единиц к массиву нулей, или наоборот, при этом информация о состоянии выходов между соседними переходами не занимает объема блока, 10 НТО приводит к его сокращению.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель коэффициента гармоник | 1986 |

|

SU1366964A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Двухканальное устройство для акустико-эмиссионного контроля | 1988 |

|

SU1508140A1 |

| Формирователь импульсов | 1986 |

|

SU1455385A1 |

| Устройство для измерения среднеквадратического значения напряжения случайного сигнала | 1978 |

|

SU789787A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство измерения частотных характеристик группового времени запаздывания четырехполюсников | 1988 |

|

SU1631511A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| Устройство для обработки изображений | 1986 |

|

SU1316003A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ, содержащий генератор импульсов, первый и второй счетчики импульсов, блок сравнения, блок элементов И, отличающийся тем, что, с целью расширения функциональных возможностей путем получения нескольких .последовательностей импульсов, в него дополнительно введены первый и второй запоминающие блоки и блок tpиггepoв, причем выход генератора импульсов соединен с входом первого счетчика, выхода которого соединены с первыми входами блока сравнения, выход которого соединен с входом второго счетчика, управляющим входом блока элементов И, выходы второго счетчика соединены с входами первого и второго запоминающих блоков, выходы первого запоминающего блока соединены с вторыми входами блока сравнения, а выходы второго запоминающего блока соединены через блок элементов И с входом блока триггеров, выходы которого явi ляются выходами преобразователя последовательности импульсов, обну(Л ляющие входы первого и второго счетчиков и блока триггеров подключены к шине сброса.

ФФГ at

ОЛ ц

i Q i:

Ш4

| ВСЕСОЮЗНАЯ | 0 |

|

SU362447A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь последовательности импульсов | 1974 |

|

SU555539A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-11-30—Публикация

1984-03-07—Подача