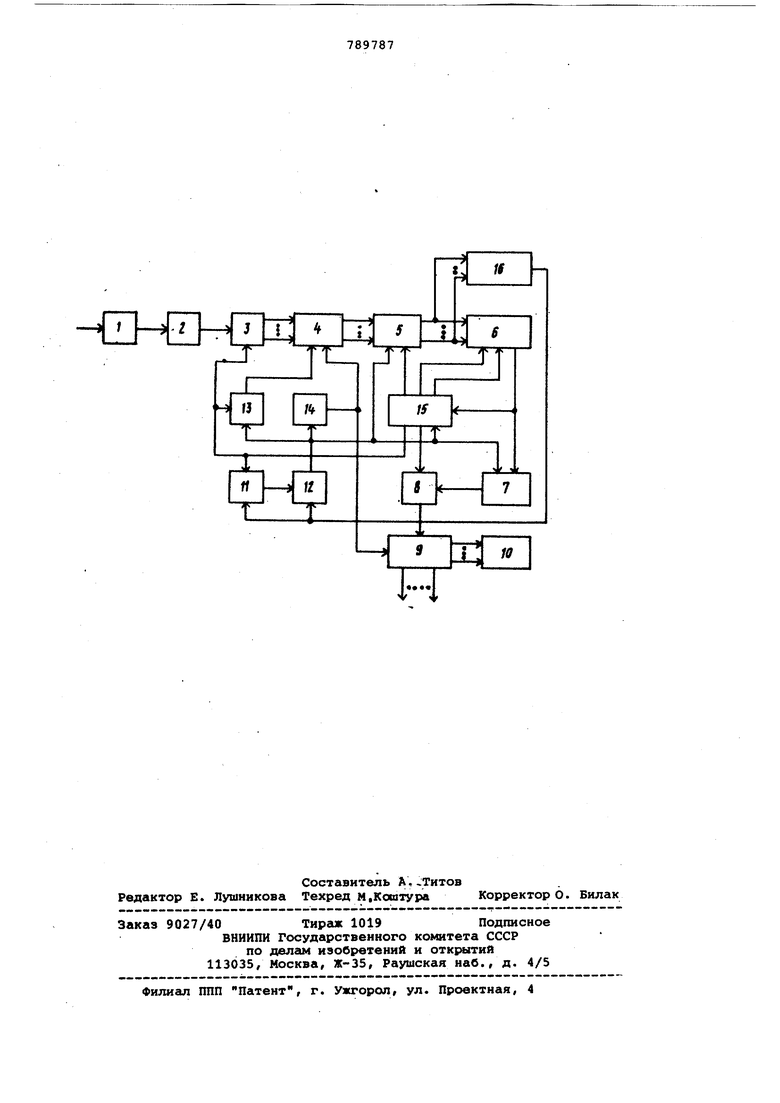

.триггера режима соединен со входами элемента запрета и формирователя, управляющими входами блока управления, триггера записи, вторым входом реверсивного счетчика, управляющий вход которого соединен со вторым выходом блока управления, третий и четвертый выходы которого соединены с входами управления оперативного запоминающего устройства, выход кото рого соединен с входом блока управл ния,, пятый выход которого соедииен со вторым входом элемента И, а выходы элемента запрета и формирователя соединены с входами коммутатора и вторым входом счетчик результата. На чертеже изображена электричес кая схема устройства. Устройство содержит логарифмичес кий усилитель 1, амплитудный детектор 2, аналого-цифровой преобразователь 3, коммутатор 4, реверсивный счетчик 5, оперативное запоминающее устройство б, триггер 7 записи, элемент 8 И, счетчик 9 результата, блок 10 индикации, счетчик 11 числа отсчетов, триггер 12 режима, элемен 13 запрета, формирователь 14, блок 15 управления и дешифратор 16. Устройство работает следующим образом. Измеряемый сигнал поступает на вход логарифмического усилителя 1, сжимающего его динамический диапазон . Сигнал с выхода логарифмического усилителя .через амплитудный детектор 2 поступает на вход аналогоцифрового преобразователя 3, которы вырабатывает двоичный код числа N j пропорционального максимальному значению измеряемого напряжения вхо ного сигнала в i-ой точке отсчета, выраженному в децибелах. Частота дискретизации аналогового сигнала в аналого-цифровом преобразователе определяется частотой импульсов о,пр са, поступающих на его вход из блока 15. В начале цикла измерения счетчик 11, реверсивный счетчик 5, триггер .12 и триггер 7 установлены в нулево состояние., а в ячейках оперативного запоминакмцего устройства б записаны нули. Сигнал с выхода триггера 12 определяет режим записи, при этом первый импульс опроса с выхода блока 15 поступает через элемент 13 на вход перезаписи коммутатора 4 и переписывает код N с выходов ана лого-цифрового преобразователя 3 в реверсивный счетчик 5, состояние которого определяет адрес выбра ной ячейки оперативного запоминающе го устройства 6, на выходе которого появляется записанный в ячейке потенциал нуля, который поступает на управляющий вход блока 15. Блок 15 вырабатывает сигналы записи единицы в ячейку А j , которые поступают, на информацио 1ный и синхронизирующий входы оперативного запог-шнающего устройства 6. Операция суммирования квадратов напряжений реализуется в оперативном запоминающем устройстве б следующим образом: i-ый импульс опроса с выхода блока 15 поступает на вход перезаписи коммутатора 4 через элемент 13 запрета, переписывает код числа N.J с выходов аналого-цифрового преобразователя 3 в реверсивный счетчик 5, при этом, если в ячейке AJJ. был ранее записан нуль, то в нее записывается единица. Если в ячейке оперативного запоминающего устройства б по адресу Afj. была записана единица, то на его выходе появляется потенциал единицы, и блок 15 сначала вырабатывает сигналы записи нуля в эту ячейку, а затем импульс счета адреса, который поступает на счетный выход реверсивного счетчика 5 и устанавливает его в состояние N4+ 1. Анашогично, если в ячейке N.; + 1 был записан нуль, то в нее записывается единица, если же бьига записана единица, в нее записывается нуль, а реверсивный счетчик 5 устанавливается в состояние N-+ 2 (перенос единицы в старший разряд сумглы) и т.д. Таким образом, в оперативном запоминающем устройстве 6 реализуется операция поразрядного сложения двоичных чисел. Счетчик 11 подсчитывает импульсы опроса и по окончании п 2 импульсов вырабатывает сигнал,устанавливающий триггер 12 в единичное состояние, соотв-етствующёе режиму считывания. Сигнал с выхода триггера 12 запрещает прохождение импульсов опроса через элемент 13 на вход коммутатора 4, переключает реверсивный счетчик 5 в режим вычитание, снимает сигнал установки в нулевое состояние со входа триггера 7, Кроме того, по фронту сигнала с выхода триггера 12 формирователь 14 вырабатывает импульс записи, устанавливакядий счетчик 9 в состояние k, а также записывающий в реверсивный счетчик 5 код постоянного числа М , которое вырабатывается коммутатором 4. Число № выбирается большим или равным максимальному адресу ячейки ОЗУ, в которую может быть записана единица при суммировании. При поступлении сигнала с выхода триггера 12 блок 15 начинает вырабатывать импульсы счета адреса и сигналы записи нуля в оперативное запоминакидее устройство б, при этом последовательно опрашиваются и обнуляются ячейки А, А , . . , При установке реверсивного счетчика 5 на адрес Ag единицы старшего

разряда суммы сигнал с выхода оперативного запоминающего устройства б устанавливает триггер 7 в единичное состояние, при этом сигнал с выхода триггера 7 разрешает поступление импульсов счета результата с выхода блока 15 через элемент 8 И на счетный вход счетчика 9.

При достижении реверсивным счетчиком адреса -ApCj ) дешифратор вырабатывает импульс сброса, устанавливающий в нулевое состояние счетчик 11 и триггер 12. Сигнал с выхода триггера 12 переводит устройствО|В режим записи, при этом триггер устанавливается в нулевое состояние и поступление импульсов на счетчик 9 прекргицается. С переходом в режим записи начинается новый цикл измерения, аналогичный описанному вьаие.

Частота импульсов счета результата выбирается в три раза больше частоты импульсов счета адреса.

Код, записанный в счетчике 9, поступает в блок 10, в котором отображается среднеквадратическое значение напряжения измеряемого случайного сигнала.

Таким образом, устройство позволяет повысить точность измерения среднеквадратического значения напржения, при этом точность измерения не зависит от вида распределения уровней случайных сигналов.

Формула изобретения

Устройство для измерения среднеквадратического значения напряжения случайного сигнала, содержащее последовательно соединенные логарифмический усилитель и амплитудный детектор, а также блок индикации, отличающееся тем, что, с целью повышения точности измерения расширения функциональных возможкостей, введены аналого-цифровой преобразователь, коммутатор, реверсивный счетчик, оперативное запоминающее устройство, триггер записи, элемент И, счетчик результата, элемент запрета, формирователь, блок .управления, дешифратор, счетчик числа отсчетов, триггер режима, причем выход амплитудного детектора через последовательно соединенные аналого-цифровой преобразователь, коммутатор, реверсивный счетчик,оперативное запоминающее устройство, триггер записи, элемент И и счетчик результата соединен с входгии1и блока индикации, выход реверсивного счет5чика через дешифратор соединен с первьт-Еи входами счетчика числа отсчетов и триггера режима, второй вход которого соединен с выходом счетчика числа отсчетов, второй вход которого

0 соединен с управляющими входами аналого-цр1фрового преобразователя и элемента запрета и первым выходом блока управления, выход триггера режима соединен со входами элемента запрета и формирователя, управляю5щими входа.ми блока управления, триггера записи, вторым входом реверсивного счетчика, управлякяциа вход которого соединен со вторьм выходом блока управления, третий и четвертый

0 выходы которого соединены с входами улравления оперативного запоминающего устройства, выход которого соединен с входом блока управления,пятый выход которого соединен со вторым

5 входом элемента И, а выходы элемента запрета и формирователя соединены с входами коммутатора и вторым входом счетчика результата.

Источники информации, принятые во внимание при экспертизе

0

1.Патент Великобритании № 1364909, кл. G 01 R 19/00, 1978.

2.Авторское свидетельство СССР № 402813, кл. G 01 R 19/02, 1972 (прототип).

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Реверсивный аналого-цифровой преобразователь | 1988 |

|

SU1612373A1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| Многоканальная система для анализа экстремумов | 1978 |

|

SU750496A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Генератор периодических колебаний инфразвуковых частот с автоматической калибровкой | 1987 |

|

SU1497722A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

Авторы

Даты

1980-12-23—Публикация

1978-07-18—Подача