«

Изобретение относится к вычислительной технике и может быть использовано для быстрого вычисления обратной величины и при реализации операции деления.

Целью изобре.тения, является повышение, быстродействия устройства.

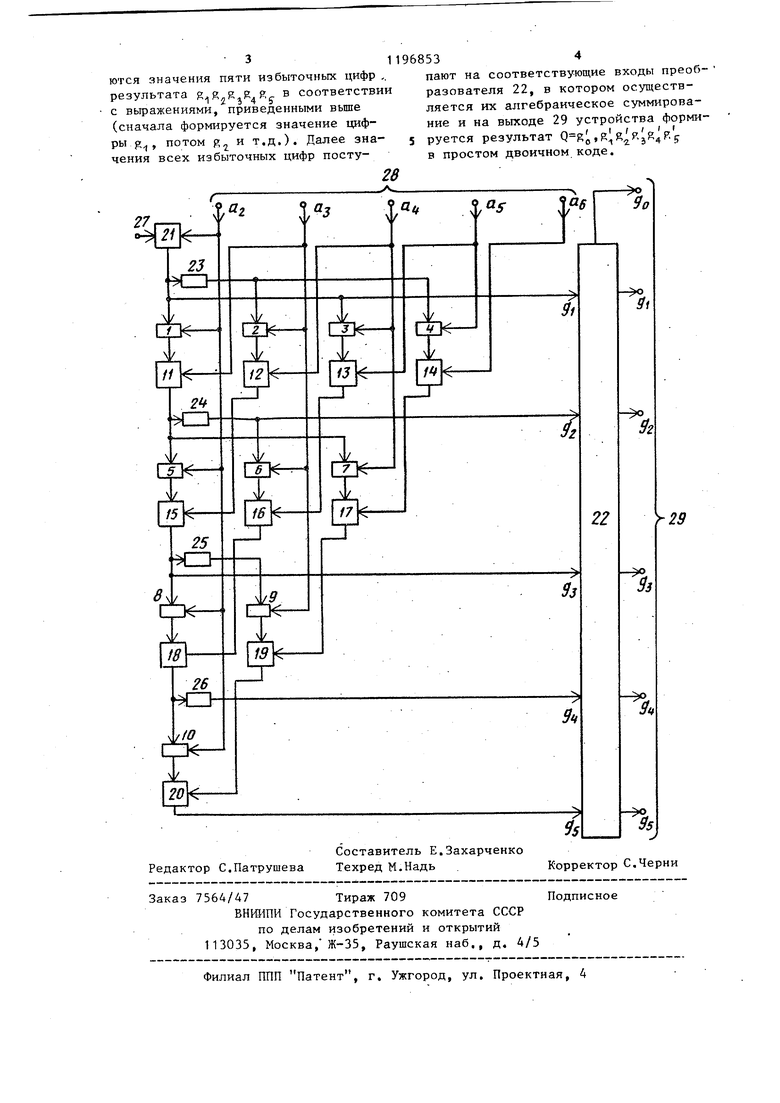

На чертеже представлена структурная .схема устройства для вычисления обратной величины (для случая когда , где п - разрядность операнда, р - число избыточных цифр обратной величины).

Устройство для вычисления обратной величины содержит треугольную матрицу,состоящую из десяти умножителей 1-10 и десяти сумматоров 11-20, вычитатель 21, преобразователь 22 избыточного кода в двоичный, четыре преобразователя 23-26 двоичного кода в обратный, вход 27 кода значения числа 2 устройства, вход 28 операнда устройства, выход 29 результата устройства.

Алгоритм вычисления обратной величины заключается в следующем. Пусть исходный операнд ,а ( - нормализованная двоичная дробь, а значение его обратной величины представляется в виде

Q I go.

где g -i-я избыточная цифра обратной величины QCOiiiS),

Из условия AQ 1 находятся выражения для определения значений избыточных цифр обратной величины. Для этого необходимо приравнять значения сумм соответствующих разрядных произведений произведения A«Q значениям равновесовых разрядов числа 1, представленного в предлагаемом устройстве следующим образом

- ,120000 1-2 +2.2-2

В результате получим следующую систему уравнений. 1; a-rgy:-aa o 2;

a,.,0; а , g( а РЗ К р,з+а g, +а5 р, +а g 0. С учетом того, что SLj- 1, так ка операнд нормализован, выражения для

96853 .

опеределения значений избыточных цифр обратной величины Q принимают вид

8о 1; 5 g 2-а2 ;

(a3+a2g) ; (а +азй/+а2Й2) ; (as+a//g +agg +a g);

(6 +а5 g.+a g +% Rj+a g) .

10 В устройстве избыточные цифры результата формируются в соответствии с приведенными выражениями. Так, цифра gj образуегся на выходе вычитателя 21 ,вход уменьшаемого которого .

15 подключен к входу 27, а вход вычитаемого соединен с входом второго разряда а, операнда А, Цифра g, формируется на выходе преобразователя 24 следующим образом. С помощью умножителя 1 вычисляется значение a2gy, которое далее поступает на первый вход сумматора 11, на второй вход которого подается значение третьего разряда а исходного операнда А.

25 На выходе сумматора 11 образуется результат a,-i- а gy , который отличается только знаком от соответствующего результата в приведенной системе управлений. Преобразователь 24

Зд изменяет знак этого результата на противоположный, в результате чего на его выходе формируется значение второй избыточной цифры результата g2 -(). Подобным образом вычисляются в .устройстве значения и других избыточных цифр резуль.тата Значение цифры g результата всегда равно единице, а поэтому она явно в устройстве не формируется. Но ее значение обязательно учитывается в преобразователе 22 при формировании окончательного значения обратной величины в .простом

двоичном-коде Q go ,1 Р,2.5 «а выходе 29 устройства.

Устройство для вычисления обратной величины работает следующим образом.

На входе 28 устройства одновременно подаются значения .a, . 50- э «t 5 ь

пяти младших разрядов исходного

операнда А ( значение старшего разряда а 1 непосредственно не участвует в формировании избыточных цифр результата и на вход устройства не поступает), Далее последовательно во времени с помощью умножителей , сумматоров 11-20, преобразователей 23-26, вычитателя 21 формируются значения пяти избыточных цифр ,. результата .. в соответствии с вьфажениями, приведенными выше (сначала формируется значение цифры g , потом g и т.д.). Далее значения всех избыточных цифр посту1196853 пают на соответствующие входы преобразователя 22, в котором осуществляется их алгебраическое суммирование и на выходе 29 устройства формируется результат ,R,R{p.jS4F.f в простом двоичном коде.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1984 |

|

SU1231498A1 |

| Устройство для деления | 1985 |

|

SU1332312A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для деления | 1978 |

|

SU802962A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОБРАТНОЙ., содержащее вычитатель, треугольную матрицу из (п-2)(п-1)/2 сумматоров и (п-2)(п-1)/2 умножителей (п-разрядность операнда) и преобразователь избыточного кода в д оичньш, причем i-ая строка матрицы (,...,п-2) содержит (n-i-1) сумматоров и (n-i-1) умножителей, первый вход (i, j)-ro умножителя (,...n-2) соединен с входом Ic-ro разряда операнда устройства (... -1), разрядные выходы результата которого соединены с выходами преобразователя избыточного кода в двоичный, вход второго разряда операнда устройства соединен с первым входом вычитателя, выход (i, j)-ro умножителя - с входом первого слагаемого соответствующего (i, j)-ro сумматора, отличающееся, тем, что, с целью повыЛения быстродействия, в него введены (h-2) преобразователей двоичного кода в обратный, причем вход кода значения числа 2 устройства соединен с вторьм входом вычитателя, выход которого соединен с вторыми входами

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М | |||

| Приспособление к индикатору для определения момента вспышки в двигателях | 1925 |

|

SU1969A1 |

| с.532-536 | |||

| Stefanelly Renato | |||

| А suggestion for а high-speed parallel benary divider | |||

| IEEE Tranf Comput, 1972, V 21, № 1, pp 42-55, fig.1,2,11 | |||

Авторы

Даты

1985-12-07—Публикация

1984-06-14—Подача