Изобретение относится к вычислительной технике и может быть использовано для быстрого выполнения операции деления.

Цель изобретения - повышение бы- стродействия устройства.

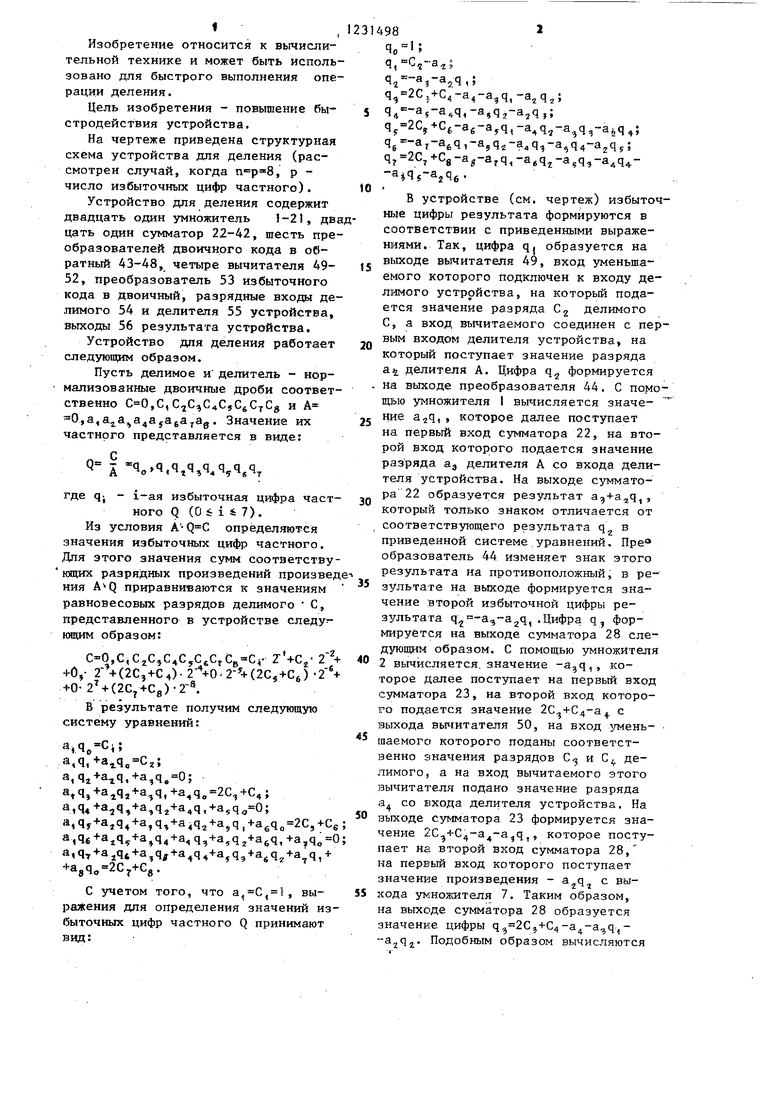

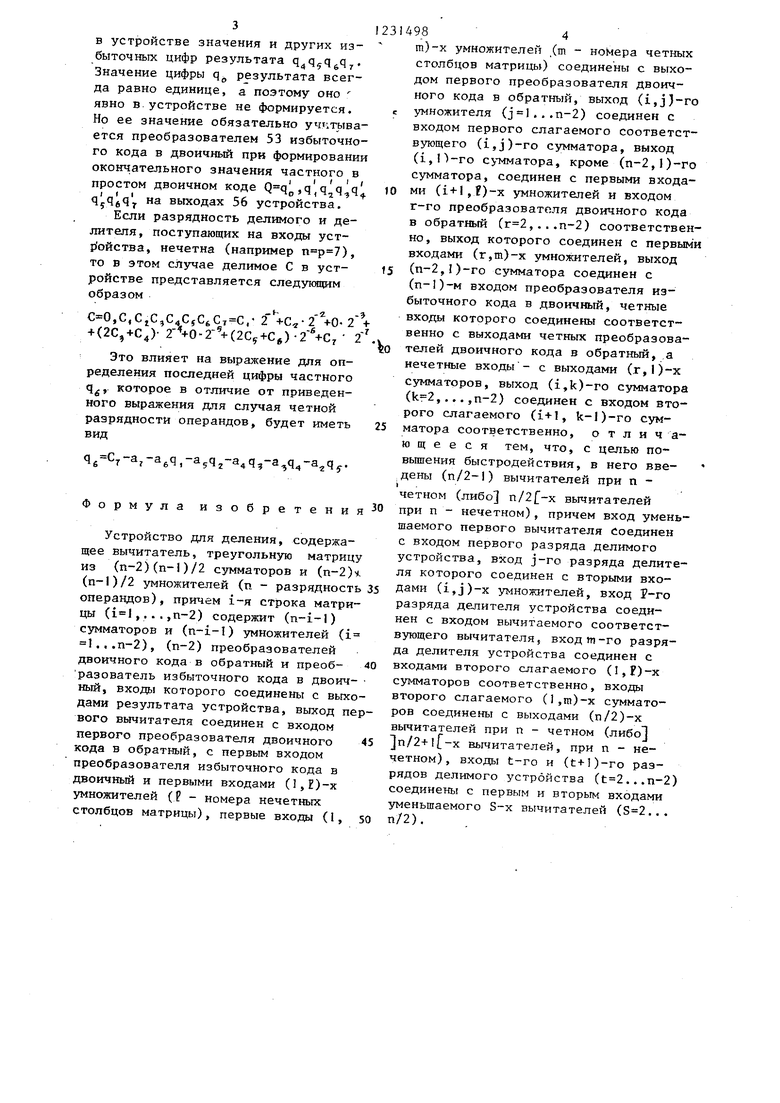

На чертеже приведена структурная схема устройства для деления (рассмотрен случай, когда , р - число избыточньпс цифр частного).

Устройство для деления содержит двадцать один умножитель -2, двацать одии сумматор 22-42, шесть преобразователей двоичного кода в обратный 43-48, четыре вычитателя 49- 52, преобразователь 53 избыточного кода в двоичный, разрядные входы де- лшмого 54 и делителя 55 устройства, выходы 56 результата устройства.

Устройство дпя деления работает следующим образом.

Пусть делимое и делитель - нормализованные двоичные дроби соответственно ,,,(С и А 0,а,. Значение их частного представляется в виде: р

0 tflQQqqqq А о ч

где q-, - i-ая избыточная цифра част-

ного Q (О i 4 7). Из условия А - определяются значения избыточных цифр частного. Для этого значения сумм соответству- кщих разрядных произведений произвед ния приравниваются к значениям равновесовых разрядов делимого С, представленного в устройстве следующим образом:

,С,СгС,С4С, +0,- 2 %(2Cj+C4)- 2 -Ю 2- ь(2С5+Сб) 0 24()-2

В результате получим следующую систему уравнений:

ЧЧо° 5

a,q,-t-aiq C ;

aiqi a q,+a,q.0;

®t4,,+a,q,+a,q,2C,+C,;

.jq,+a,qj+a,q,+a,

iqr+ajq4+a,q,,j+a,q,+agqo 2C,

iiq6+ajq,..+a,,+a,q2+ajq,

«iiq7 aiq4+a,,q,,,,-f agq 2C7+ee.

С учетом того, что а,, вы- 55 дпя определения значений избыточных цифр частного Q принимают вид:

5

0

s

0

5

о

5

0

5

5

q,i;

q,C,

,-a,,q,;

q 2Cj+C4-a,-a,q,

q « -a5-a,q,-a,qj-ajq5;

qy 2Cy+C6-a6-a q,,,-aj,q,;

qg -aj-agq,-a5q2-a q,-a,q4-a2q5;

q,2C +Cg-a -ajq,-aeq,j-a,.q,.

В устройстве (см. чертеж) избыточные цифры результата формируются в соответствии с приведенными выражениями. Так, цифра q образуется на выходе вычитателя 49, вход уменьшаемого которого подключен к входу делимого устройства, на который подается значение разряда С делимого С, а вход вьиитаемого соединен с первым входом делителя устройства, на который поступает значение разряда а делителя А. Цифра q формируется на выходе преобразователя 44, С помощью умножителя I вычисляется значение ,, которое далее поступает на первый вход сумматора 22, на второй вход которого подается значение разряда ад делителя А со входа делителя устройства. На выходе сумматора 22 образуется результат , , который только знаком отличается от соответствующего результата q в приведенной системе.уравнений. Пре образователь 44 изменяет знак этого результата на противоположный, в ре- зультате на выходе формируется значение второй избыточной цифры результата ,.Цифра q, формируется на выходе сумматора 28 следующим образом. С помощью умножителя 2 вычисляется, значение ,, которое далее поступает на первый вход сумматора 23, на второй вход которого подается значение 2С +С4-а с выхода вычитателя 50, на вход уменьшаемого которого поданы соответственно значения разрядов С и С делимого, а на вход вычитаемого этого вычитателя подано значение разряда а со входа делителя устройства. На выходе сумматора 23 формируется значение ,q,, которое поступает на второй вход сумматора 28, на первый вход которого поступает значение произведения - с выхода у нолсителя 7. Таким образом, на выходе сумматора 28 образуется значение цифры q 2Cj+C4-a -a q ,- . Подобным образом вычисляются

3

в устройстве значения и других из- быточных цифр результата . Значение цифры q результата всегда равно единице, а поэтому оно явно в устройстве не формируется. Но ее значение обязательно учитывается преобразователем 53 избыточного кода в двоичный при формировании окончательного значения частного в простом двоичном коде ЧсЧбЧ т выходах 56 устройства.

Если разрядность делимого и делителя, поступающих на входы уст- р ойства, нечетна (например ), то в этом случае делимое С в уст- ройстве представляется следукшщм образом

--г ,-э

,C,CjC,C4C5CtCT C, 2 +0-2 + ( (,) 2

Это влияет на выражение для определения последней цифры частного q, которое в отличие от приведенного выражения для случая четной разрядности операндов, будет иметь вид

,-a,-a,q,-a5q,,-a,.

Формула изобретения

Устройство для деления, содержащее вычитатель, треугольную матрицу из (п-2)(п-1)/2 сумматоров и (п-2)у. (п-1)/2 умножителей (п - разрядность 35 операндов), причем -я строка матрицы (,...,п-2) содержит (n-i-1) сумматоров и (n-i-1) з ножителей (i 1.,.п-2), (п-2) преобразователей двоичного кода в обратный и преоб- 40 разователь избыточного кода в двоич- ный, входы которого соединены с выходами результата устройства, выход первого вычитателя соединен с входом первого преобразователя двоичного 45 кода в обратный, с первым входом преобразователя избыточного кода в двоичный и первыми входами (1,Е)-х умножителей (Р - номера нечетных столбцов матрицы), первые входы (I, 50

с О

15

5

0

5 0 5

4984

т)-х умножителей (т - номера четных столбцов матрицьО соединены с выходом первого преобразователя двоичного кода в обратный, выход (i,j)-ro умножителя (...n-2) соединен с входом первого слагаемого соответствующего (i,j)-ro сумматора, выход (i,l)-ro с -мматора, кроме (п-2, 1)-го сумматора, соединен с первыми входами (i+f,f)-x умножителей и входом г-го преобразователя двоичного кода в обратный ,...п-2) соответственно, выход которого соединен с первыми входами (r,m)-x умножителей, выход (п-2,I)-го сумматора соединен с (n-l)-M входом преобразователя избыточного кода в двоичный, четные входы которого соединены соответственно с выходами четных преобразователей двоичного кода в обратный, а нечетные входы - с выходами (.г,1)-х сумматоров, выход (i,k)-ro сумматора (kr2,...,п-2) соединен с входом второго слагаемого (i+1, k-l)-ro сумматора соответственно, о т л и ч а- ю щ е е с я тем, что, с целью по- вьшения быстродействия, в него введены (n/2-l) вычитателей при п четном (либо n/2f-x вычитателей при п - нечетном), причем вход уменьшаемого первого вычитателя соединен с входом первого разряда делимого устройства, вход j-ro разряда делителя которого соединен с вторыми входами (i,j)-x умножителей, вход Р-го разряда делителя устройства соединен с входом вычитаемого соответствующего вычитателя, вход ш-го разряда делителя устройства соединен с входами второго слагаемого (I,F)-x сумматоров соответственно, входы второго слагаемого (1,т)-х сумматоров соединены с выходами (п/2)-х вычитателей при п - четном (либо n/2+l -x вычитателей, при п - нечетном), входы t-ro и (t+l)-ro разрядов делимого устройства (...n-2) соединены с первым и вторым входами уменьшаемого S-x вычитателей (... п/2).

Я 55 Я 55Я 5В 55 54- 54 55 S5 Я 54 5S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1332312A1 |

| Устройство для деления | 1978 |

|

SU802962A1 |

| Устройство для вычисления обратной величины | 1984 |

|

SU1196853A1 |

| Устройство для деления | 1984 |

|

SU1242935A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления | 1982 |

|

SU1086427A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

Изобретение относится к вычислительной технике и может быть использовано для быстрого вычисления частного двух чисел. Целью изобретения является цовышение быстродействия устройства. Устройство содержит умножители и-сумматоры, образующие треугольную матрицу, преобразователи двоичного кода в обратный, вычи- татели и преобразователь избыточного кода в двоичный с соответствующими связями. 1 ил.

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М.: Наука, 1969, с | |||

| 532-536 | |||

| IEEE | |||

| Trans.Comput | |||

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Stefa- nelly Renato | |||

| A suggestion for a high-speed parallel benary divider | |||

| Устройство для вычисления обратной величины | 1984 |

|

SU1196853A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1984-10-22—Подача