тая группа информационных входов сумматора j-ro узла вычисления, итерационной переменной соединена с выходами элементов И третьей группы этого узла, первые входы которых соединены с выходами разрядов регистра константы,вторые входы элементов И третьей группы j-ro узла вьIчиc.J7eнця ит;ерационной переменной соединены с выходом старшего разряда регистра коэффициентов числителя этого узла, авЬгкоды разрядов регистров коэффициентов знаменателя n-jrb узла вычис;пения итерационной пёремённоЙГ - с первыми входами элементов И первой группы этого узла, вторые входы которых соединены с выходом старшего разряда регистра коэффициентов числителя нулевого узла, выходы элементов И первой группы п-го узла вычисления итерационной переменной с второй группой информационных входов сумматора этого узла, третья группа информационных входов сумматора соединена с выходами элементов И второй группы п-го узла вычисления итерационной переменной, первые входы которых соединены с выходами разрядов регистра констант вторые входы элементов И второй группы п-го узла вычисления итерационной переменной соединены с выходом старшего разряда регистра коэффициентов числителя этого узла, а выходы разрядов регистров коэффициентов знаменателя нулевого узла вычисления итерационной переменной - с первыми входами элементов И

6856

второй группы этого узла, вторые входы которых соединены с выходом старшего разряда коэффициентов числителя нулевого узла вычисления итерационной переменной, выходы элементов И второй группы этого узла соединены с третьей группой информационных входов сумматора нулевого узла, выход старшего разряда регистра коэффициентов числителя k-ro узла вычисления итерационной переменной (К 1,п) соединен с вторыми входами элементов И первой группы (К-1) узла вычисления итерационной переменной, а прямой выход генератора тактовых импульсов соединен с третьими входами элементов И первой, второй, третьей групп j-ro узла вычисления итерационной переменной, с третьими входами элементов И первой и второй групп нулевого и п-го узлов, инверсный, выход генератора тактовых импульсов соединен с синхронизирующими входами регистров коэффициентов числителя всех узлов вычисления итерационной переменной и входом синхронизации регистра результата, информационный вход которого соединен с выходом старшего .разряда регистра коэффициента -числителя нулевого узла, синхронизирующий вход которого соединен со счетным входом счетчика, выход переполнения которого соединен с входом разрешения- генератора тактовых импульсов, а установочный вход счетчика соединен с входом запуска устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1324035A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1254477A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

| Устройство для извлечения корня третьей степени | 1983 |

|

SU1129609A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО содержащее (п+1) узлов вычисления итерационной переменной (п- степень полинома), регистр результата и регистр аргументов, причем i-и узел вычисления итерационной переменной (, п-1) содержит Сумматор, регистр коэффициентов числителя и первую группу элементов И, выходы сумматора i-го узла вычисления итерационной переменной соединены с информационными входами регистра коэффициентов числителя этого узла, выходы регистра коэффициентов числителя i-го узла вычисления итерационной переменной - с первой группой информационных входов сумматора этого узла, вторая группа информационных входов сумматора - с выходами элементов И первой группы i-ro узла вычисления итерационной переменной, первые входы элементов И -первой группы -го узла вычисления итерационной переменной соединены с выходами разрядов регистра аргументов, а .п-й узел вычисления итерационной переменной содержит сумматор-и регистр коэффициентов, причем выходы сумматора п-го узла вычисления итерационной- переменной соединены с информационными входами регистра коэффициентов вычислителя этогоузла, выходы регистра коэффициентов-числителя п-го узла вычисления итерационной переменной соединены с первой группой информационных входов сумматора этого узла, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности вычисления дробно-рациональной функции, в него дополнительно введены генератор тактовых импульсов, счетчик и регистр константы, а j-й узел (, п-1) вычисления итерацион-. ной переменной дополнительно со(Л держит регистр коэффициентов знаменателя, вторую и третью группы элементов И, п-й узел вычисления итерационной переменной дополнительно содержит первую и вторую группы элементов И и регистр косо :эффициентов знаменателя, а нулевой узел дополнительно содержит Од вторую группу элементов И и регистр 00 СП коэффициентов знаменателя, выходы разрядов регистра коэффициентов Од знаменателя -го узла вычисления итерационной переменной соединены с первыми входами элементов И второй группы этого узла, вторые входы элементов И втррой группы соединены с выходом старщего разряда регистра коэффициента числителя нулевого узла, выходы элементов И второй группы j-ro узла вычисления итерационной переменной соединены с третьей группой информационных входов сукматора этого узла, четвер

Изобретение относится к вычислительной технике и может быть применено в специализированных вычислителях.

Цель изобретения - расширение функциональных возможностей за счет возможности вычисления дробно-ра-. циональной функции и повьшение быстродействия за счет организации вычисления по методу цифра за цифрой.

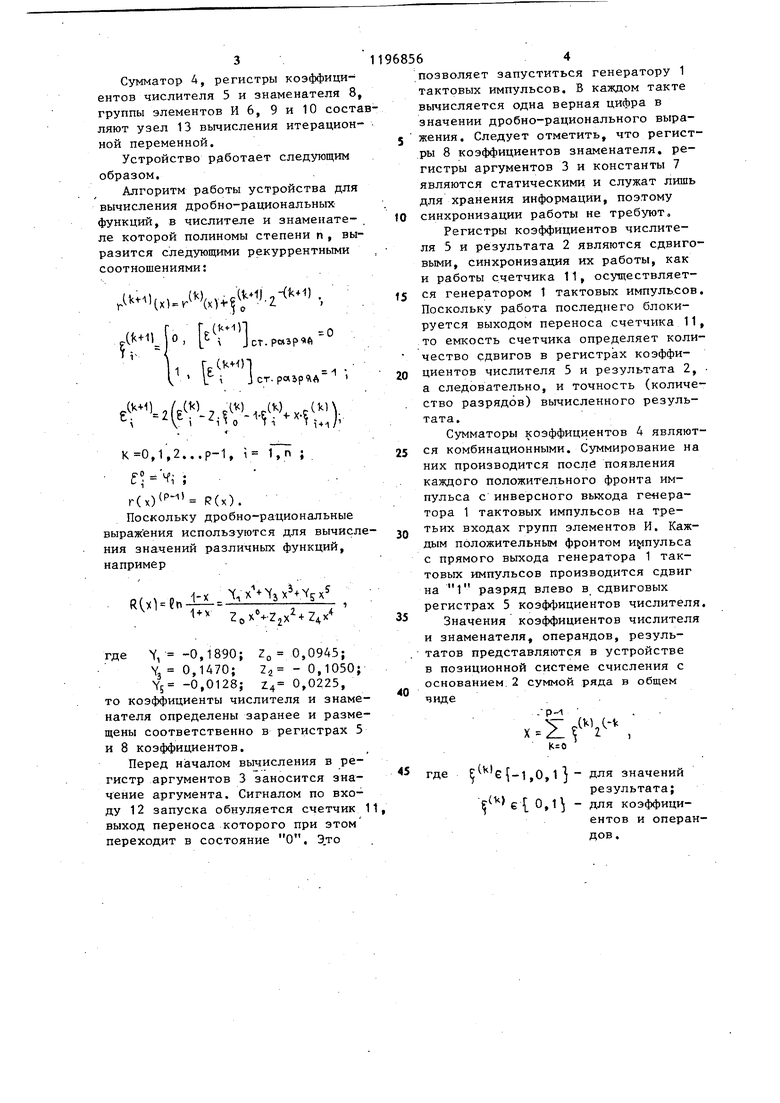

На чертеже представлена структурная схема устройства.

Устройство содержит генератор 1 тактовых импульсов, регистры результата 2 и аргументов 3, сумматоры 4,-регистры 5 коэффициентов числителя, первые группы элементов И 6, регистр 7 константы, регистры 8 коэффициентов знаменателя, вторые 9 и третьи 10 группы элементов И, счетчик 11, вход 12 запуска. 3 Сумматор 4, регистры коэффициентов числителя 5 и знаменателя группы элементов И 6, 9 и 10 сост ляют узел 13 вычисления итерацион ной переменной. Устройство работает следующим образом. Алгоритм работы устройства дл вычисления дробно-рациональных функций, в числителе и знаменателе которой полиномы степени п, вы разится следующими рекуррентными соотношениями: ,ии1,„.,(М(,„5(1ч|.), .№-а,. pw3p«A I V ff Ски) 1 -1 l J ст. pcnipi A Г-(Г- л -пг-1 ;); к 0,1,2...р-1, i ГТп ; С-О ц). . C-, г(х) R(x). Поскольку дробно-рациональные выражения используются для вычисл ния значений различных функций, например х . R()(l en Z..x где Ч, -0,1890; ,0945; Yj 0,1470; 22 - 0,1050 5 -0,0128; Z4 0,0225, то коэффициенты числителя и знаме нателя определены заранее и разме щены соответственно в регистрах 5 и 8 коэффициентов. Перед н;ачалом вычисления в регистр аргументов 3 заносится значение аргумента. Сигналом по входу 12 запуска обнуляется счетчик выход переноса которого при этом переходит в состояние О, Это 64 позволяет запуститься генератору 1 тактовых импульсов. В каждом такте вычисляется одна верная цифра в значении дробно-рационального выраженин. Следует отметить, что регистры 8 коэффициентов знаменателя, регистры аргументов 3 и константы 7 являются статическими и служат лишь для хранения информации, поэтому синхронизации работы не требуют. Регистры коэффициентов числителя 5 и результата 2 являются сдвиговыми, синхронизация их работы, как и работы счетчика 11, осутдествляется генератором 1 тактовых импульсов, Поскольку работа последнего блокируется выходом переноса счетчика 11, то емкость счетчика определяет количество сдвигов в регистрах коэффициентов числителя 5 и результата 2, а следовательно, и точность (количество разрядов) вычисленного результата. Сумматоры коэффициентов 4 являются комбинационными. Суммирование на них производится после появления каждого положительного фронта импульса с инверсного вмхода генератора 1 тактовых импульсов на третьих входах групп элементов И. Каждым положительным фронтом и 1пульса с прямого выхода генератора 1 тактовых импульсов производится сдвиг на 1 разряд влево в сдвиговых регистрах 5 коэффициентов числителя, Значения коэффициентов числителя и знаменателя, операндов, результатов представляются в устройстве в позиционной системе счисления с основанием.2 суммой ряда в общем - P-i x.ZfV- где ,0,1 - для значений результата; g 0,1 - для коэффициентов и операндов.

| Устройство для вычисления дробно-рациональных функций | 1980 |

|

SU934482A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-07-05—Подача