4

со

N9

сд

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ различного класса для Аппаратной реализации функциональных Зависимостей,

Цель изобретения - повьшение точности вычисления.

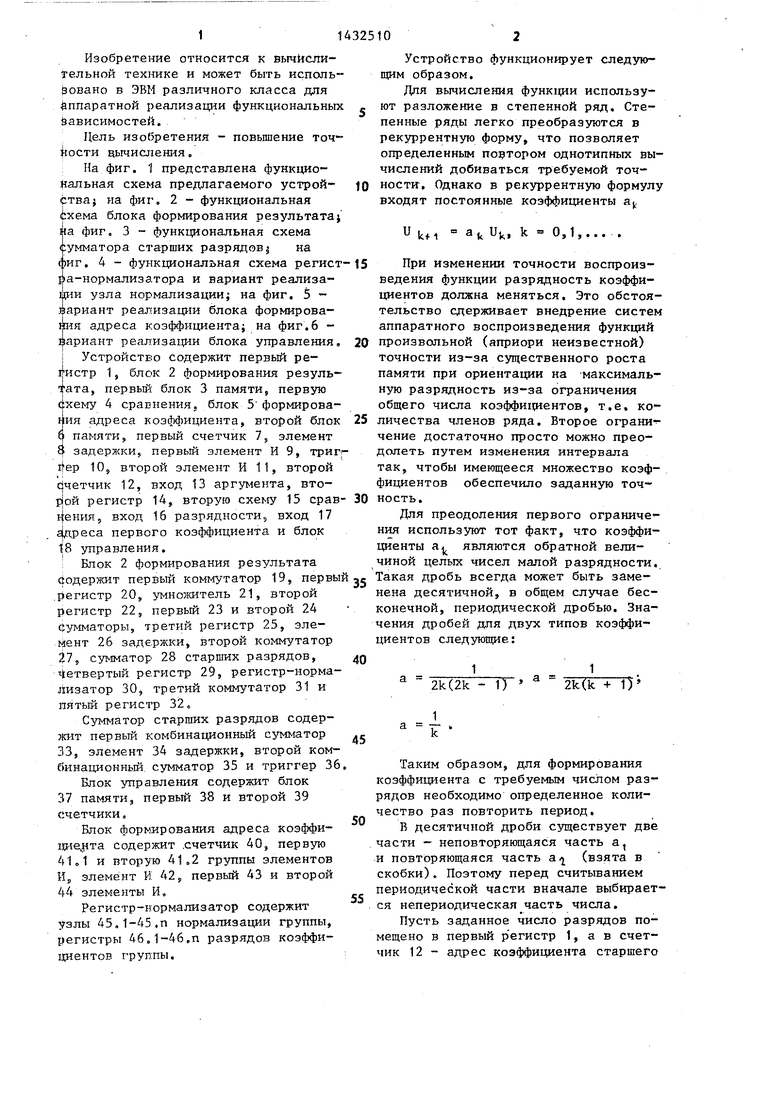

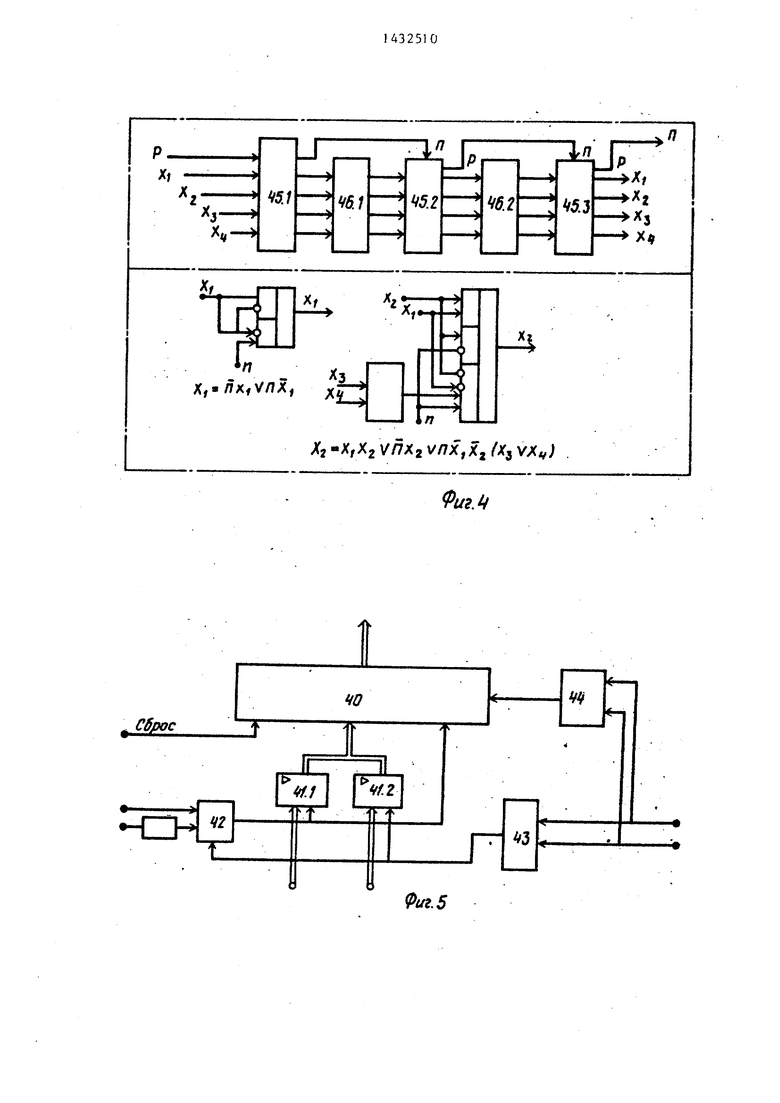

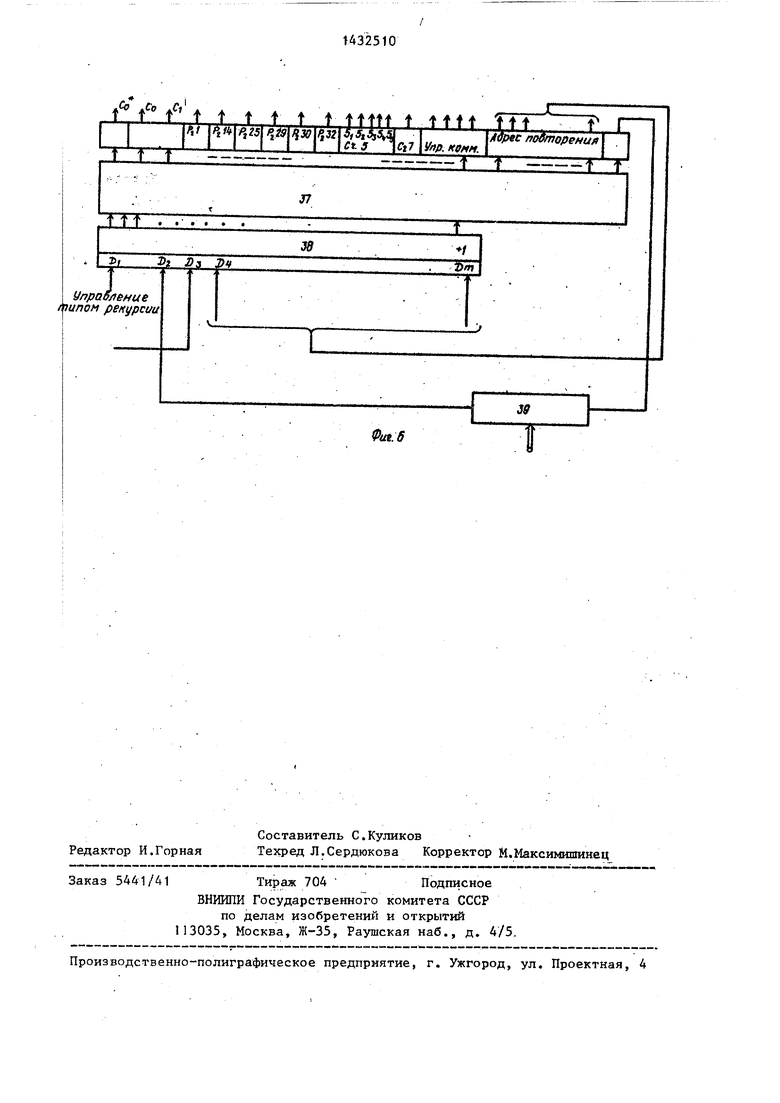

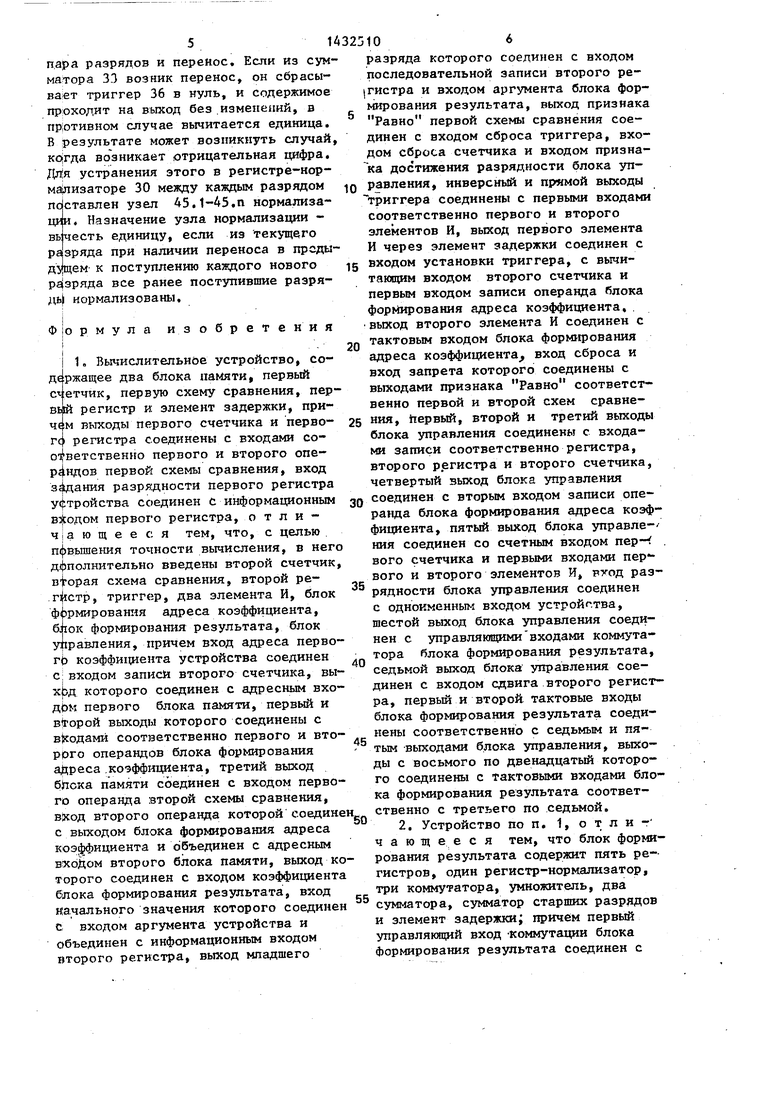

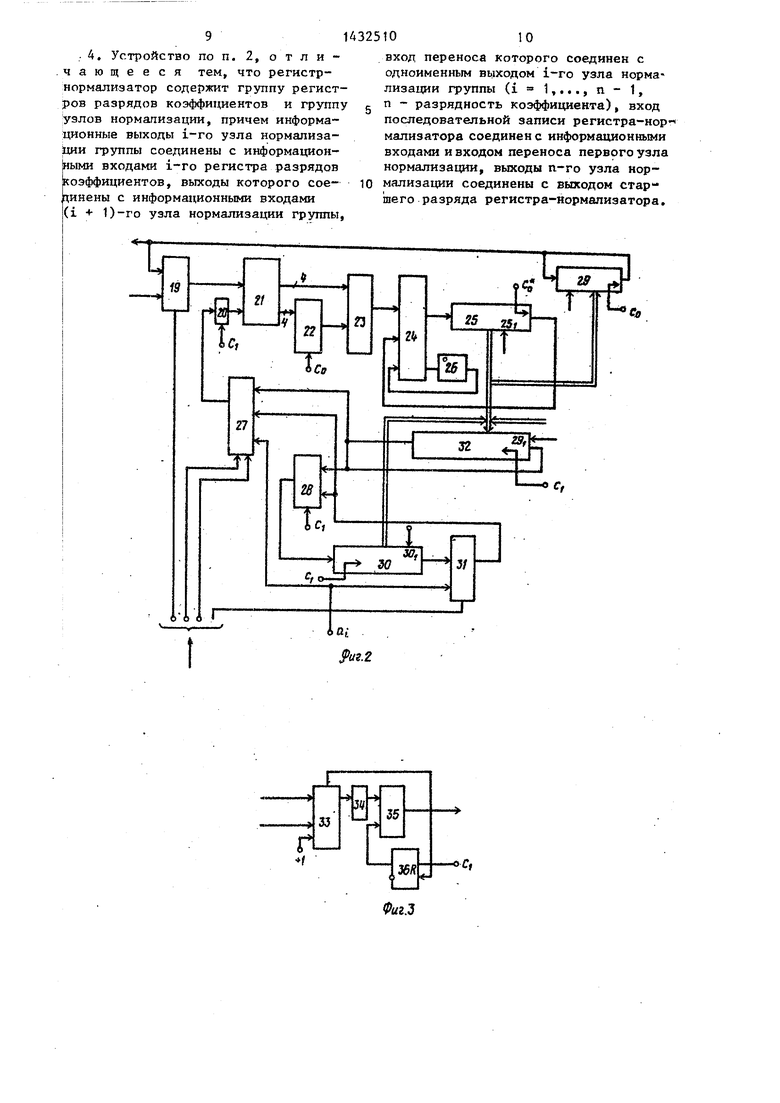

; На фиг. 1 представлена функциональная схема предлагаемого устрой- ства) на фиг. 2 - функциональная (|:хема блока формирования результатаj на фиг. 3 - функциональная схема (сумматора старших разрядов на оиг. 4 - функциональная схема регист ра-нормализатора и вариант реализа- ijpiH узла нормализации; на фиг. 5 .фариант реал:изации блока формирова- 1ШЯ адреса коэффициента; на фиг.6 - щарнант реализации блока управления. i Устройство содержит первый ре- ij HCTp 1J блок 2 формирования результата, первый: блок 3 памяти j первую 4хему 4 сравнения, блок 5 формирова- цтля адреса козф4)ициента, второй блок

памяти, первый счетчик 7, элемент задержки, первый элемент И 9, триге 6

riep 10, второй элемент И 11, второй Ьчетчик 12, вход 13 аргумента, вто- фй регистр 14, вторую схему 15 срав фнияр вход 16 разрядности, вход 17 4п,реса первого коэффициента и блок 18 управления.

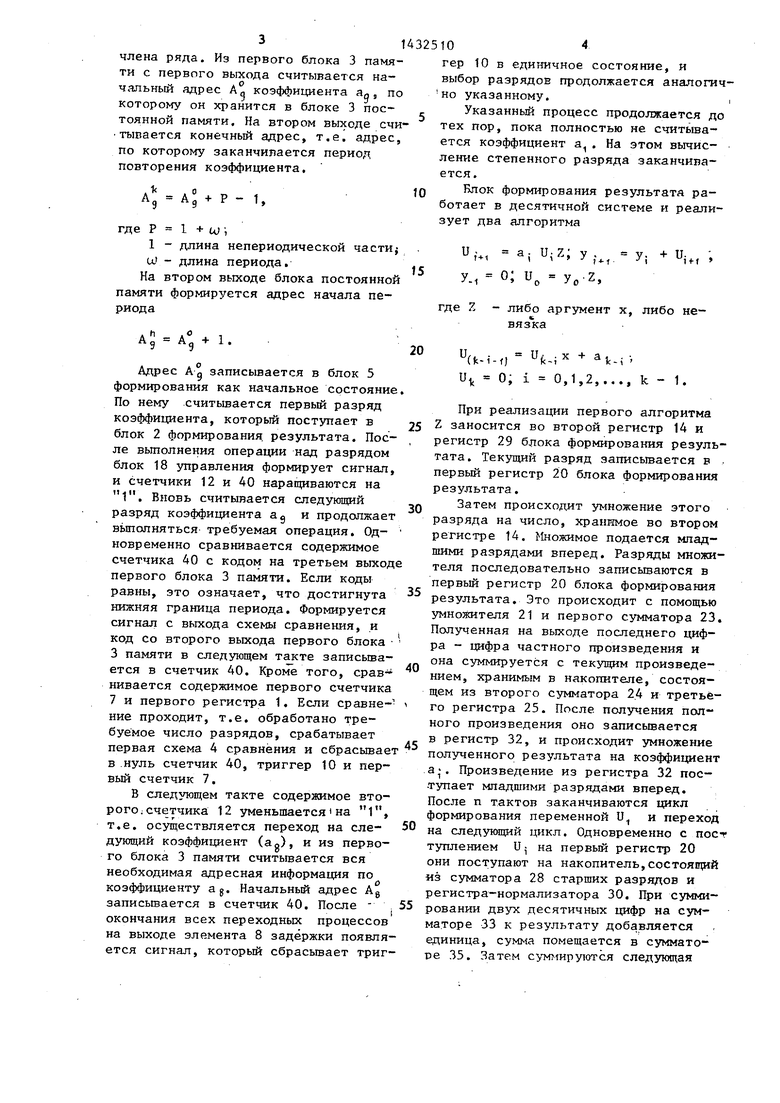

I Блок 2 формирования результата Содержит первый коммутатор 19, первы .регистр 20, умнолдатель 21, второй регистр 22, первый 23 и второй 24 с умматоры, третий регистр 25, эле- мент 26 задержки, второй коммутатор 27 сумматор 28 старших разрядов,

сЬтвертый регистр 29, регистр-нормализатор 30, третий коммутатор 31 и пятый регистр 32s

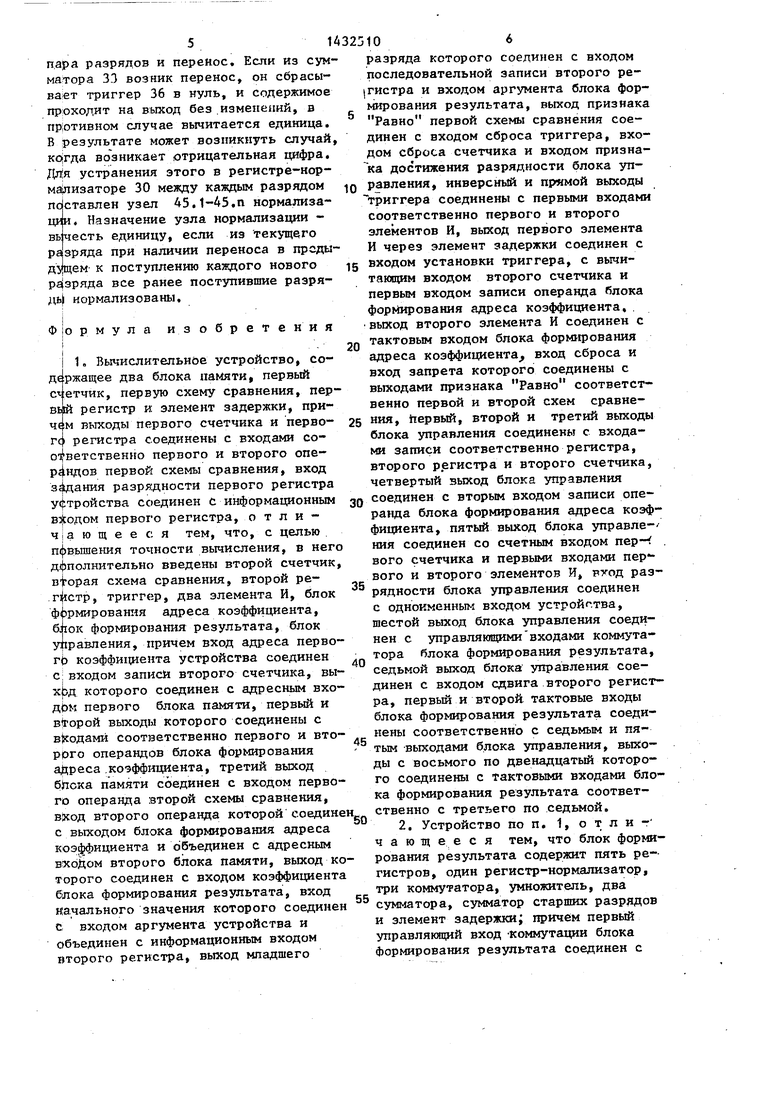

Сумматор старших разрядов содер- jjruT первый комбинационный сумматор 33j элемент 34 задержки, второй комбинационный, cjnsmaTop 35 и триггер 36

Блок управления содержит блок 37 памяти, первый 38 и второй 39 счетчики.

Блок формирования адреса коэффи- 1Ше.нта содержит .счетчик 40, первую 41.1 и вторую 41.2 группы элементов И, элемент И 42, первый 43 и второй 44 элементы И,

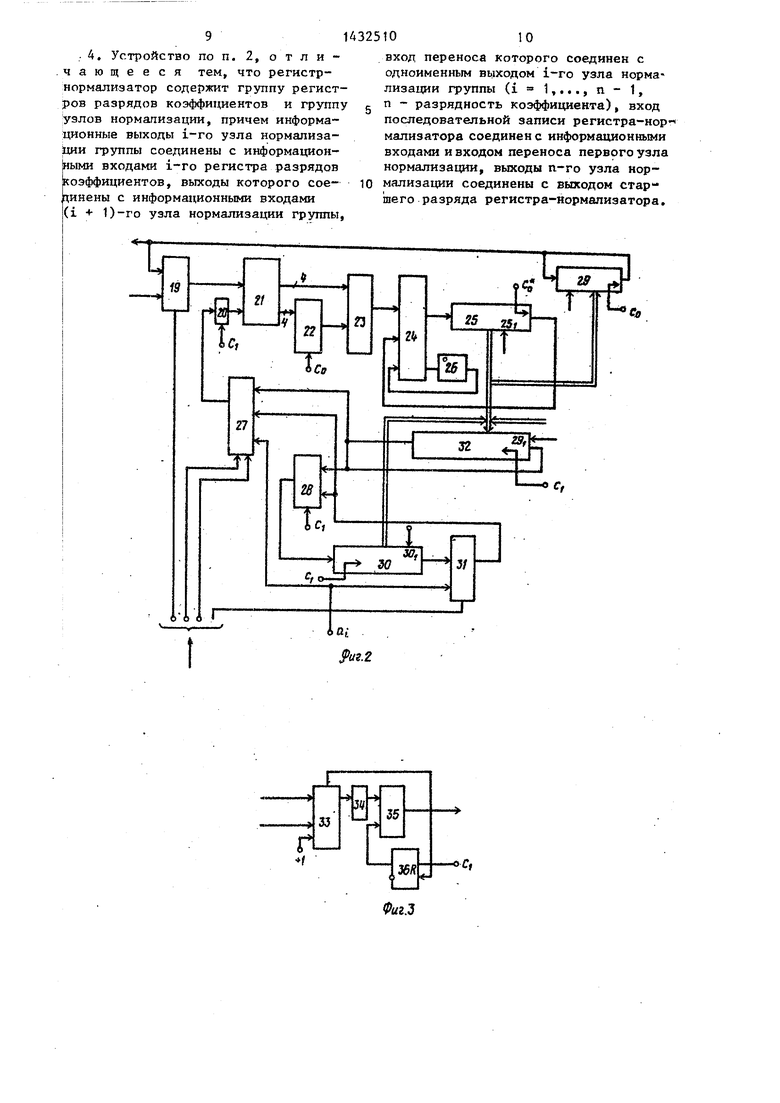

Регистр-нормализатор содержит узлы 45.1-45.п нормализации группы, регистры 46.1-46,п разрядов коэффи- даентов группы.

Устройство функционирует следзпо- щим образом.

Для вычисления функции используют разложение в степенной ряд. Степенные ряды легко преобразуются в рекуррентную форму, что позволяет определенным повтором однотипных вычислений добиваться требуемой точности. Однако в рекуррентную формулу входят постоянные коэффициенты а.

а

fcU,,,

0,1,.,.

При изменении точности воспроизведения функции разрядность коэффициентов должна меняться. Это обстоятельство сдерживает внедрение систем аппаратного воспроизведения функций произвольной (априори неизвестной) точности из-за существенного роста памяти при ориентации на максимальную разрядность из-за ограничения общего числа коэффициентов, т.е. количества членов ряда. Второе ограни- чение достаточно просто можно преодолеть путем изменения интервала так, чтобы имеющееся множество коэффициентов обеспечило заданную точность.

Для преодоления первого ограничения используют тот факт, что коэффи- хщенты а являются обратной величиной целых чисел малой разрядности. Такая дробь всегда может быть заменена десятичной, в общем случае бесконечной, периодической дробью. Значения дробей для двух типов коэффициентов следующие:

1

2k(2k - 1)

а

1

2k(k + 1)

а

Таким образом, для формирования коэффициента с требуемым числом разрядов необходимо определенное количество раз повторить период,

В десятичной дроби сзществует две части - неповторяющаяся часть а, и повторяющаяся часть а (взята в скобки). Поэтому перед считыванием периодической части вначале выбирается непериодическая часть числа.

Пусть заданное число разрядов помещено в первый р егистр 1, а в счетчик 12 - адрес коэффициента старшего

члена ряда. Из первого блока 3 памяти с первого выхода считывается начальный адрес АО коэффициента а,, по которому он хранится в блоке 3 постоянной памяти. На втором выходе счи- тьшается конечный адрес, т.е. адрес, по которому заканчивается период повторения коэффициента.

:р - 1,

где Р 1 + to 1

1 - длина непериодической части; U - длина периода.

На втором выходе блока постоянной памяти формируется адрес начала периода

гер 10 в единичное состояние, и выбор разрядов продолжается анапогич- но указанному.,

Указанньй процесс продолжается до тех пор, пока полностью не считьшается коэффициент а . На этом вычисление степенного разряда заканчивается.

Блок формирования результата работает в десятичной системе и реализует два алгоритма

и,ч. 3; .; у,.,,. у, +Uj,, , У.1 о; и y,.z,

где Z - либо аргумент х, либо невязка

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления экспоненциальной функции | 1986 |

|

SU1465884A1 |

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство вычисления функции @ @ с исправлением ошибок | 1984 |

|

SU1288690A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Устройство таймеров | 1983 |

|

SU1163309A1 |

Изо бретение относится к вычислительной технике и может быть применено в качестве функционального расширителя при вычислении широкого класса функций. Целью изобретения является повьппение точности вычислений. Устройство содержит первый регистр 1, блок 2 формирования результата, первый блок 3 памяти, первую схему сравнения 4, блок 5 формирова- НИЛ адреса коэффициента, второй блок 6 памяти, первый счетчик 7, элемент задержки 8, первый элемент И 9, триггер 10, второй элемент И 11, второй счетчик 12, вход 13 аргумента, второй регистр 14, вторую схему сравнения 15, вход 16 разрядности, вход 17адреса первого коэффициента, блок 18управления. 3 з.п. ф-лы, 6 ил. 3

А;

А - 1.

Адрес АО записывается в блок 5 формирования как начальное состояние По нему считьшается первый разряд коэффициента, который поступает в блок 2 формирования, результата. После вьтолнения операции над разрядом блок 18 управления формирует сигнал, и счетчики 12 и 40 наращиваются на 1. Вновь считывается следующий разряд коэффициента а и продолжает вьшолняться требуемая операция. Од- повременно сравнивается содержимое счетчика 40 с кодом на третьем выход первого блока 3 памяти. Если коды равны, это означает, что достигнута нижняя граница периода. Формируется сигнал с выхода схемы сравнения, и код со второго выхода первого блока 3 памяти в следующем такте записьша- ется в счетчик 40. Кроме того, срав- нивается содержимое первого счетчика 7 и первого регистра 1. Если сравнение проходит, т.е. обработано требуемое число разрядов, срабатывает первая схема 4 сравнения и сбрасывае в .нуль счетчик 40, триггер 10 и первый счетчик 7.

В следующем такте содержимое второго ; счетчика 12 уменьшается на 1, т.е. осуществляется переход на еле- дующий коэффициент (а„), и из первого блока 3 памяти считьшается вся необходимая адресная информация по коэффициенту ag. Начальный адрес Ag записьшается в счетчик 40. После - окончания всех переходных процессов на выходе элемента 8 задержки появляется сигнал, который сбрасьшает триг

20

(,

fc-; - t-i0

5

0

5

0

5

U 0; i 0,1,2,..., k - 1.

При реализации первого алгоритма Z заносится во второй регистр 14 и регистр 29 блока формирования результата. Текущий разряд записьшается в . первый регистр 20 блока формирования результата.

Затем происходит умножение этого разряда на число, хранимое во втором регистре 14. Множимое подается мпад- шими разрядами вперед. Разряды множителя последовательно записываются в первый регистр 20 блока формирования результата. Это происходит с помощью З множителя 21 и первого сумматора 23. Полученная на выходе последнего цифра - цифра частного произведения и она суммируется с текущим произведением, хранимым в накопителе, состоящем из второго сумматора 24 и третьего регистра 25. После получения полного произведения оно записьшается в регистр 32, и происходит умножение полученного результата на коэффициент а-. Произведение из регистра 32 поступает мпадшими разрядами вперед. После п тактов заканчиваются цикл формирования переменной U., и переход на следующий цикл. Одновременно с пост туплением U на первый регистр 20 они поступают на накопитель,состоящий из сумматора 28 старших разрядов и регистра-нормализатора 30. При суммировании двух десятичных цифр на сумматоре 33 к результату добавляется единица, сумма помещается в сумматоре 35. Затем с -ммируются следующая

51

пара разрядов и перенос. Если из сумматора ЗЛ возник перенос, он сбрасывает триггер 36 в нуль, и содержимое проходит на выход без .изменений, в npioTHBHoM случае вычитается единица. В результате может возникнуть случай ко|Гда возникает отрицательная цифра. Дл;я устранения этого в регистре-нормализаторе 30 между каждым разрадом пЬставлен узел 45.1-45.п нормализации. Назначение узла нормализации - вьчесть единицу, если из текущего разряда при наличии переноса в прсды

дущем к поступлению каждого нового ра(3ряда все ранее поступившие разря- дь| нормализованы.

Ф|ормула изобретения

I

1, Вычислительное устройство, содержащее два блока памяти, первый сметчик, первую схему сравнения, первый регистр и элемент задержки, причем выходы первого счетчика и перво- г4 регистра соединены с входами со- о ветственно первого и второго опе- р4ндов первой схемы сравнения, вход разрядности первого регистра устройства соединен с информационным в:1содом первого регистра, о т л и повышения точности вычисления, в него дфполнительно введены второй счетчик,

вторая схема сравнения, второй ре- - , . .

rjiCTp, триггер, два элемента И, блок рядности блока управления соединен ф)рмирования адреса коэффициента, с одноименным входом устройства.

25 ния, hepвый, второй и третий выход блока управления соединены с входа ми записи соответственно регистра, второго регистра и второго счетчика четвертый выход блока управления соединен с вторым входом записи опе ранда блока формирования адреса ко фициента, пятый выход блока управле ния соединен со счетным входом первого счетчика и первыми входами пер вого и второго элементов И, РУОД ра

6JJIC

IOK формиро1зания результата, блок управления, причем вход адреса перво- гЬ коэффициента устройства соединен С; входом записи второго счетчика, вы- хЬд которого соединен с адресным вхо- дЬм первого блока памяти, первый и второй выходы которого соединены с вводами соответственно первого и второго операндов блока формирования адреса .коэффициента, третий выход б)пска памяти соединен с входом первого операнда второй схемы сравнения, в1ход второго операнда которой соединеи, с выходом блока формирования адреса коэ ициента и объединен с адресным входом второго блока памяти, выход которого соединен с входом коэффициента блока формирования результата, вход начального значения которого соединен с входом аргумента устройства и объединен с информационньм входом второго регистра, выход младшего

40

45

50

55

шестой выход блока управления соеди нен с управляющими входами коммута тора блока формирования результата седьмой выход блока управления соединен с входом сдвига второго регис ра, первый и второй тактовые входы блока формирования результата соеди нены соответственно с седьмым и пятым выходами блока управления, выхо ды с восьмого по двенадцатый которо го соединены с тактовыми входами бл ка формирования результата соответственно с третьего по седьмой.

5

- , . .

разряда которого соединен с входом последовательной записи второго ре- (гистра и входом аргумента блока фор- ьофования результата, выход признака Равно первой схемы сравнения соединен с входом сброса триггера, входом сброса счетчика и входом призна- ка достижения разрядности блока управления, инверсный и прямой выходы триггера соединены с первыми входами соответственно первого и второго элементов И, выход первого элемента И через элемент задержки соединен с входом установки триггера, с вычитающим входом второго счетчика и первым входом записи операнда блока формирования адреса коэффициента, выход второго элемента И соединен с

Q тактовым входом блока формирования адреса коэффициентад вход сброса и вход запрета которого соединены с выходами признака Равно соответственно первой и второй схем сравне5 ния, hepвый, второй и третий выходы блока управления соединены с входами записи соответственно регистра, второго регистра и второго счетчика, четвертый выход блока управления соединен с вторым входом записи операнда блока формирования адреса коэффициента, пятый выход блока управле- ния соединен со счетным входом пер . вого счетчика и первыми входами вого и второго элементов И, РУОД раз0

шестой выход блока управления соединен с управляющими входами коммутатора блока формирования результата, седьмой выход блока управления соединен с входом сдвига второго регистра, первый и второй тактовые входы блока формирования результата соединены соответственно с седьмым и пятым выходами блока управления, выходы с восьмого по двенадцатый которого соединены с тактовыми входами блока формирования результата соответственно с третьего по седьмой.

управляющим входом первого коммутатора, первый информационный вход которого соединен с входом аргуме«та блока формирования результата, выход первого коммутатора ссигдинен с входо первого сомножителя умножителя, вход второго сомножителя которого соединен с выходом,первого регистра блока формирования результата, выход младших разрядов произведения умножителя соединен с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с выходом второго регистра блока формирования результата, информационный вход второго регистра данного блока соединен с выходом старших разрядов произведения умножителя, выход первого сумматора соединен с входом первого слагаемого второго сумматора, nepBbii-t выход которого соединен с информационным входом третьего регистра, выход младших разрядов которого соединен с входом второго слагаемого второго сумматора, вход третьего слагаемого которого соединен через элемент .задержки с вторым выходом этого сумматора, параллель- иый выход третьего регистра соединен с информационными входами четвертого и пятого регистров, выход младшего разряда четвертого регистра соединен с входом последовательной записи данного регистра и вторым информационным входом первого коммутатора, выход которого соединен с информационным входом первог-о регистра, выход старшего разряда пятого регистра соединен с входом последовательной записи данного регистра, с входом первого слагаемого сумматора разрядов и с первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом третьего коммутатора, первый информационный вход которого объе- динен с третьим информационным входом второго коммутатора и соединен i входом коэффициента блока формирова- ,ния результата, второй информационный вход третьего коммутатора которого соединен с выходом старших разрядов регистра-нормализатора, вход последовательной записи которого соединен с выходом сумматора старших разрядов, вход второго слагаемого которого соединен с выходом третьего коммутатора, параллельный выход регистра0

5

0

5

0

5

0

5

0

5

нормализатора соединен с информационным входом четвертого регистра, второй и третий управляющие входы коммутации блока формирования результата соединены с управляющими входами второго коммутатора, четвертый угфав- ляюпщй вход коммутации блока формирования результата соединен с управляющим входом третьего коммутатора, первый тактовый вход блока формиро- .вания результата соединен с входами сдвига второго и четвертого регистров блока формирования результата, входы iсдвига пятого регистра,, регистра- iнормализатора, вход синхронизации первого регистра блока формирования результата и синхронизирующий вход сумматора старших рйзрлдсв сосдппетты с вторым тактовым входом блока формирования результата, вход сдвига третьего регистра соединен с третьим тактовым входом блока формирования результата, синхронизируюш е входы третьего, четвертого, пятого регистров и регистра-нормализатора соединены с. тактовыми входами с четвертого по седьмой соответственно, выход первого регистра блока фор- шpoвaния результата соединен с вхо- . дом второго сомножителя умножителя, информационный вход пятого регистра соединен с входом начального значения блока формирования результата.

3, Устройство по п. 2, о т л и- чающееся тем, что сумматор старших разрядов содержит два комбинационных сумматора, триггер и элемент задержки, причем входы первого и второго слагае к сумматора старших разрядов соединены с входами соответственно первого и второго слагаемых первого комбинационного сумматора, вход третьего слагаемого которого соединен с входом константы 1, выход первого комбинационного с мматора через элемент задержхск ;соединен .с входом первого слагаемого второго комбинационного сумматора, вход второго слагаемого которого соединен с прямым выходом триггера, вход сброса которого соединен с Iвыходом переполнения первого комбинационного сумматора, вход установки триггера соединен с синхронизирующим входом сумматора старших разрядов, выход второго комбинациоя- ного сумматора соединен с выходом . сумматора старших разрядов.

9

. 4. Устройство по п. 2, отли чающееся тем, что регистр- нормализатор содержит группу регистров разрядов коэффициентов и групп узлов нормапизации, причем информационные выходы i-ro узла нормализации группы соединены с информационными входам1И i-ro регистра разрядов Коэффициентов, выходы которого соединены с информационными входами (i + 1)-го узла нормализации группы

Г

Г

10

10

вход переноса которого соединен с одноименным выходом i-ro узла норма- лизации группы (i 1,..., п - 1, п - разрядность коэффициента), вход последовательной записи регистра-нормализатора соединено информационными входами и входом переноса первого узла нормализации, выходы п-го узла нормализации соединены с выходом старшего разряда регистра-нормализатора.

Й/г4

иг.5

Фие:б

| Устройство для вычисления функции @ | 1985 |

|

SU1305671A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления полинома @ -ой степени | 1983 |

|

SU1140115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-12-24—Подача