первого и второго узлов формирования переноса соответственно, выходы второго и третьего разрядов результата третьего четырехразрядного сумматора соединены с вторыми входами соответственно первого и второго элементов И первого узла формирования переноса, выходы второго и третьего разрядов результата четвертого четырехразрядного сумматора соединены с вторыми входами соответственн.о первого и ;Втррого элементов И второго узла формирования.переноса, выходы переноса третьего и четвертого четырехразрядных сумматоров соединены с третьими входами первого и второго узлов формирования переноса соответственно, выход элемента ИЛИ первого узла формирования переноса и выходы суммы четвертого четырехразрядного сумматора соединены с соответствующрши информационньми

входами первой группы узла формирования контрольного разряда, выход элемента ИЛИ первого узла формирования переноса соединен с вторым входом второго элемента И, третьи входы первого и второго элементов И, первого и второго узлов формирования переноса объединены с входом задания вида суммирования устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены элемент ИЛИ, третий коммутатор, узел контроля, содержащий два элемента НЕ, два элемента И и сумматор по модулю два, узел предсказания переноса, содержащий четыре элемента И и элемент ИЛИ, и два узла десятичной коррекции, каждый из которых содержит два элемента НЕ, элемент И, элемент ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, причем в узле контроля выходы первого и второг элементов НЕ соединены с первыми входами соответственно первого и второго элементов И, выходы которых сое, динены с соответствующими входами сумматора по модулю два, в узле предсказания переноса выходы первого, второго, третьего и четвертого элементов И соединены с первым, вторым, третьим и четвертым входами элемента ИЛИ, в каждом узле десятичной коррекциивыход первого элемента НЕ соединен с первым входом элемента И, второй вход которого объединен с входом второго элемента НЕ. и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ6874

НЕ, входы переноса первого и второго четырехразрядных сумматоров соединены соответственно с шинами нулевого и единичного потенциалов, выходы суммы первого и второго четырехразрядных сумматоров соединены соответственно с первой и второй группами информационных входов третьего коммутатора, управляющий вход которого соединен с вьбсодом элемента ИЛИ второго узла формирования переноса, .выходы суммы и выходы переноса пер.вого и второго четырехразрядных сумматоров соединены с соответствующими входами сумматора 43 по модулю два узла 5 контроля, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом узла сравнения , выход элемента ИЛИ является выходом ошибки двоичного суммирования устройства, выходы первого, второго, третьего и четвертого разрядов суммы первого четырехразрядного сумматора соединег ны соответственно с входом первого элемента НЕ, вторьм входом первого элемента И, входом второго элемента НЕ и вторым входом второго элемента И узла контроля, в последнем третий и четвертый входы первого элемента И объединены соответственно с входом второго элемента НЕ и вторым входом второго элемента И, в узле предсказания переноса первый.,. второй и третий входы первого элемента И объединены соответственно с первым входом третьего элемента И.и первым и вторым входа ми второго элемента И, второй вход третьего элемента И объединен с первым входом четвертого элемента И, выходы первого, второго, третьего и четвертого разрядов суммы первого четырехразрядного сумматора соединены соответственно с первым и вторым входами первого элемента И, третьим входом второго элемента И и третьим входом третьего элемента И узла предска зания переноса, вход задания вида суммирования устройства объединен с третьим входом первого элемента И узла предсказания переноса, выход элемента ИЛИ первого узла формирования переноса и выходы переноса первого и второго четырехразрядных сумматоров соединены соответственно с вторым входом третьего элемента И, пятым входом элемента ИЛИ. и вторым входом четвертого элемента И узла предсказания переноса. выход элемента ИЛИ которого является выходом переноса устройства, выходы третьего коммутатора соединены с первой группой входов первого коммутатора, выходы первого, второго, третьего и четвертого разрядов третьего коммутатора соединены соответственно с цервым входом элемента ИЛИ, входом второго элемента НЕ, вторым, входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и входом первого элемента НЕ первого узла де-г сятичной коррекции, выходы которого соединены с соответствующими информационными входами второй группы входов первого коммутатора, выходы первого, второго, третьего и четвертого разрядов суммы третьего четырех разрядного сумматора соединены, соответственно с первым входом элемента ИЛИ, входом второго элемента НЕ, вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и входом первого элемента НЕ второго узла десятичной коррекции, выходы которого соединены с соответствующими информационными входами второй группы входов второго коммутатора, выход элемента ИЛИ узла предсказания переноса и выходы третьего коммутатора- соединены с соответствующими информационными входами второй группы входов узла формирования контрольного разряда, выхгод элемента ИЛИ узла предсказания, переноса соединен с BTopbiM входом первого элемента И..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1979 |

|

SU911505A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Двоично-десятичный сумматор | 1990 |

|

SU1728859A1 |

КОНТРОЛИРУЕМОЕ УСТРОЙСТВО ДЛЯ ДВОИЧНО-ДЕСЯТИЧНОГО СУММИРОВАНИЯ, содержащее четыре четырехразрядных сумматора, два коммутатора, два элемента И, узел свертки по модулю два, узел сравнения,.узел формирования контрольного разряда и два узла формирования переноса, каждый из которых содержит два элемента И. и элемент ИЛИ, причем в каждом из узлов формирования переноса выходы первого и второго элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, входы первого слагаемого первого и второго четырехразрядных сумматоров объединены, входы второго слагаемого первого и второго четырехразрядных сумматоров объединены, входы первого слагаемого третьего и четвертого четырехразрядных сумматоров объеди-. нены, входы второго слагаемого тр.етьего и четвертого четырехразрядных сумматоров объединены, входы первого слагаемого первого и третьего четырехразрядных сумматоров образуют группу входов первого слагаемого устройства, входы второго слагаемого первого и третьего четырехразрядных сумматоров образуют группу входов второго слагаемого устройства, входы переноса третьего и четвертого четырехразрядных сумматоров объединены и являются входом переноса уст.ройства, выход переноса и выходы суммы третьего и четвертого четырехразрядных сумматоров соединены соответственно с первой и второй группами информационных входов узла сравнения, входы задания вида суммирования всех четырехразрядных сумматор/эв и узла формирования контрольного , разряда и первые входы первого и второго элементов И объединены и являются входом задания вида суммирования устройства, выходы первогои второго элементов И соединены соответственно с управляющими входами .первого и второго коммутаторов, выходы которых образуют группу информационных выходов устройства, СО выход узла формирования контрольногоО) разряда является выходом контрольного разряда устройства, выходы перво00 го и второго коммутаторов и выход узда формирования контрольного раз4 ряда соединены с соответствующими входами узла свертки по модулю два, выход которого является выходом ошибки результата устройства, группа выходов.результата третьего четырехразрядного сумматора соединена с первой, группой информационных входов второго коммутатора, выходы четвертых разрядов результата третьего и четвертого четырехразрядных сумматоров соединены с первыми входами первого и второго элементов И

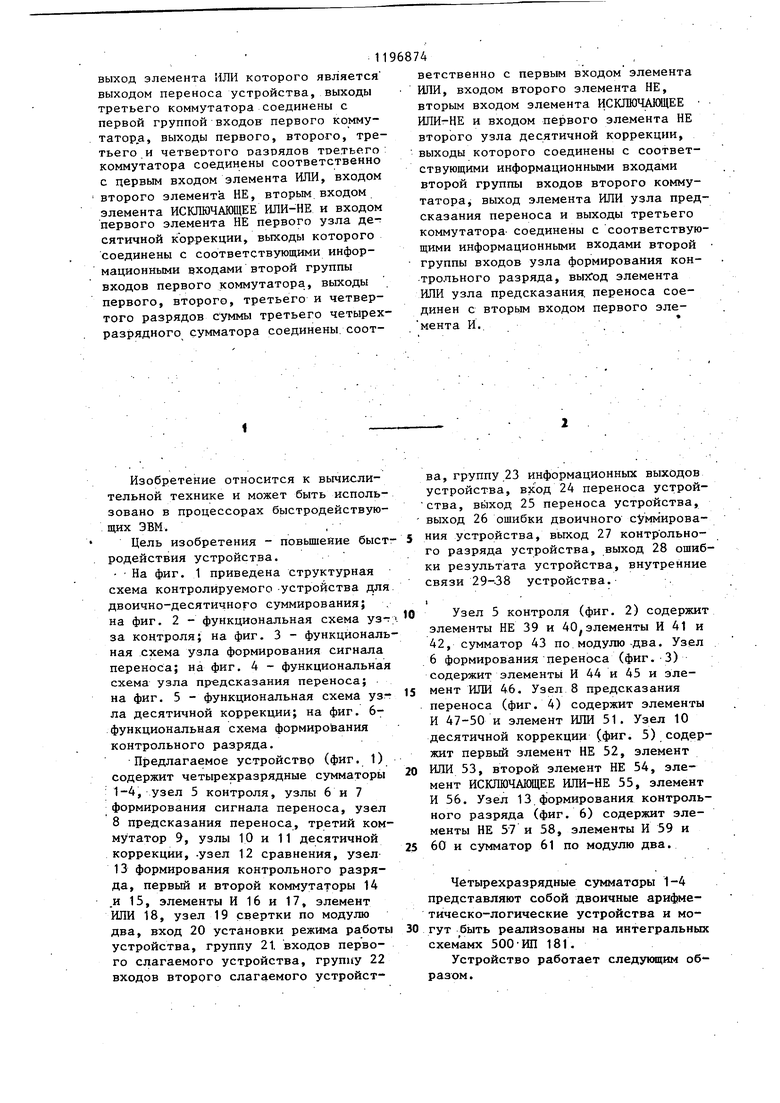

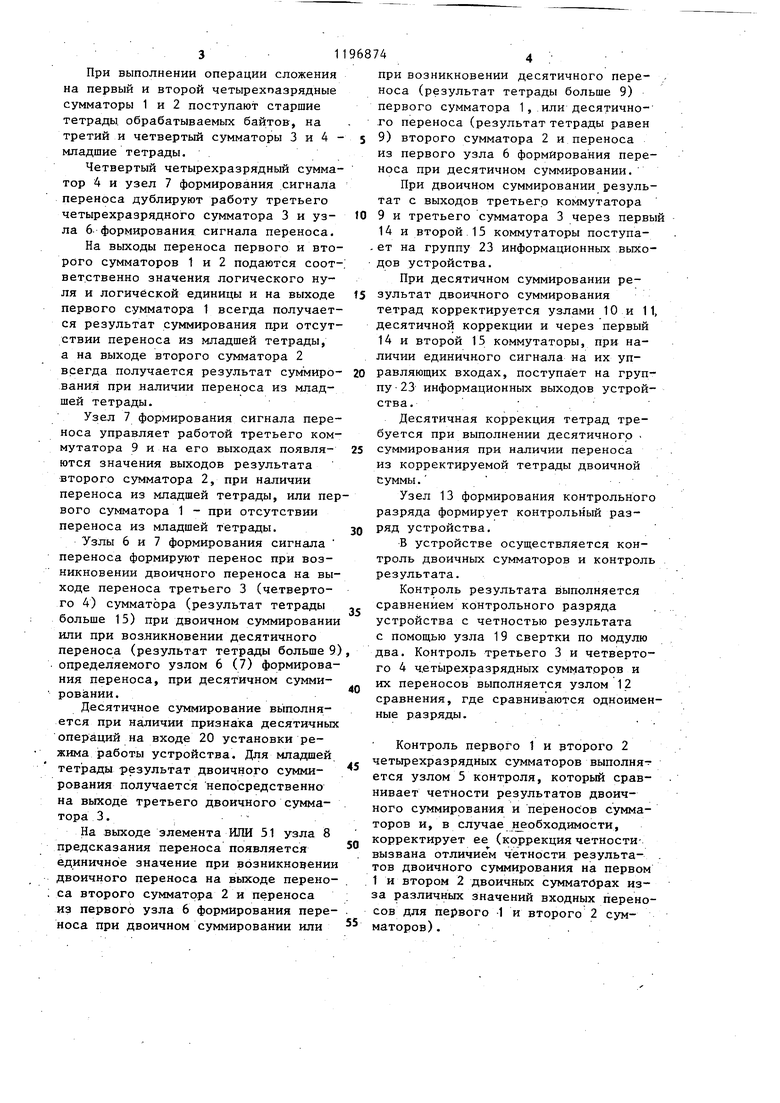

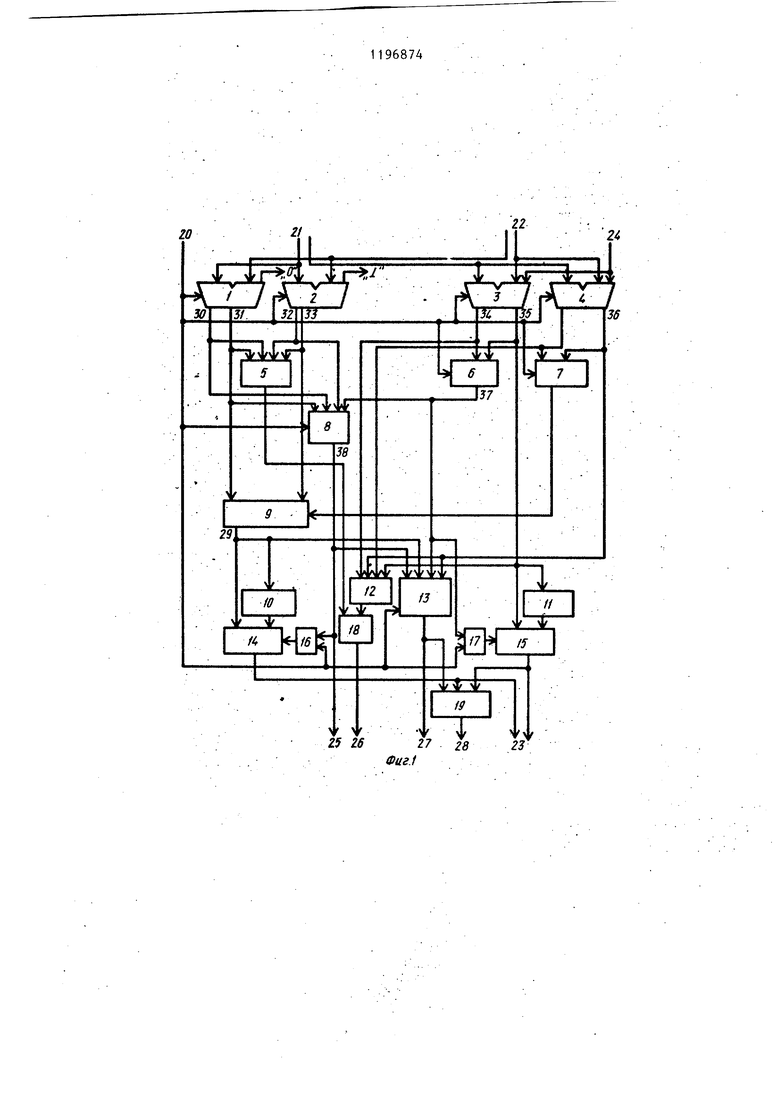

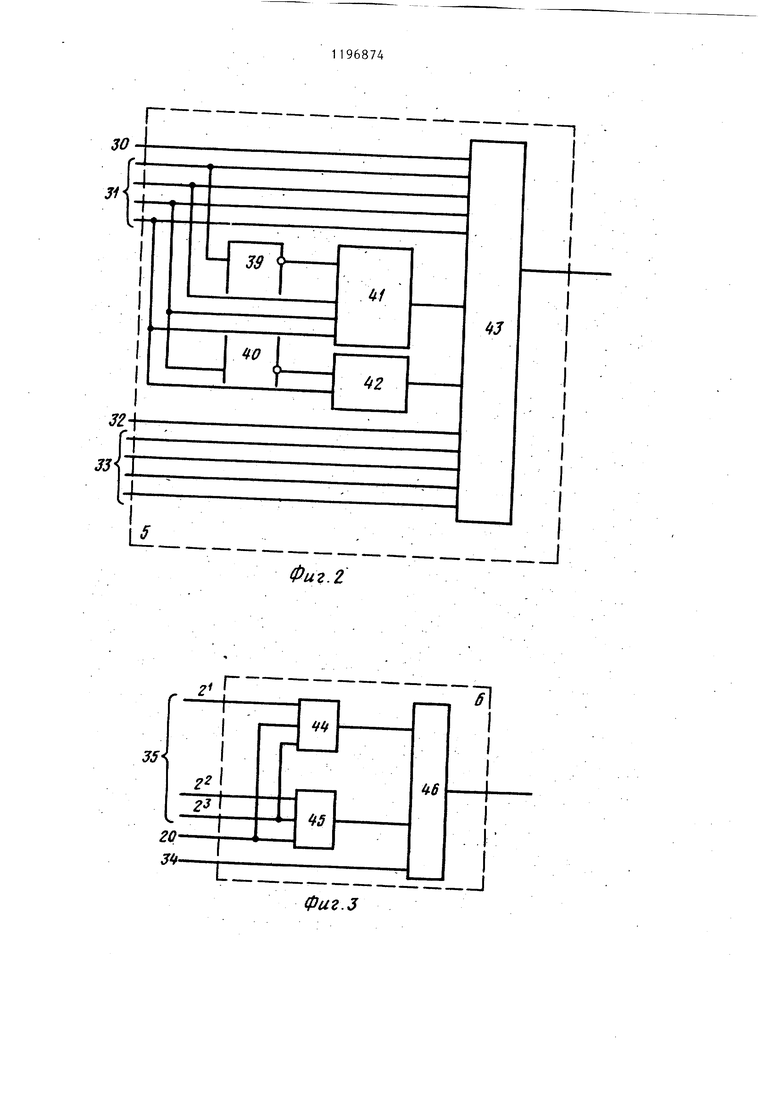

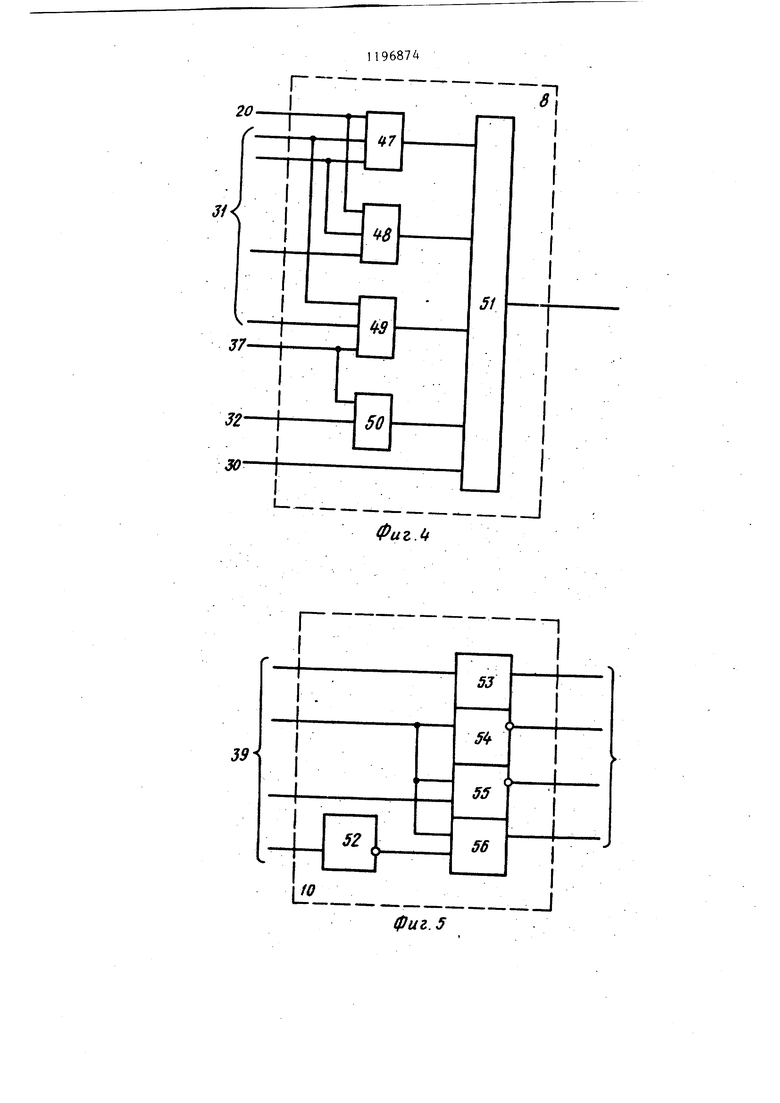

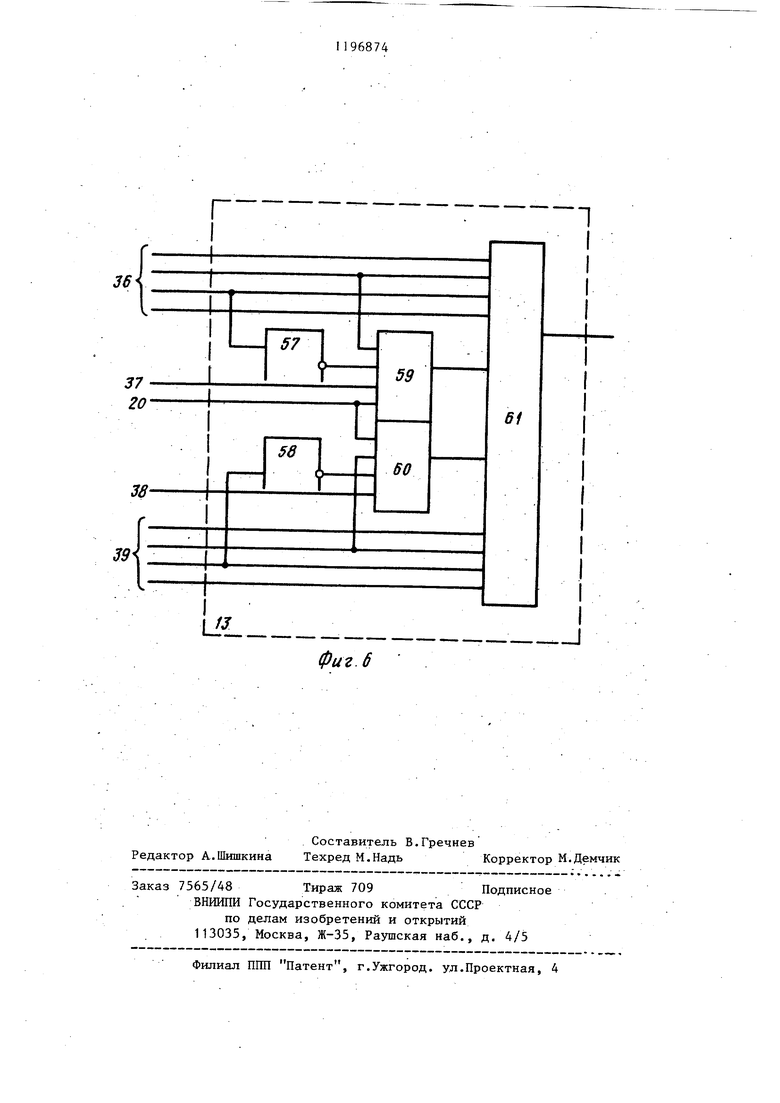

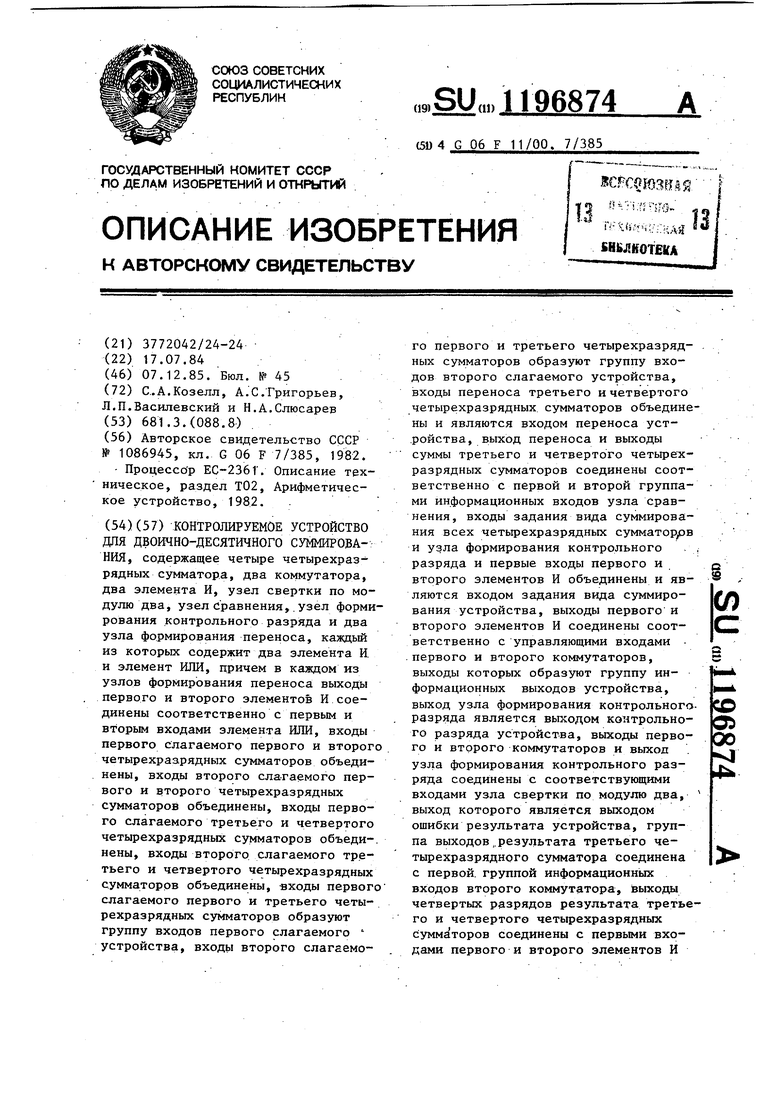

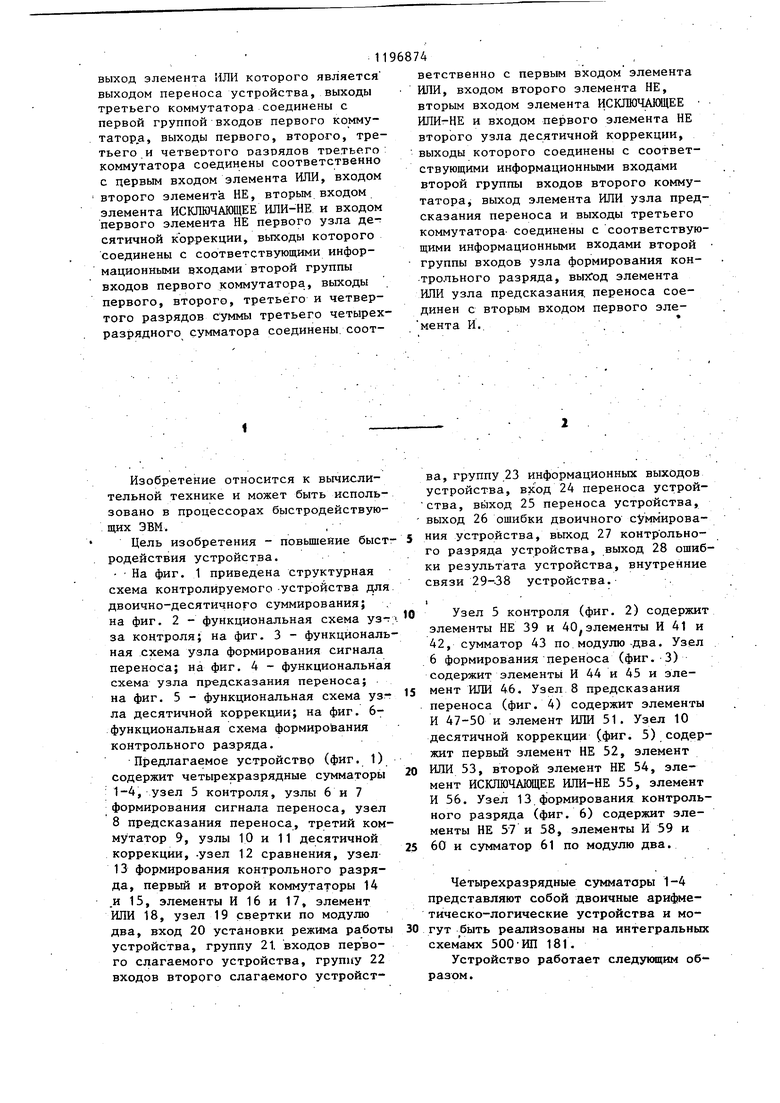

Изобретение относится к вычислительной технике и может быть использовано в процессорах быстродействующих ЭВМ,, Цель изобретения - повьшение быст родействия устройства. На фиг. 1 приведена структурная схема контролируемого устройства для двоично-десятичного суммирования; на фиг. 2 - функциональная схема узза контроля; на фиг. 3 - функциональ ная схема узла формирования сигнала переноса; на фиг. 4 - функциональная схема узла пр-едсказания переноса; на фиг. 5 - функциональная схема узла десятичной коррекции; на фиг. 6функциональная схема формирования контрольного разряда. Предлагаемое устройство (фиг. 1) содержит четырехразрядные сумматоры 1-4, узел 5 контроля, узлы 6 и 7 формирования сигнала переноса, узел 8 предсказания переноса, третий ком мутатор 9, узлы 10 и 11 десятичной коррекции, .узел 12 сравнения, узел 13 формирования контрольного разряда, первый и второй коммутаторы 14 .и 15, элементы И 16 и 17, элемент ИЛИ 18, узел 19 свертки по модулю два, вход 20 установки режима работы устройства, группу 21. входов первого слагаемого устройства, группу 22 входов второго слагаемого устройства, группу 23 информационных выходов устройства, вход 24 переноса устройства, выход 25 переноса устройства, выход 26 ошибки двоичного суммирования устройства, выход 27 контрольного разряда устройства, выход 28 ошибки результата устройства, внутренние связи 29-38 устройства. Узел 5 контроля (фиг. 2) содержит элементы НЕ 39 и 40 элементы И 41 и 42, сумматор 43 по модулю-два. Узел 6 формирования переноса (фиг. 3) содержит элементы И 44 и 45 и элемент ИЛИ 46. Узел 8 предсказания переноса (фиг. 4) содержит элементы И 47-50 и элемент ИЛИ 51. Узел 10 десятичной коррекции (фиг. 5) содержит первый элемент НЕ 52, элемент ИЛИ 53, второй элемент НЕ 54, элемент ИСКЛЮЧАЩЕЕ ИЛИ-НЕ 55, элемент И 56. Узел 13 формирования контрольного разряда (фиг. 6) содержит элементы НЕ 57 и 58, элементы И 59 и 60 и сумматор 61 по модулю два. Четырехразрядные сумматоры 1-4 представляют собой двоичные арифметическо-логические устройства и могут быть реализованы на интегральных схемамх 500-ИЛ 181. Устройство работает следующим образом.

, 3 1

При выполнении операции сложения на первый и второй четырехпазрядные сумматоры 1 и 2 поступают старшие тетрады, обрабатываемых байтов, на третий и четвертый сумматоры 3 и 4 младшие тетрады.

Четвертый четырехразрядный сумматор 4 и узел 7 формирования сигнала переноса дублируют работу третьего четырехразрядного сумматора 3 и узла 6 формирования сигнала переноса.

На выходы переноса первого и второго сумматоров 1 и 2 подаются соответственно значения логического нуля и логической единицы и на выходе первого сумматора 1 всегда получается результат суммирования п,ри отсутствии переноса из младшей тетрады, а на выходе второго сумматора 2 всегда получается результат суммирования при наличии переноса из младшей тетрады.

Узел 7 формирования сигнала переноса управляет работой третьего коммутатора 9 и на его выходах появляются значения выходов результата второго сз матора 2, при наличии переноса из младшей тетрады, или первого сумматора 1 - при отсутствии переноса из младшей тетрады.

Узлы 6 и 7 формирования сигнала переноса формируют перенос при возникновении двоичного переноса на выходе переноса третьего 3 (четвертого 4) сумматора (результат тетрады больше 15) при двоичном суммировании или при возникновении десятичного переноса (результат тетрады больше 9 определяемого узлом 6 (7) формирования переноса, при десятичном суммировании.

Десятичное суммирование выполняется при наличии признака десятичных операций на входе 20 установки режима работы устройства. Для младшей тетрады результат двоичного суммирования получается непосредственно на выходе третьего двоичного сумматора 3.

На выходе элемента ИЛИ 51 узла 8 предсказания переноса появляется единичное значение при возникновении двоичного переноса на выходе переноса второго сумматора 2 и переноса из первого узла 6 формирования переноса при двоичном суммировании или

68744 ;

при возникновении десятичного пере- . носа (результат тетрады больше 9) первого сумматора 1, или десятичного переноса (результат тетрады равен 5 9) второго сумматора 2 и переноса из первого узла 6 формирования переноса при десятичном суммировании.

При двоичном суммировании результат с выходов третьего коммутатора 10 9 и третьего сумматора 3 через первый

1А и второй 15 коммутаторы поступа.ет на группу 23 информационных выходов устройства.

При десятичном суммировании реfS зультат двоичного суммирования

тетрад корректируется узлами 10 и 11, десятичной коррекции и через первый 14 и второй 15 коммутаторы, при наличии единичного сигнала на их управляющих входах, поступает на группу 23 информационных выходов устройства. .

Десятичная коррекция тетрад требуется при выполнении десятичного . 5 суммирования при наличии переноса из корректируемой тетрады двоичной суммы. , .

Узел 13 формирования контрольного разряда формирует контрольный разряд устройства.

В устройстве осуществляется контроль двоичных сумматоров и контроль результата.

Контроль результата выполняется сравнением контрольного разряда устройства с четностью результата с помощью узла 19 свертки по модулю два. Контроль третьего 3 и четвертого 4 четырехразрядных сумматоров и д их переносов выполняется узлом 12

сравнения, где сравниваются одноименные разряды.

Контроль первого 1 и эторого 2 е четырехразрядных сумматоров выполняется узлом 5 контроля, который сравнивает четности результатов двоичного суммирования и переносов сумматоров и, в случае 11еобходимости,

корректирует ее (коррекция четностивызвана отличием четности результа- . тов двоичного суммирования на первом 1 и втором 2 двоичных сумматорах изза различных значений входных переносов для первого -1 и второго 2 сумматоров)..

21

ZO

2S 2627 2823

22

24

Фиг.)

iL...

Фи2.2

фиг.З

Г

.J

ФигМ

п

фиг.

Г

ilL

фиг. 6

| Авторское свидетельство СССР № 1086945, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Химический огнетушитель | 1925 |

|

SU2361A1 |

| Описание техническое, раздел Т02, Арифметическое устройство, 1982. | |||

Авторы

Даты

1985-12-07—Публикация

1984-07-17—Подача