(Sk ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ Б ДВОИЧНЫЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичныхчиСЕл B дВОичНыЕ C МАСшТАбиРОВАНиЕМ | 1979 |

|

SU822173A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Преобразователь двоичных чисел в двоично-десятичные | 1987 |

|

SU1481897A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1221758A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1005027A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей .

Извегтен преобразователь двоичнодесятичноых чисел в двоичные, содержащий группу комбинационных сумматоров , входы сумматора одного яруса соединены с выходами сумматоров соседнего младшего яруса, входы сумматора первого яруса соединены с входами преобразователя, а выходы сумматора старшего яруса соединены с выходами преобразователя lj.

Недостаток этого преобразователя состоит в относительно большом количестве сумматоров, что увеличивает сложность преобразователя и время его работы.

Наиболее близким к предлагаемому по Технической сущности является преобразователь двоично-десятичных чисел в двоичные, содержащий сумматоры, ВЫХОДЫ младших разрядов которых соединены соответственно со вторым, третьим, шестым и седьмым разрядами группы выходов преобразователя,вход младшего разряда группы входов преобразователя соединен с первым разрядом группы выходов преобразователя, вход первого слагаемого второго разряда первого сумматора соединен с входом третьего разряда первой тет10рады группы входов преобразователя, входы первого и второго разрядов второй тетрады группы входов преобразователя соответственно соединены с входами первого слагаемого перво15го и третьего разрядов и вхолами второго слагаемого второго и четвертого разрядов первого сумматора, вход третьего разряда второй тетрады группы входов преобразователя соеди20нен с входами первого слагаемого второго и четвертого разрядов второго сумматора, вход четвертого разряда второй тетрады группы входов преобразователя соединен со входом первого слагаемого четвертого разряда первого сумматора, входы третьего и четвертого разрядов третьей тетрады группы входов преобразователя соответственно соединены с входами первого слагаемого третьего и четвертог разрядов третьего и четвертого сумматоров, выходы четвертого сумматора соединены со старшими разрядами груп пы выходов преобразователя, вуходы старших разрядов и выход переноса первого и третьего суммат.оров соединены с входами вторых слагаемых третьего и четвертого разрядов второго и четвертого сумматоров соответственно, вход третьего разряда третьей тетрады группы входов преобразователя соединен с входом первого слагаемого второго разряда второго сумматора 2. Недостаток данного преобразователя также состоит в большом количестве сумматоров и относительно невысоком быстродействии. Цель изобретения - упрощение преобразователя, и повышение его быстродействия. Поставленная цель достигается те что в преобразователь двоично-десятичных чисел в двоичные, содержащий сумматоры, выходы младших разрядов которых соединены соответственно с вторым, третьим, шестым и седьмым разрядами группы выходов преобразователя, вход младшего разряда группы входов преобразователя соединен непосредственно с первым разрядом гру пы выходов преобразователя, вход первого слагаемого второго разряда первого сумматора соединен с входом третьего разряда первой тетрады гру пы входов преобразователя, вЯоды первого и второго разрядов второй тетрады группы входов преобразовате

соединены соответственно с входами первого слагаемого первого и третьего разрядов и входами второго слагаемого второго и четвертого разрядов первого сумматора, вход третьего разряда второй тетрады группы входов преобразователя соединен с входами первого слагаемого второго и четвертого разрядов второго суммато.ра, вход четвертого разряда второй тетрады группы входов преобразователя соединен с входом первого слагаемого четвертого разряда первого

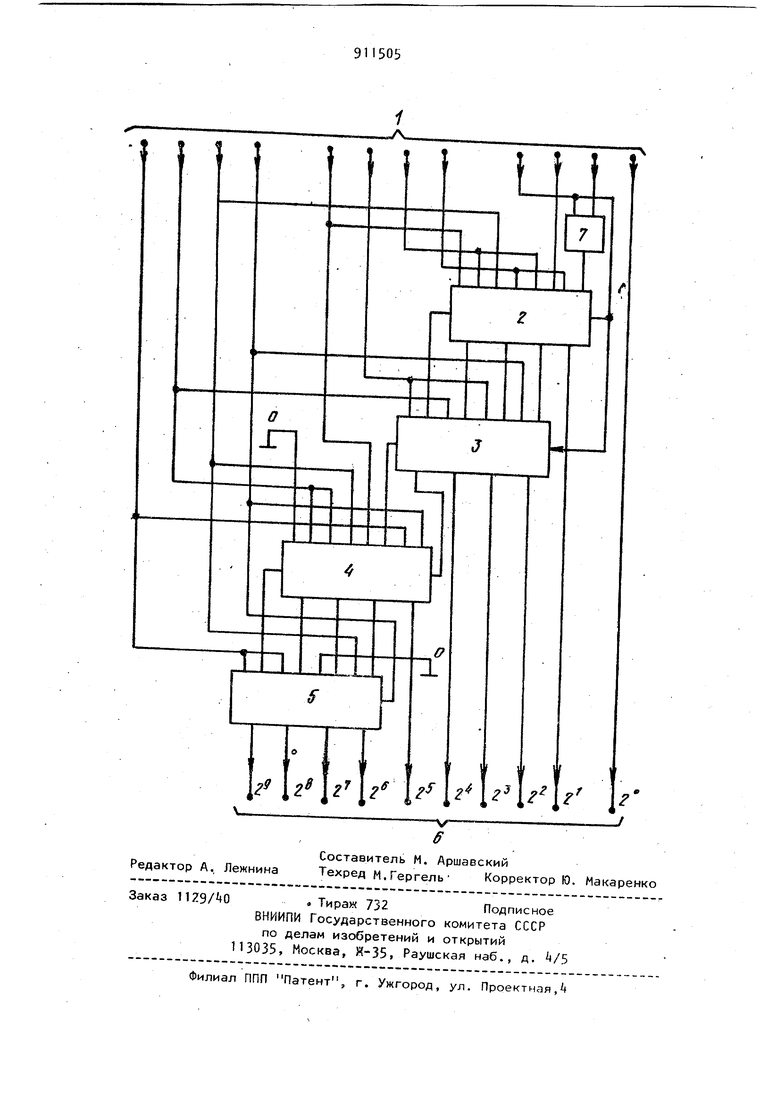

преобразователя соединен с входом второго слагаемого второго разряда третьего сумматора, вход первого разряда третьей тетрады группы входов феобразователя соединен с входами первого слагаемого первых разрядов второго и третьего сумматоров и входом переноса четвертого сумматора, входы второго слагаемого четвертого разряда третьего сумматора и первого слагаемого второго разряда четвертого сумматора соединены с входом тождественного нуля. сумматора, входы третьего и четвертого разрядов третьей тетрады группы входов преобразователя соответственно соединены с входами первогослагаемого третьего и четвертого разрядов третьего и четвертого сумматоров, выходы четвертого сумматора соединены со старшими разрядами группы выходов преобразователя, выходы старших разрядов и выход переноса первого и третьего сумматоров соединены с входами вторых слагаемых третьего и четвертого разрядов второго и Четвертого сумматоров соответственно, вход третьего разряда третьей тетрады группы входов преобразователя соединен с входом первого слагаемого второго разряда второго сумматора, введен элемент ИЛИ, первый вход которого соединен с входом четвертого разряда первой тетрады группы входов преобразователя и с входами переноса первого и второго сумматоров,второй вход элемента .ИЛИ соединен с входом второго разряда первой тетрады группы входов преобразователя, а выход элемента ИЛИ подключен к входу второго слагаемого первого разряда первого сумматора, вход второго разряда третьей тетрады группы входов преобразователя соединен с входами второго слагаемого третьего разряда первого сумматора, третьего разряда третьего сумматора и входом первого слагаемого первого разряда четвертого сумматора, выходы второго и третьего разрядов второго сумматора соединен с четвертым и пятым разрядами группы выходов преобразователя, выход четвертого разряда и выход переноса второго сумматора соединены с входом переноса и вх.одом первого слагаемого второго разряда третьего сумматора соответственно, вход четвертого раз-f---T-i- - --r---,r ряда второй тетрады группы входов 5 На чертеже приведена блок-схема предлагаемого преобразователя. Преобразователь содержит тетрады 1 группы входов преобразогателя, су маторы 2-5, выходы 6 преобразовател и элемент ИЛИ 7. Предлагаемый преобразователь осу ществляет параллельное преобразование кода, поступающего на входные шины, и по принципу работы является устройстбом комбинационного типа. Поэтому при подаче на вход устройст ва двоично-десятичного кода числа на его выходе немедленно вырабатыва ется двоичный код этого числа. Врем задержки установления выходного код определяете количеством операций ,суммирования, выполняемых при преоб разовании кодов. Для предлагаемого преобразователя количество операций суммирования по пятому, шестому и седьмому разрядам выходного кода уменьшено ё два раза по сравнению с прототипом за счет сокращения общего количества четырехразрядных сумматоров. Это, в свою очередь, до стигнуто за счет введения элемента ИЛИ, представления четвертого разря да кода младшей тетрады суммы двоичных чисел - 2; 2 и 2 и использования входов переноса суммато ров. В результате, например, время задержки установления пятого разряда выходного кода tг. для.предлагаемого устройства равно t ЗГ„-н задержка распространения по цепи переноса; задержка распространения по цепи суммы. Для схемы прототипа эта величина равна сумме 31 «t. Если задержка по цепи переноса приблизительно равна задержке по цепи суммы, то предлагаемое устройство имеет быстродействие в 1, раза выше чем у прототипа. В предлагаемом преобразователе количество сумматоров, необходимых для его. реализации схемы, сокращается на одну треть при одновременном повышении быстродействия.. 05 Формула изобретения Преобразователь двоично-десятичных чисел в двоичные, содержащий сумматоры, выходы младших разрядов которых соединены соответственно с вторым, третьим, шесгым И седьмым разрядами группы выходов преобразователя, вход младшего разряда группы входов преобразователя соединен непосредственно с первым разрядом группы выходов преобразователя, вход первого слагаемого второго разряда первого сумматора соединен с входом третьего разряда первой тетрады группы входов преобразователя, входы первого и второго разрядов в,орой тетрады группы входов преобразователя соответственно соединены с входами первого слагаемого первого и третьего разрядов и входами второго слагаемого второго и четвертого разрядов пер.вого сумматора, вход третьего разряда второй тетрады группы входов преобразователя соединен с входами первого слагаемого второго и четвертого разрядов второго сумматора, вход четвертого разряда второй тетрады группы входов преобразователя соединен с входом первого .слагаемого четвертого разряда первого сумматора, входы третьего и четвертого разрядов третьей тетрады группы входов преобразователя соеответственно соединены с входами первого слагаемого третьего и четвертого разрядов третьего и четвертого сумма;торов, выходы четвертого сумматора соединены с старшими разрядами группы выходов преобразователя, выходы старших разрядов и выход переноса первого и третьего сумматоров соеди нены с входами вторых слагаемых третьего и четвертого разрядов второго и четвертого сумматоров соответ- , ственно, вход третьего разряда третьей тетрады группы входов преобразователя соединен с входом первого слагаемого-второго разряда второго сумматораJ .отличающийся тем, что, с целью упрощения и повыения быстродействия, в него введен лемент ИЛИ, первый вход которого оединен с входом четвертого разяда первой тетрады группы входов реобразователя и с входами переноса ервого и второго сумма торс в, вГторой ход элемента ИЛИ соединен с входом торого разрялз первой тетрады

79

группы входов преобразователя, а выход элемента ИЛИ подключен к входу второго слагаемого первого разряда первого сумматора, вход второго разряда третьей тетрады группы входов преобразователя соединен с входами второго слагаемого третьего разряда первого сумматора, третьего разряда третьего сумматора и входом первого слагаемого первого разряда четвертого сумматора, выходы второго и третьего разрядов второго сумматора соединены с четвертым и пятым разрядами группы выходов преобразователя, выход четвертого разряда и выход переноса второго сумматора соединены с входом переноса и входом первого слагаемого второго разряда третьего сумматора соответственно, вход четвертого разряда

8

второй тетрады группы входов преобразователя соединен с входом второго слагаемого второго разряда третьего сумматора, вход первого разряда

третьей тетрады группы входов преобразователя соединен с входами первого слагаемого первых разрядов второго и третьего сумматоров и входом переноса четвертого сумматора, входы

второго слагаемого четвертого разряда третьего сумматора и первого слагаемого второго разряда четвертого сумматора соединены с входом тождественного нуля.

Источники информации,

принятые во внимание при экспертизе

w

Авторы

Даты

1982-03-07—Публикация

1979-02-23—Подача