генератора тактовых импульсов, соединенным также с первыми входами элементов И группы и третьего, четвертого элементов И, выходы вторых элементов И первого и второго блоков анализа соединены соответственно -С входами сброса первого и регистров, первые выходы дешифраторов группы соединены с вторыми входа1 и соответствующих элементов И группы, выходы которых соединены с входами сброса с второго

fio (1-2)-й и с (i + D-ro по (N-l)-ft регистров соответственно, а в каж- дом блоке анализа выход второго дешифратора соединен с вторым входом третьего элемента И, выход которого соединен с вторым (инверсным) входом первого элемента И, выход которого соединен с вторым входом

второго элемента ИЛИ, вьгходы вторых ешифраторов первого и второго блоков анализа соединены соответственно с первыми входами первого и второго элементов И и вторыми вхог ами третьего и четвертого элементов И, выходы перв.ого и второго элементов И соединены соответствено с первыми управляющими входами -ro и первого коммутаторов , выходы ретьего и четвертого элементов И

96885. .

соединены с входами сброса (1-1)-го и К -го регистров; соответственно, вторые выходы первых дешифраторов первого и второго блоков анализа соединены соответственно с первыми управляющими входами второго и (L + 1)-ro коммутаторов и вторыми входами соответственно первого и второго элементов И, выходы третьих элементов И первого и второго блоков анализа соединены соответственно с вторыми управлякщими входами 1-го и первого коммутаторов, выходы вторых элементов ИЛИпервого, и второго блоков анализа соединены соответственно с вторыми управляющими входами второго и (t-1)-ro коммутаторов, вторые выходы дешифраторов группы соединены соответственно с управляющими входами с третьего по (i-1)-ft и с (L+2)-ro по N-и коммутаторов, группы разрядных выходов первого и I. -го регистров соединены . соответственно с третьими информационными входами 1-го и первого коммутаторов, группы выходов разрядов адреса (L-l)-ro и N-го регистров соединены соответственно с входами . вторых дешифраторов первого и второго блоков анализа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными | 1984 |

|

SU1278874A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

| Устройство для контроля распределения ресурсов | 1989 |

|

SU1702372A1 |

| Мультимикропрограммное устройство для контроля и управления | 1984 |

|

SU1249513A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

УСТРОЙСТВО ДЛЯ ОБМЕНА ДАННЫМИ, содержащее N регистров, м коммутаторов, генератор тактовых импульсов, группу дешифраторов, первьй и второй элементы И, группу элементов И и блоки анализа, каждый из которых содержит два дешифратора, два элемента И и два элемента ИЛИ, причем с первого по N й входы данных устройства соединены соответственно с первыми информационными входами с первого noN-й коммутаторов, выходы которых соединены с информационными входами соответственно с первого по N-Й ре- . гистров, синхровходы которых соединены с первым выходом генератора тактовых импульсов, группа разрядных выходов i -го регистра соединена с вторым информационным в.ходом (. + 1)-го коммутатора, группа выходов разрядных данных N -го регистра соединена с вторым информационным входом первого коммутатора, группы выходов разрядов данных с первого по Ю-й регистров являются с первого по N-и выходами данных устройства, группы выходов разрядов адресов первого и i. -го регистров соединены соответственно с . входами первых дешифраторов первого и второго блоков анализа, причем в каждом блоке анализа первая группа выходов первого дешифратора соединена с входами первого элемента ИЛИ,выход которого соединен с первым входом второго элемента ИЛИ, группа выходов разрядов адресов с второго по (-2)-й и с (i+1)-ro ; по (М-1)-й регистров соединены с входами соответствующих дешифрато8 S .ров группы, первый выход первого дешифратора первого блока анализа, (Л первые выходы с первого по

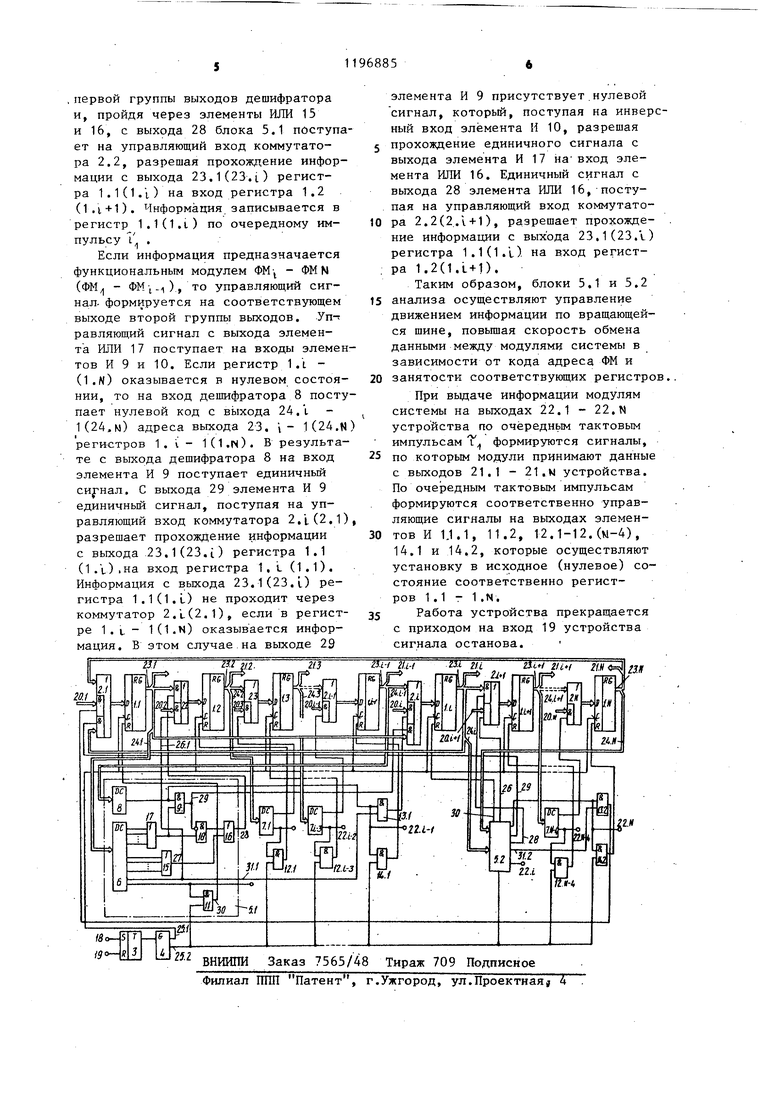

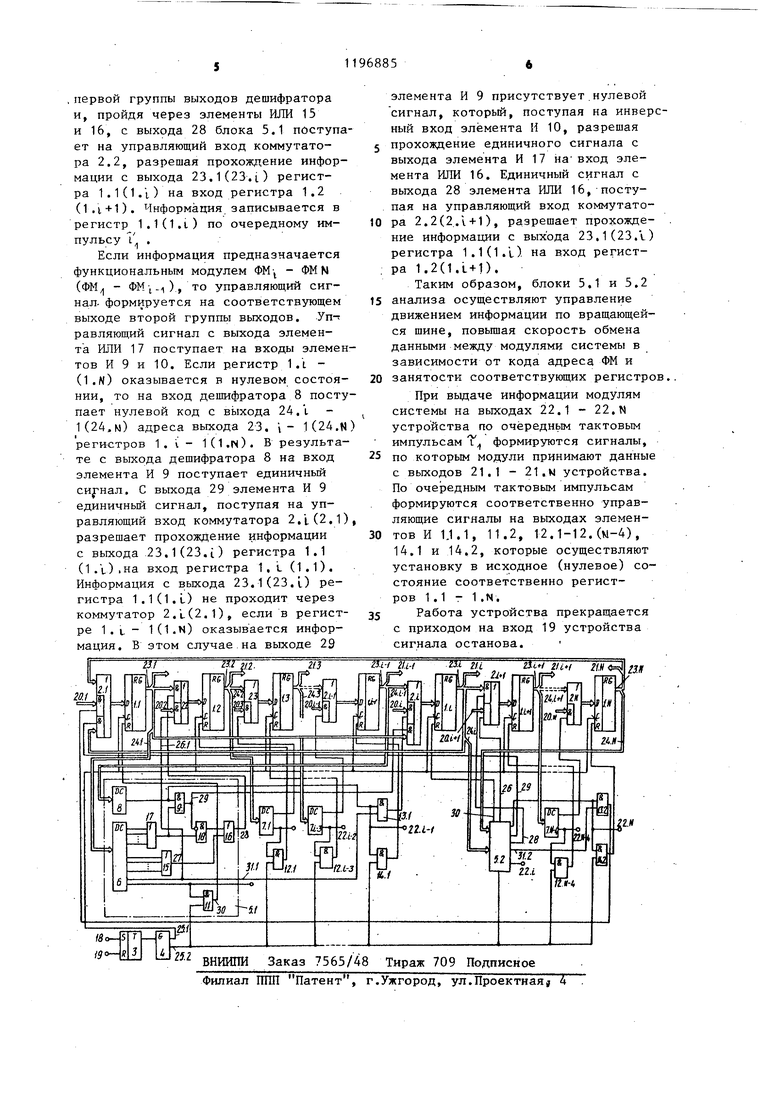

Изобретение относится к вычислительной технике и может быть использовано в качестве коммутирующей сети для управления и обмена данными в распределенньпс .системах ,с контролем.

Целью изобретения является повышение производительности устройства путем обеспечения возможности изменения направления сообщений по вращающейся шине.

На чертеже представлена функци.ональная схема устройства.

Устройство содержит первьй -И -и регистры 1.1 - 1.N соответственно, первый - N-и коммутаторы 2, триггер 3, генератор 4 тактовых импульсов, первый 5.1 и второй 5.2 блоки анализа, первый дешифратор 6, первьй - (Н-4)-й дешифраторы 7.1 7. (N-4) группы, дешифратор 8, третий элемент И 9, первьй элемент И 10 второй элемент И 11, первый (и-4)-й элемент И 12.1 -. 12. (м-4), первьй 13.1 и второй 13.2 элементы И,третий 14.1 и четвертьй 14,2 элементы И,первьй элемент ИЛИ 15 элемент ИЛИ 16, третий элемент. ИЛИ 17

. вход 18 пуска устройства, вход 19 останова устройства, первый -N -и входы 20,1 - 20. N данных устройства, первьй -N-и выходы 21.1 - 21. J данных устройства, пе;рвьй N-й выходы 22.1 - 22. N прерываний устройства, вькоды 23.1 - 23. N соответственно первого - N -го регистров 1.1 - 1. N выходы 24.1-24. N адресов выходов регистров 1.1 - 1.

3 1

/ соответственно, первый и второй выходы 25,1 и 25.2 генератора 4

тактовых импульсов соответственно; второй выход 26 первого дешифрато ра 6, выход 27 элемента ИЛИ 15, выход 28 элемента ИЛИ 16, выход 29 элемента И 9 выход 30 элемента И 11, выход 31.1 и 31,2 соответственно первого 5.1 и второго 5.2 блоков

анализа.

Устройство работает следующим образом.. .

В исходном состоянии все регистры и триггер устройства находятся в нулевом состоянии. Цепи установки в исходное состояние на функциональной схеме условно не показаны.

.Работа устройства начинается с момента прихода на вход, 18 устройства сигнала пуска. Триггер 3 устанавливается в единичное состояние, генератор 4 тактовых импульсов начинает формировать на своих выходах 25.1 и 25.2 две последовательности сдвинутых друг относительно друга тактовых импульсов i, и 1г , Данные, на входы 20.1 - .20. N. устройства от функциональных модулей могут поступать асинхронно друг относительно друга.. Рассмотрим особенности приема данных по входам 20.3. - 20, (i-1); 20.(i+2) -20. N устройства. Данные со входа 20,3 устройства, пройдя через коммутатор 2.3, записываются в регистр 1.3 по очередному тактовому импульсуY, . Разрешающим сигналом, для прохождения данных через коммутатор 2.3 является единичный сигнал, поступающий с выхода дешифратора 7.1 на вход которого поступает нулевой код адреса функционального модуля признакпустого предьщущего регистра 1.2. Аналогичным образом данные с входов 20.4 - 20.(1-1) и 20.(;+2) 20.N устройства соответственно че-.. рез коммутаторы 2..4 - 2. d-1) и 2.(v+2) - 2. N по разрешающим сигналам свыходов дешифраторов 7.2 7. (1-3) и 7. 1 - 7.(N-4) записываются в регистры 1.4 - I.(L-I) и 1.(L +2) - 1. N по тактовому импульсу 1 . По очередному тактовому импульсу данные из i -го регистра записываются в (+1)-й регистр, где V -1, N. Под (ц + 1)-м регистром подразумевается регистр 1.1.

968854

Рассмотрим особенность приема данных от функциональных модулей -по входам 20.2 и 20. (1 + 1) устройства. Данные со входов 20.2 и 20. (1+1) 5 устройства соответственно по разрешающим сигналам с выходов 26 блоков 5,1 и 5.2 анализа, пройдя соответственно через коммутаторы 2.2 и 2.(|, + 1), по очередному тактовому 10 импульсу t, записываются соответственно в регистры 1.2 и 1.(1+1). Разрешающие единичные сигналы на выходах 26 блоков 5.1 и 5.2 д.ля прохождения данных с входов20.2 15 и 20,(v+1) устройства появляются в результате поступления на входы

первого дешифратора 6 нулевых кодов адресов с выходов 24.1 и 241 адресов, выходов 23.1 и 23i соответственно регистров 1 .1 и 1. i ,

которые являются признаками- свободных регистров 1.1 и 1, (i-1). Таким образом, данные с входов 20,2 и 20, (1+1.) устройства не пересекаются

5 с информацией, передаваемой по вра- щающейся шине.

Запись данных со входа 20.1(20.1) устройства через коммутатор 2.1 (2.( ) в регистр 1,1 (1.1 ) возмож0. на при пустых регистрах Г, N(1.V-1) и 1 .i (1.1). При этом с выхода элемента И 13 на первый управляющий вход коммутатора 2.1(2,/) поступает единичный разрешающий сигнал. Этот

5 сигнал формируется при поступлении единичных сигналов с выхода 31.2(31,1).

Данные, записанные в регистры 1.1 - 1.N, по очередным тактовым

0 импульсам Т., перемещаются последовательно из (i-1)-;21 Регистра в L-Й регистр, где i 1,Ki , Такая последовательность перемещения информации из регистра в регистр может

5 быть нарушена только при записи данных в регистры 1.1 и 1.1.

При записи информации в регистр 1.1(1,1) код адреса с выхода 24.1 (24,L) поступает .на вход дешифратора 6. В зависимости от номера кода адреса на выходе первой или второй группы выходов дешифратора 6 формируется управляющий сигнал. Если информация, записанная в регистре 1.1(1.1)предназначена функциональным модулем ФМг ФМС11) ( ФМН ), то управляющий сигнал появляется на одном из выходов

| Авторское свидетельство СССР | |||

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| .Экспресс-информация, сер | |||

| ВТ, 1982, № 35, с.12, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-07—Публикация

1984-07-11—Подача