Изобретение относится к автоматике и вычислительной технике и может быть использовано в распределенных сосредоточенных управляющих системах АСУ ТП, использующих программный принцип управления, работающих по модели коллектива вычислителей. Кроме того, оно может использоваться в средствах контроля и отладки сложных управлляющих комплексов.

Известно программное устройство управления с контролем, содержащее постоянное запоминающее устройство, регистры адреса и микрокоманд, коммутатор, мультиплексор логических условий, триггер пуска, генератор тактовых импульсов, блок анализа кодов, триггер ошибки и элемент ИЛИ. Недостатком указанного аналога является низкая производительность функционирования, обусловленная невозможностью его агрегатирования в управляющую систему.

Известно наиболее близкое решение - модуль распределенной системы, содержащее блок памяти микрокоманддля программного управления, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, триггеры пуска и ошибки, генератор тактовых импульсов, элементы И, ИЛИ, дешифратор признака и кода модуля, коммутатор, магистральные элементы. Недостатком указанного аналога является низкая производительность функционирования, обусловленная последовательной работой модулей в управляющей системе.

В указанной распределенной системе для программного управления каждый модуль управляет своим объектом, параллельно с другими модулями Объекты управления системы так или иначе связаны между собой и определенным обрязом 00

К

ю

N СО

гут влиять на алгоритмы управления друг друга. При управлении сельносвязанными объектами, часто возникает необходимость анализа одним управляющим модулем системы состояния и стадии управления объектов других модулей системы.

Недостатком указанного модуля-прото- типа является низкое, быстродействие, обусло вленное низкой производительно- сть кнего работы необходимости анали- за Гм состояния оВъектов управления друТих мбдулей системы.

Такой анализ в системе на основе модуля-прототипа осуществляется путем организации специальной процедуры междумодульного взаимодействия. 1-й модуль-прототип, которому требуется узнать состояние объекта управления J-ro модуля, получает от него адресный код управления (АКУ), АКУ- это адрес М К,с которой, согласно состояния j-ro модуля, должен продолжить работу i-й модуль. Момент выполнения j-м модулем МК передачи АКУ 1-му модулю определяется программно. Однако, так как последовательность выполнения модулями МК определяется не только самой командой, но и, в известной мере, реакцией на МК объектов управления, сигналами внешних логических условий, то момент передачи АКУ может программно задаваться только на какой-то интервал времени раооты 1-го и j-ro модулей системы. Таким образом, если 1-й (j-й) модуль подошел к моменту приема (передачи) АКУ раньше j-ro (i-ro) то он должен ожидать его готовности. В этом состоянии ожидания модуль-прототип простаивает, прерывая алгоритмы управления своим объектом. Потери времени от таких простоев тем более велики, чем более недетерминированы ход реализации системой своего уп- равляющего алгоритма, чем больше задаваемый интервал времени для процедуры межмодульного взаимодействия. Весьма вероятна, также ситуация, когда Г-ому модулю нужна информация о состоянии объекта управления j-ro модуля Только при реализации им одной из альтернативных (расходящихся) ветвей своего алгоритма.

В этом случае, если i-й модуль реализует ветвь своего алгоритма, не требующую АКУ от j-ro модуля, j-й модуль в программно заданном иятервале времени ожидания передачи АКУ вообще прождет готовность i-ro модуля к приему АКУ напрасно Причем 1-й модуль, пока j-й ждет его готовности к приему от него АКУ, не может анализировать состояние объекта другого (не j-ro) модуля системы.

Таким образом, при реализации в управляющей системе сильносвязанных модульных алгоритмов, используемая в модуле-прототипе процедура организации межмодульного взаимодействия обусловливает весьма значительные потери во времени реализации модулем-прототипом алгоритма управления своим объектом.

Целью изобретения является повышение быстродействия управляющего модуля. Поставленная цель достигается тем, что

0 в модульное устройство для программного управления и контроля, содержащее блок памяти микрокоманды, регистры адреса и микроопераций, мультиплексор логических условий, коммутатор адреса, дешифратор.

5 триггер пуска, первый, второй, третий, четвертый элементы И, первый и второй элементы ИЛИ, магистральный элемент, S-вход триггера пуска является входом пуска устройства, выход устройства соединен с пер0 выми входами первого и второго элементов И, первый и второй входы синхронизации устройства являются соответственно вторыми входами первого и второго элементов И, выходы которых соединены соответственно

5 со входами синхронизации регистров микроопераций и адреса, выход поля признака микрокоманды блока памяти микрокоманд соединен со входом дешифратора, первый выход которого соединен с первым прямым

0 и вторым инверсным управляющими входами коммутатора адреса, вход кода команды устройства является первым информационным входом коммутатора адреса, старшие разряды выхода которого соединены с соот5 ветствующими разрядами информационного входа регистра адреса, второй выход дешифратора и выход поля микроопераций блока памяти микрокоманд соединены соответственно с младшими и старшими раз0 рядами информационного входа регистра микроопераций, младший разряд выхода которого соединен с R-входом триггера пуска, старшие разряды выхода регистра микроопераций являются выходом

5 микроопераций модуля, выход регистра адреса соединен со входом блока памяти микрокоманд, выход поля кода логических условий которого соединен с адресным входом мультиплексора логических условий,

0 вход логических условий устройства и выход младшего разряда поля адреса блока памяти микрокоманд соединены соответственно со старшими и младшим разрядами информационного входа мультиплексора логиче5 ских условий, выход которого и выход старших разрядов поля адреса блока памяти микрокоманд соединены соответственно с младшим и старшим разрядами второго информационного входа коммутатора адреса устройства, вход магистрального элемента соединен с двунаправленной межмодульной шиной передачи адреса, дополнительно введены коммутатор управления, регистр сдвига и схема сравнения, причем выход первого элемента И соединен с син- хровходом регистра сдвига одного из разрядов которого соединен с управляющим входом магистрального элемента, выходы разрядов соединены с соответствующим управляющим входом коммутатора управления, выход старшего разряда регистра сдвига соединен также со входом младшего разряда регистра сдвига, старшие разряды выхода полей микроопераций и кода логических условий блока памяти микрокоманд соединены соответственно с первым входом схемы сравнния, первый выход которой соединен с первым входом третье го элемента И, младшие разряды полей микроопераций и кода логических условий блока памяти микрокоманд соединены соответственно с соответствующими информационными входами коммутатора управления, выход которого соединен с управляющим входом схемы сравнения, двунаправленная шина передачи адреса является входом-выходом передачи адреса устройства и соединена со вторым информационным входом схемы сравнения, второй выход которой соединен с первым входом четвертого элемента И, третий выход дешифратора соединен с инверсным с управляющим входом мультиплексора логических условий и регистра микроопераций, со вторыми входами третьего и четвертого элементов И, выход четвертого элемента И и младший разряд выхода коммутатора адреса соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с младшим разрядом информационного входа регистра адреса, выход третьего элемента И и предпоследний младший разряд выхода коммутатора адреса соединены соответственно с первым и вторым входами второго элемента ИЛИ. выход которого соединен с предпоследним младшим разрядом информационного входа регистра адерса, выход регистра адерса, соединен с информационным входом магистрального элемента.

Сущность изобретения состоит в повышении быстродействия путем обеспечения возможности анализа модулем состояния и стадии управления объектов других модулей системы без вмешательства в их работу. Требуемую информацию о стадии управления и, соо ветс венно, о текущем состоянии объекта „ругого модуля, можно получить, идентифь.цирозав выполняемую отим модулем микрокоманду (МК). Идент;.фикатором

же МК в блоке памяти соответственного модуля является ее адрес. Возможность идентификации адерса МК в других модулях системы достигается благодаря следующе- 5 му. Между модулями системы организуется общая шина передачи адреса текущей МК с межмодульным разделением во времени. Каждый модуль системы поочередно выдает в эту шину адрес выполняемой им в этом

0 момент МКдля нужд остальных модулей системы. Те модули, которым требуется узнать стадию управления и состояние чужого объекта, выполняют специальную МК. В формате такой МК предусмотрено поле, оп5 ределяющее такт работы системы, при котором в описанной шине передачи адреса будет адрес текущей МК соответствующего модуля. Кроме того, в этой же-МК предусматривается поле, в котором записывается

0 адрес - эталон, сравниваемый с адресом из межмодульной шины. По результатам этого сравнения рассматриваемый модуль может судить о стадии управления соответствующего другого модуля системы. Для более

5 детального анализа стадии управления и соответственно состояния чужого объекта может выполняться не одна специальная МК, а их последовательность.

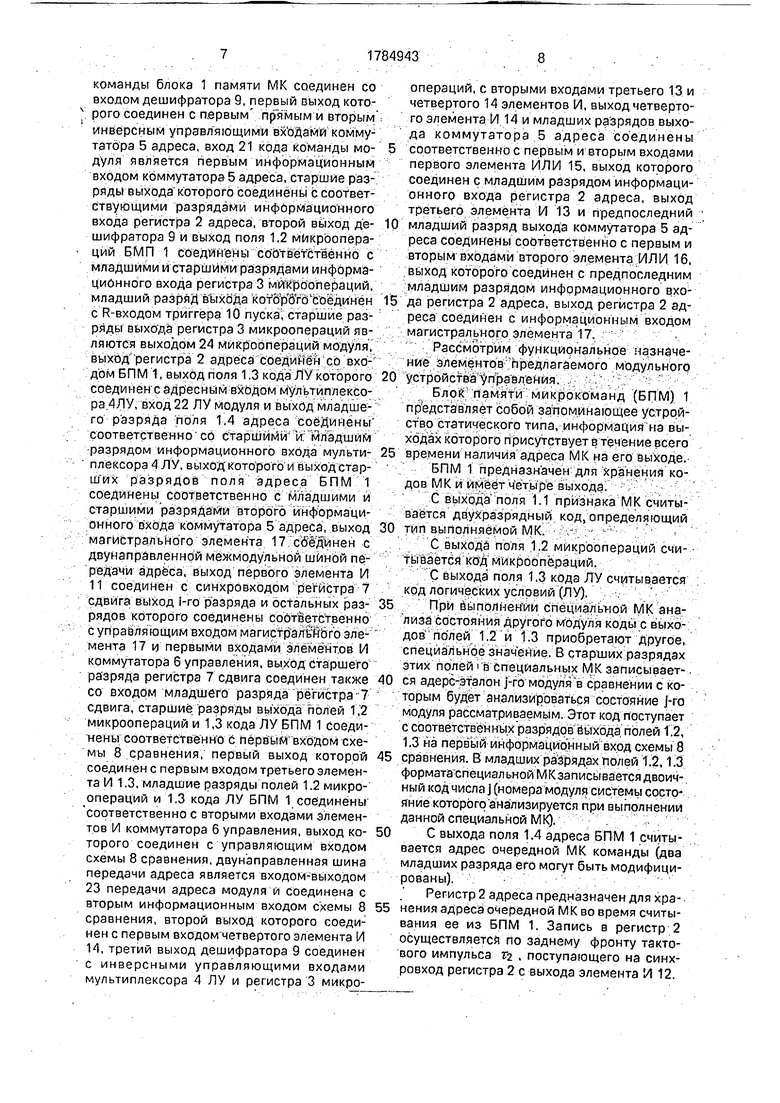

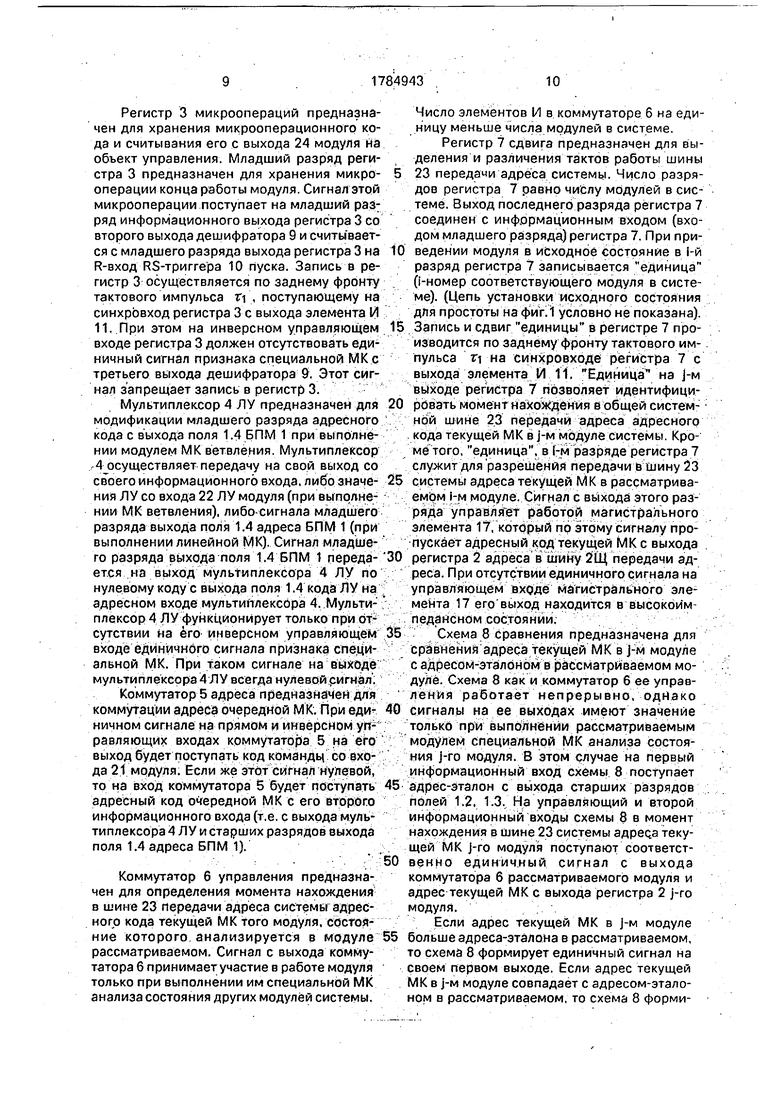

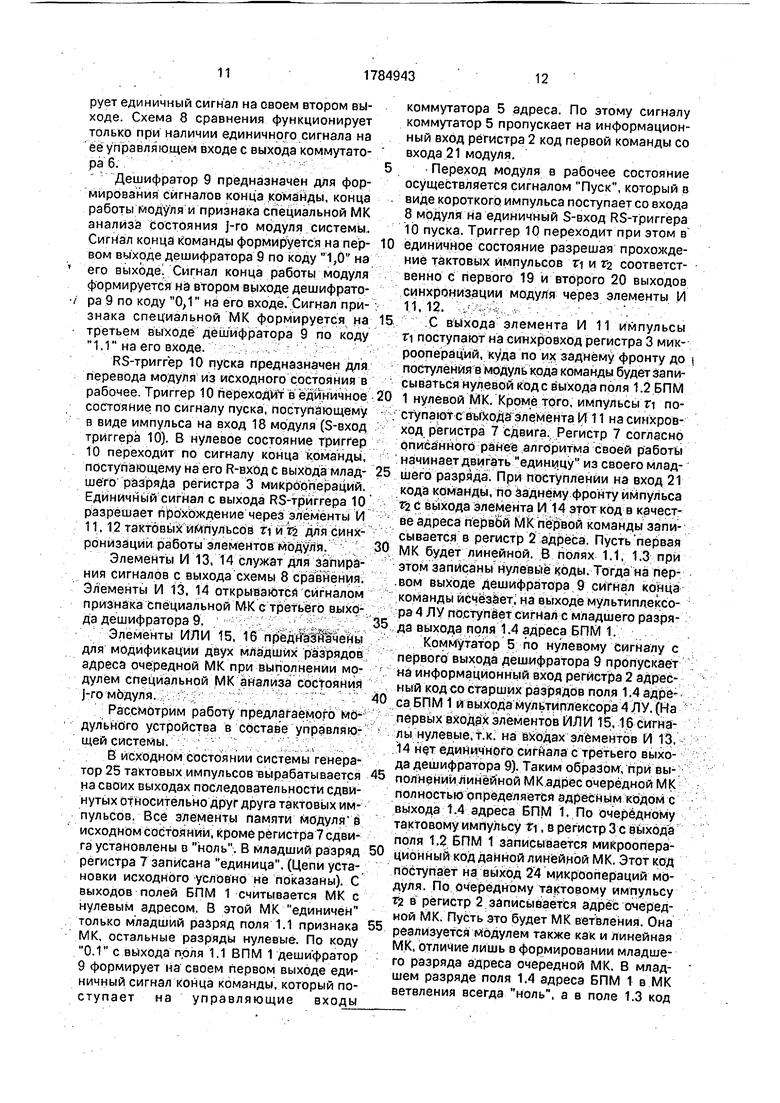

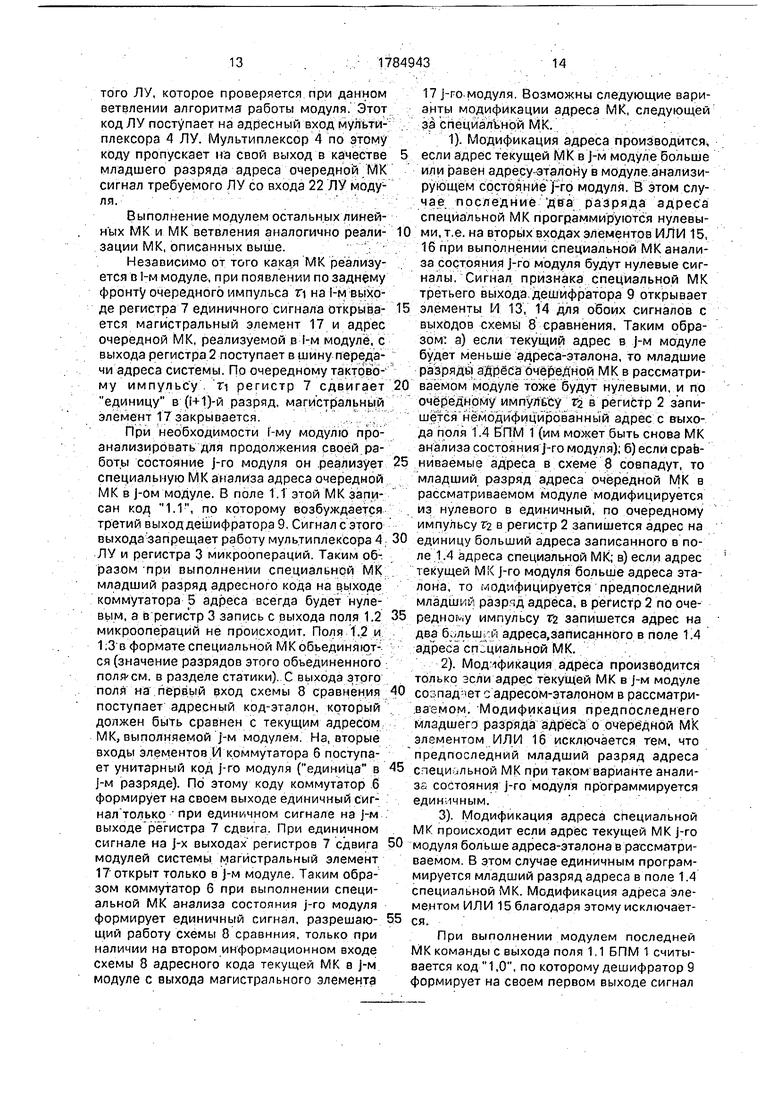

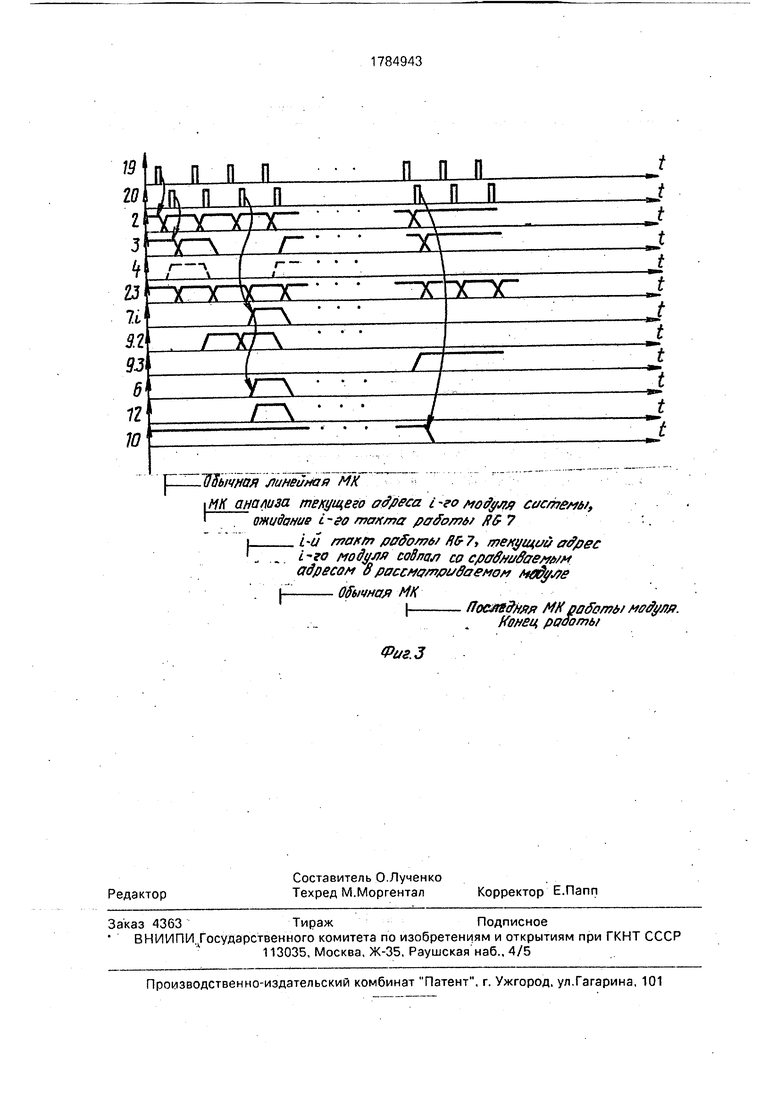

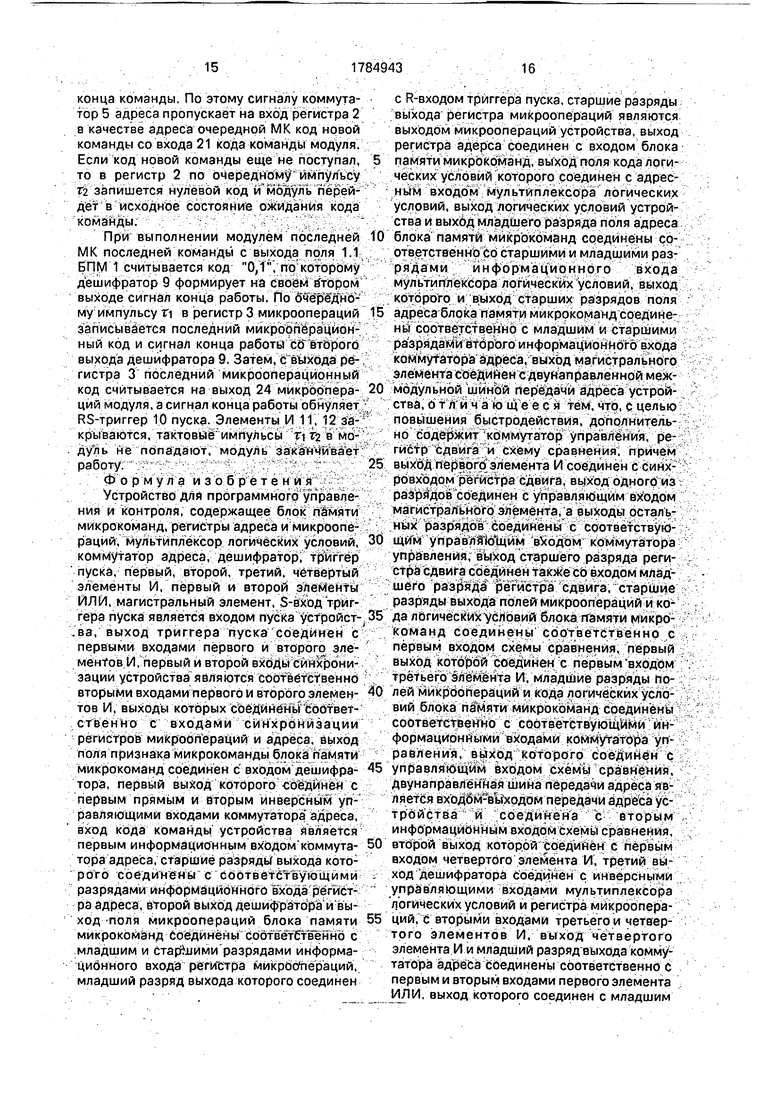

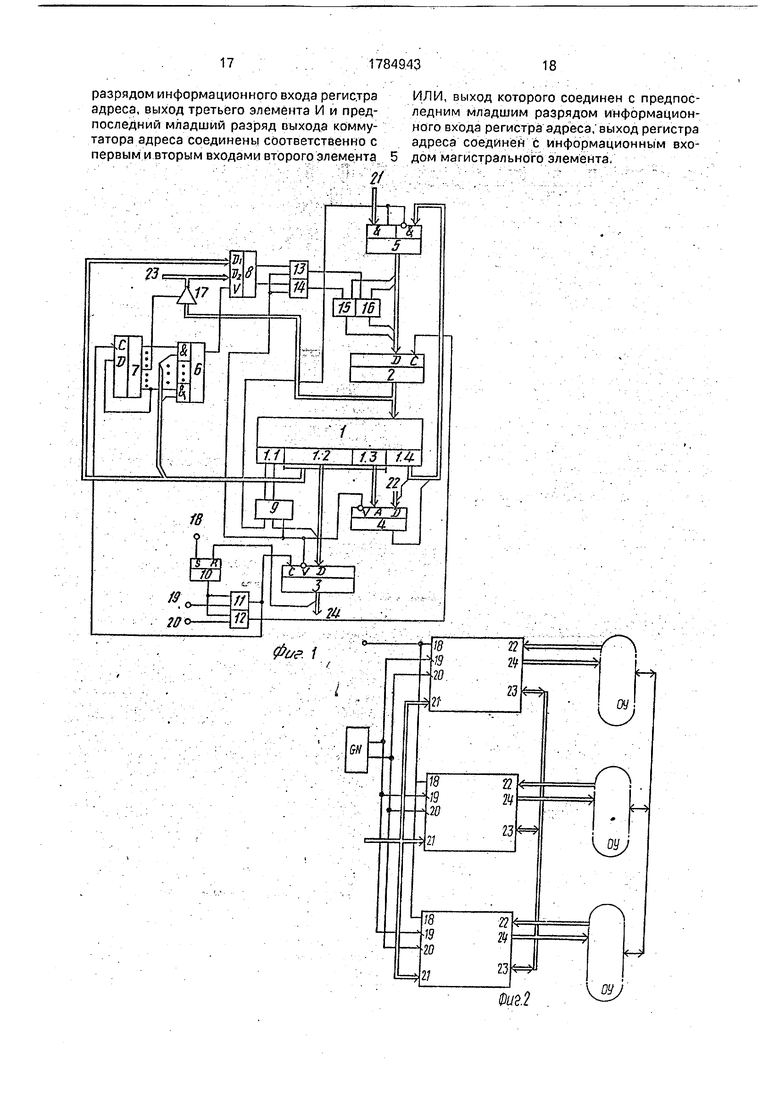

На фиг.1 приведена функциональная

0 схема варианта модульного устройстав программного управления,контроля и отладки, на фиг.2 - пример функциональной схемы управляющей системы на базе трех таких модульных устройств; на фиг.З - временная

5 диаграмма работы предлагаемого модульного устройства

Устройство (фиг.1) содержит блок памя- и микрокоманд (БПМ) 1 с полями 1.1 признака микрокоманд (МК). 1,2

0 микроопераций, 1,3 кода ЛУ, 1.4 адреса, регистры 2 адреса, 3 микроопераций, мультиплексор 4 адреса, коммутаторы 5 адреса, 6 управления, регистр 7 сдвига, схему 8 сравнения, дешифратор 9, триггер 10 пуска, пер5 вый 11, второй 12, третий 13, четвертый 14 элемен 17, вход 18 пуска модуля, первый 19, второй 20 входы синхронизации модуля, входы 21 кода команды, и 22 ЛУ модуля, вход-выход 23 шины передачи адреса, вы0 ход 24 микроопераций модуля.

Вход 18 пуска модуля является S-вхо- дом триггера 10 пуска, выход которого соединен с первыми входами первого 11 и второго 12 элеметов И, первый 19 и второй

5 20 входы синхронизации модуля являются соответственно вторыми входами первою 11 и второго 12 элементов И, выходы которых соединены соответственно со входами синхронизации регистров 3 микроопераций и 2 адреса, выход поля 1 1 признака микрокоманды блока 1 памяти МК соединен со входом дешифратора 9, первый выход кото- рого соединен с первым прямым и вторым инверсным управляющими входами коммутатора 5 адреса, вход 21 кода команды модуля является первым информационным входом коммутатора 5 адреса, старшие разряды выхода которого соединены с соответствующими разрядами информационного входа регистра 2 адреса, второй выход дешифратора 9 и выход поля 1.2 микроопераций БМП 1 соединены соответственно с младшими и старшими разрядами информационного входа регистра 3 микроопераций, младший разряд выхода котЬрЪ го соединен с R-входом триггера 10 пуска, старшие разряды выхода регистра 3 микроопераций являются выходом 24 микроопераций модуля, выход регистра 2 адреса соединен со входом БПМ 1, выход поля 1 3 кода ЛУ которого соединен с адресным входом мультиплексора 4ЛУ, вход 22 ЛУ модуля и выход младшего разряда поля 1.4 адреса соединены соответственно со старшими и йладшим разрядом информационного входа мультиплексора 4 Л У, выход которого и выход старших разрядов поля адреса БПМ 1 соединены соответственно с младшими и старшими разрядами второго информационного входа коммутатора 5 адреса, выход магистрального элемента 17 сбёдинен с двунаправленной межмодульной шиной передачи адреса, выход первого элемента И 11 соединен с синхровходом регистра 7 сдвига выход i-ro разряда и остальных разрядов которого соединены соответственно с управляющим входом магистралШого элемента 17 и первыми входами элементов И коммутатора б управления, выход старшего разряда регистра 7 сдвига соединен также со входом младшего разряда регистра 7 сдвига, старшие разряды выхода полей 1,2 микроопераций и 1,3 кода ЛУ БПМ 1 соединены соответственно с первым входом схемы 8 сравнения, первый выход которой соединен с первым входом третьего элемента И 1 3, младшие разряды полей 1 2 микроопераций и 1 3 кода ЛУ БПМ 1 соединены соответственно с вторыми входами элементов И коммутатора 6 управления, выход которого соединен с управляющим входом схемы 8 сравнения, двунаправленная шина передачи адреса является входом-выходом 23 передачи адреса модуля и соединена с вторым информационным входом схемы 8 сравнения, второй выход которого соединен с первым входом четвертого элемента И 14, третий выход дешифратора 9 соединен с инверсными управляющими входами мультиплексора 4 Л У и регистра 3 микроопераций, с вторыми входами третьего 13 и четвертого 14 элементов И, выход четвертого элемента И 14 и младших разрядов выхода коммутатора 5 адреса соединены

соответственно с первым и вторым входами первого элемента ИЛИ 15, выход которого соединен с младшим разрядом информационного входа регистра 2 адреса, выход третьего элемента И 13 и предпоследний

младший разряд выхода коммутатора 5 адреса соединены соответственно с первым и вторым входами второго элемента ИЛИ 16, выход которого соединен с предпоследним младшим разрядом информационного входа регистра 2 адреса, выход регистра 2 адреса соединен с информационным входом магистрального элемента 17.

Рассмотрим функциональное назначение элементов Предлагаемого модульного

устройства управления

Блок памяти микрокоманд (БПМ) 1 представляет собой запоминающее устройство статического типа, информация на выходах которого присутствует в течение всего

времени наличия адреса МК на его выходе. БПМ 1 предназначен для хранения кодов МК и имеет четыре выхода

С выхода поля 1 1 признака МК считывается двухразрядный код, определяющий

тип выполняемой МК.

С выхода поля 1 2 микроопераций считывается код микроопераций.

С выхода поля 1 3 кода ЛУ считывается код логических условий (ЛУ)

При выполнении специальной МК анализа состояния другого мгодуля коды с выходов полей 1 2 и 1 3 приобретают другое, специальное значение. В старших разрядах этих полей i в специальных МК записывается адерс-эталон j-ro модуля в сравнении с которым будет анализироваться состояние j-ro модуля рассматриваемым Этот код поступает с соответственных разрядов ёыхода полей 1.2, 1.3 на первый информационный вход схемы 8

сравнения. В младших разрядах полей 1.2,1.3 формата специальной МКзаписывается двоичный код числа j (номера модуля системы состояние которого анализируется при выполнении данной специальной МК).

С выхода поля 1.4 адреса БПМ 1 считывается адрес очередной МК команды (два младших разряда его могут быть модифицированы)

Регистр 2 адреса предназначен для хранения адреса очередной М К во время считывания ее из БПМ 1 Запись в регистр 2 осуществляется по заднему фронту тактового импульса Г2 , поступающего на синх- ровход регистра 2 с выхода элемента И 12

Регистр 3 микроопераций предназначен для хранения микрооперационного кода и считывания его с выхода 24 модуля на объект управления. Младший разряд регистра 3 предназначен для хранения микрооперации конца работы модуля. Сигнал этой микрооперации поступает на младший разряд информационного выхода регистра 3 со второго выхода дешифратора 9 и считывается с младшего разряда выхода регистра 3 на R-вход RS-триггера 10 пуска. Запись в регистр 3 осуществляется по заднему фронту тактового импульса с , поступающему на синхровход регистра 3 с выхода элемента И 11. При этом на инверсном управляющем входе регистра 3 должен отсутствовать единичный сигнал признака специальной МК с третьего выхода дешифратора 9. Этот сигнал запрещает запись в регистр 3.

Мультиплексор 4 ЛУ предназначен для модификации младшего разряда адресного кода с выхода поля 1.4 БПМ 1 при выполнении модулем МК ветвления. Мультиплексор 4 осуществляет передачу на свой выход со своего информационного входа, либо значения ЛУ со входа 22 ЛУ модуля (при выполнении МК ветвления), либо сигнала младшего разряда выхода поля 1.4 адреса БПМ 1 (при выполнении линейной МК). Сигнал младшего разряда выхода поля 1.4 БПМ 1 передается на выход мультиплексора 4 ЛУ по нулевому коду с выхода поля 1.4 кода ЛУ на адресном входе мультиплексора 4. Мультиплексор 4 ЛУ функционирует только при отсутствии на его инверсном управляющем входе единичного сигнала признака специальной МК. При таком сигнале на выходе мультиплексора 4 Л У всегда нулевой ригнал .

Коммутатор 5 адреса предназначен для коммутации адреса очередной МК. При единичном сигнале на прямом и инверсном управляющих входах коммутатора 5 на его выход будет поступать код команды, со входа 21 модуля. Если же этот сигнал нулевой, то на вход коммутатора 5 будет поступать адресный код очередной МК с его второго информационного входа (т.е. с выхода мультиплексора 4 ЛУ и старших разрядов выхода поля 1.4 адреса БПМ 1).

Коммутатор 6 управления предназначен для определения момента нахождения в шине 23 передачи адреса системы адресного кода текущей МК того модуля, состояние которого анализируется в модуле рассматриваемом. Сигнал с выхода коммутатора 6 принимает участие в работе модуля только при выполнении им специальной МК анализа состояния других модулей системы.

Число элементов И в коммутаторе 6 на единицу меньше числа модулей в системе.

Регистр 7 сдвига предназначен для выделения и различения тактов работы шины 5 23 передами адреса системы. Число разрядов регистра 7 равно числу модулей в системе. Выход последнего разряда регистра 7 соединен с информационным входом (входом младшего разряда) регистра 7. При при- 10 ведении модуля в исходное состояние в 1-й разряд регистра 7 записывается единица (i-номер соответствующего модуля в системе). (Цепь установки исходного состояния для простоты на фиг.1 условно не показана). 15 Запись и сдвиг единицы в регистре 7 производится по заднему фронту тактового импульса т на синхровходе регистра 7 с выхода элемента И 11. Единица на j-м выходе регистра 7 позволяет идентифици0 рбвзть момент нахождения в общей системной шине 23 передачи адреса адресного кода текущей МК в j-м модуле системы Кроме того, единица, в i-м разряде регистра 7 служит для разрешения передачи в шину 23

5 системы адреса текущей МК в рассматриваемом i-м модуле. Сигнал с выхода этого разряда управляет работой магистрального элемента 17, который по этому сигналу пропускает адресный код текущей МК с выхода

0 регистра 2 адреса в шину 2Щ передачи адреса. При отсутствии единичного сигнала на управляющем входе магистрального элемента 17 его выход находится в высокоим- педансном состоянии.

5 Схема 8 сравнения предназначена для сравнения адреса текущей МК в j-м модуле с адресом-эталоном в рассматриваемом модуле. Схема 8 как и коммутатор б ее управления работает непрерывно, однако

0 сигналы на ее выходах имеют значение только при выполнении рассматриваемым модулем специальной МК анализа состояния j-ro модуля. В этом случае на первый информационный вход схемы 8 поступает

5 адрес-эталон с выхода старших разрядов полей 1.2, 1.3. На управляющий и второй информационный входы схемы 8 в момент нахождения в шине 23 системы адресу текущей МК j-ro модуля поступают соответст0 венно единичный сигнал с выхода коммутатора 6 рассматриваемого модуля и адрес текущей МК с выхода регистра 2 j-ro модуля.

Если адрес текущей МК в j-м модуле

5 больше адреса-эталона в рассматриваемом, то схема 8 формирует единичный сигнал на своем первом выходе. Если адрес текущей МК в j-м модуле совпадает с адресом-эталоном в рассматриваемом, то схема 8 формирует единичный сигнал на своем втором выходе. Схема 8 сравнения функционирует только при наличии единичного сигнала на ее управляющем входе с выхода коммутатора 6.

Дешифратор 9 предназначен для формирования сигналов конца команды, конца работы модуля и признака специальной МК анализа состояния j-ro модуля системы. Сигнал конца команды формируется на первом выходе дешифратора 9 по коду 1,0 на его выходе. Сигнал конца работы модуля формируется на втором выходе дешифрато- / ра 9 по коду 0,1 на его входе. Сигнал признака специальной МК формируется на третьем выходе дешифратора 9 по коду 1.1 на его входе.

RS-триггер 10 пуска предназначен для перевода модуля из исходного состояния в рабочее. Триггер 10 переходит в единичное состояние по сигналу пуска, поступающему в виде импульса на вход 18 модуля (S-вход триггера 10). В нулевое состояние триггер 10 переходит по сигналу конца команды, поступающему на его R-вход с выхода младшего разряда регистра 3 микроопераций. Единичный сигнал с выхода RS-триггера 10 разрешает прохождение через элементы И 11,12 тактовых импульсов п и Г2 для синхронизации работы элементов модуля.

Элементы И 13, 14 служат для запирания сигналов с выхода схемы 8 сравнения. Элементы И 13, 14 открываются сигналом признака специальной МК с третьего выхода дешифратора 9.

Элементы ИЛИ 15, 16 предн аШэчены для модификации двух младших разрядов адреса очередной МК при выполнении модулем специальной МК анализа состояния j-ro мбдуля.

Рассмотрим работу предлагаемого модульного устройства в составе управляющей системы.

В исходном состоянии системы генератор 25 тактовых импульсов вырабатывается на своих выходах последовательности сдвинутых относительно друг друга тактовых им- пульсов. Все элементы памяти модуля s исходном состоянии, кроме регистра 7 сдвига установлены в ноль. В младший разряд регистра 7 записана единица. (Цепи установки исходного условно не показаны). С выходов полей БПМ 1 считывается МК с нулевым адресом. В этой МК единичен только младший разряд поля 1.1 признака МК, остальные разряды нулевые. По коду 0.1 с выхода поля 1.1 ВПМ 1 дешифратор 9 формирует на своем первом выходе единичный сигнал конца команды, который поступает на управляющие входы

коммутатора 5 адреса. По этому сигналу коммутатор 5 пропускает на информационный вход регистра 2 код первой команды со входа 21 модуля.

Переход модуля в рабочее состояние

осуществляется сигналом Пуск, который в виде короткого импульса поступает со входа 8 модуля на единичный S-вход RS-триггера 10 пуска. Триггер 10 переходит при этом в

0 единичное состояние разрешая прохождение тактовых импульсов rt и гз соответственно с первого 19 и второго 20 выходов синхронизации модуля через элементы И 11,12. .

5 С выхода элемента И 11 импульсы ri поступают на синхровход регистра 3 микроопераций, куда по их заднему фронту до постуления в модуль кода команды будет записываться нулевой коде выхода поля 1.2 БПМ

0 1 нулевой МК. Кроме того, импульсы п посту па юте в элемента И 11 на синхровход регистра 7 сдвига. Регистр 7 согласно описанного ранее алгоритма своей работы начинает двигать единицу из своего млад5 шего разряда. При поступлении на вход 21 кода команды, по заднему фронту импульса TZ с выхода элемента И 14 этот код в качестве адреса первбй МК первой команды записывается в регистр 2 адреса. Пусть первая

0 МК будет линейной, в полях 1.1, 1.3 при этом записаны нулевые коды. Тогда на первом выходе дешифратора 9 сигнал конца команды исчезает, на выходе мультиплексора 4 ЛУ поступает сигнал с младшего разря5 да выхода поля 1.4 адреса БПМ 1.

Коммутатор 5 по нулевому сигналу с первого выхода дешифратора 9 пропускает на информационный вход регистра 2 адресный код со старших разрядов поля 1.4 адре0 са БПМ 1 и выхода мультиплексора 4 ЛУ. (На первых входах элементов ИЛИ 15,16 сигналы нулевые, т.к. на входах элементов И 13, 14 нет единичного сигнала с третьего выхода дешифратора 9). Таким образом, при вы5 полнениилинейнойМКадрес очередной МК полностью определяется адресным кодом с выхода 1.4 адреса БПМ 1. По очередному тактовому импульсу ri, в регистр 3 с выхода поля 1.2 ВПМ 1 записывается микроопера0 ционный код данной линейной МК. Этот код поступает на выход 24 микроопераций модуля. По очередному тактовому импульсу Г2 в регистр 2 записывается адрес очередной МК. Пусть это будет МК ветвления. Она реализуется модулем также как и линейная МК, отличие лишь в формировании младшего разряда адреса очередной МК. В младшем разряде поля 1.4 адреса БПМ 1 в МК ветвления всегда ноль, а в поле 1.3 код

5

того ЛУ, которое проверяется при данном ветвлении алгоритма работы модуля Этот код ЛУ поступает на адресный вход мультиплексора 4 ЛУ. Мультиплексор 4 по этому коду пропускает на свой выход в качестве младшего разряда адреса очередной МК сигнал требуемого ЛУ со входа 22 ЛУ модуля.

Выполнение модулем остальных линейных МК и МК ветвления аналогично реализации МК, описанных выше

Независимо от того какал МК реализуется в 1-м модуле, при появлении по заднему фронту очередного импульса ri на l-м выходе регистра 7 единичного сигнала открывается магистральный элемент 17 и адрес очередной МК, реализуемой в i-м модуле, с выхода регистра 2 поступает в шину передачи адреса системы По очередному тактовому импульсу ti регистр 7 сдвигает единицу в (1+1)-й разряд, магистральный элемент 17 закрывается

При необходимости l-му модулю проанализировать для продолжения своей работы состояние j-ro модуля он реализует специальную МК анализа адреса очередной МК в j-Ом модуле. В поле 1 1 этой МК записан код 1.1, по которому возбуждается третий выход дешифратора 9 Сигнал с этого выхода запрещает работу мультиплексора 4 ЛУ и регистра 3 микроопераций Таким образом при выполнении специальной МК младший разряд адресного кода на выходе коммутатора 5 адреса всегда будет нулевым, а в регистр 3 запись с выхода поля 1.2 микроопераций не происходит. Поля 1.2 и 1 3 в формате специальной МК объединяются (значение разрядов этого объединенного поля см. в разделе статики) С выхода этого поля на первый вход схемы 8 сравнения поступает адресный код-эталон, который должен быть сравнен с текущим адресом МК, выполняемой j-м модулем На, вторые входы элементов И коммутатора б поступает унитарный код j-ro модуля (единица в j-м разряде). По этому коду коммутатор 6 формирует на своем выходе единичный сигнал только при единичном сигнале на j-м выходе регистра 7 сдвига При единичном сигнале на j-x выходах регистров 7 сдвига модулей системы магистральный элемент 17 открыт только в j-м модуле Таким образом коммутатор 6 при выполнении специальной МК анализа состояния j-ro модуля формирует единичный сигнал, разрешающий работу схемы 8 сравнния, только при наличии на втором информационном входе схемы 8 адресного кода текущей МК в j-м модуле с выхода магистрального элемента

17 j-ro модуля Возможны следующие варианты модификации адреса МК, следующей за специальной МК.

1). Модификация адреса производится, 5 если адрес текущей МК в j-м модуле больше или равен адресу-эталону в модуле анализирующем состояние j-ro модуля. В этом случае последние два разряда адреса специальной МК программируются нулевы10 ми, т е. на вторых входах элементов ИЛИ 15, 16 при выполнении специальной МК анализа состояния j-ro модуля будут нулевые сигналы Сигнал признака специальной МК третьего выхода дешифратора 9 открывает

15 элементы И 13, 14 для обоих сигналов с выходов схемы 8 сравнения. Таким образом: а) если текущий адрес в j-м модуле будет меньше адреса-эталона, то младшие разряды адреса Очередной МК в рассматри0 ваемом модуле тоже будут нулевыми, и по очередному импульсу TI в регистр 2 запишется немодифицированный адрес с выхода поля 1 4 БПМ 1 (им может быть снова МК анализа состояния j-ro модуля), б)еслисрав5 ниваемые адреса в схеме 8 совпадут, то младший разряд адреса очередной МК в рассматриваемом модуле модифицируется из нулевого в единичный, по очередному импульсу Сг в регистр 2 запишется адрес на

0 единицу больший адреса записанного в поле 1.4 адреса специальной МК, в) если адрес текущей МК j-ro модуля больше адреса эталона, то модифицируется предпоследний младший разрад адреса, в регистр 2 по оче5 редно у импульсу fi запишется адрес на два и адреса.записанного в поле 1 4 адреса специальной МК.

2). Мод1фикация адреса производится только эсли адрес текущей МК в j-м модуле

0 со. пад ет с адресом-эталоном в рассматриваемом. Модификация предпоследнего младшего разряда адреса о очередной МК элементом ИЛИ 16 исключается тем. что предпоследний младший разряд адреса

5 специ льной МК при таком варианте анализа состояния j-ro модуля программируется един 1чным.

3) Модификация адреса специальной МК происходит если адрес текущей МК j-ro

0 модуля больше адреса-эталона в рассматриваемом В этом случае единичным программируется младший разряд адреса в поле 1 4 специальной МК Модификация адреса элементом ИЛИ 15 благодаря этому исключает5 ся.

При выполнении модулем последней МК команды с выхода поля 1 1 БПМ 1 считывается код 1,0, по которому дешифратор 9 формирует на своем первом выходе сигнал

конца команды. По этому сигналу коммутатор 5 адреса пропускает на вход регистра 2 в качестве адреса очередной МК код новой команды со входа 21 кода команды модуля. Если код новой команды еще не поступал, то в регистр 2 по очередному импульсу Т2 запишется нулевой код и4 модуль перейдет в исходное состояние ожидания кода команды.

При выполнении модулем последней МК последней команды с выхода поля 1.1 БПМ 1 считывается код 0,1, по которому дешифратор 9 формирует на своём в тором выходе сигнал конца работы. По му импульсу ti в регистр 3 микроопераций записывается последний микрооперационный код и сигнал конца работы со второго выхода дешифратора 9. Затем, с выхода регистра 3 последний микрооперационный код считывается на выход 24 микроопера- ций модуля, а сигнал конца работы обнуляет RS-триггер 10 пуска. Элементы И 11, 12 закрываются, тактовые импульсы r TI в модуль не попадают, модуль заканчивает работу.

Формула изобретения Устройство для программного управления и контроля, содержащее блок памяти микрокоманд, регистры адреса и микроопераций, мультиплексор логических условий, коммутатор адреса, дешифратор, триггер пуска, первый, второй, третий, четвертый элементы И, первый и второй элементы ИЛИ, магистральный элемент, S-вход триггера пуска является входом пуска устройст.ва, выход триггера пуска соединен с первыми входами первого и второго элементов И, первый и второй входы синхронизации устройства являются coofeeTcfвенно вторыми входами первого и второго элемен- тов И, выходы которых соединены Соответственно с входами синхронизации регистров микроопераций и адреса, выход поля признака микрокоманды блока памяти микрокоманд соединен с входом дешифра- тора, первый выход которого соединен с первым прямым и вторым инверсным управляющими входами коммутатора адреса, вход кода команды устройства является первым информационным входом коммута- тора адреса, старшие разряды выхода которого соединены с соответствующими разрядами информационного входа регистра адреса, второй выход дешифратора и выход поля микроопераций блока памяти микрокоманд Соединены соответственно с младшим и старшими разрядами информационного входа регистра мйкрбО пе раций, младший разряд выхода которого соединен

с R-входом триггера пуска, старшие разряды выхода регистра микроопераций являются выходом микроопераций устройства, выход регистра адерса соединен с входом блока памяти микрокоманд, выход поля кода логических условий которого соединен с адресным входом мультиплексора логических условий, выход логических условий устройства и выход младшего разряда поля адреса блока памяти микрокоманд соединены соответственно со старшими и младшими раз- рядами информационного входа мультиплексора логических условий, выход которого и выход старших разрядов поля адреса блока памяти микрокоманд соединены соответственно с младшим и старшими разрядами второго информационного входа коммутатора адреса, выход магистрального элемента соединен с двунаправленной межмодульной шйнЪй передачи адреса устройства, отличающееся тем, что, с целью повышения быстродействия, дополнительно содержит коммутатор управления, регистр сдвига и схему сравнения, причем выход первого элемента И соединен с синх- ровходом регистра сдвига, выход одного из разрядов Соединен с управляющим входом магистрального элемента, а выходы остальных разрядов соединены с соответствующим управляющим входом коммутатора управления, выход старшего разряда регистра сдвига соединен также со входом младшего разряди регистра сдвига, старшие разряды выхода полей микроопераций и кода логических условий блока памяти микро- команд соединены соответственно с первым входом схемы сравнения, первый выход которой соединен с первым входом третьего элемента И, младшие разряды Молей микроопераций и кода логических условий блока па мяти микрокоманд соединены соответственно с соответствующими информационными входами коммутатора управления, выход которого соединен с управляющим входом схемы сравнения, двунаправленная шина передачи адреса является входбм вы ходом передачи адреса устройства и соединена с вторым информационным входом схемы сравнения, второй выход которой Соединен с первым входом четвертого элемента И, третий выход дешифратора соединен с инверсными управляющими входами мультиплексора логических условий и регистра микроопераций, с вторыми входами третьего и четвертого элементов И, выход четвертого элемента И и младший разряд выхода коммутатора адреса соединены соответственно С первым и вторым входами первого элемента ИЛИ, выход которого соединен с младшим

разрядом информационного входа регистраИЛИ, выход которого соединен с предпосадреса, выход третьего элемента И и пред-ледним младшим разрядом информационпоследний младший разряд выхода комму-ного входа регистра адреса, выход регистра

татора адреса соединены соответственно садреса соединен с информационным вхопервым и вторым входами второго элемента5 дом магистрального элемента,

| название | год | авторы | номер документа |

|---|---|---|---|

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

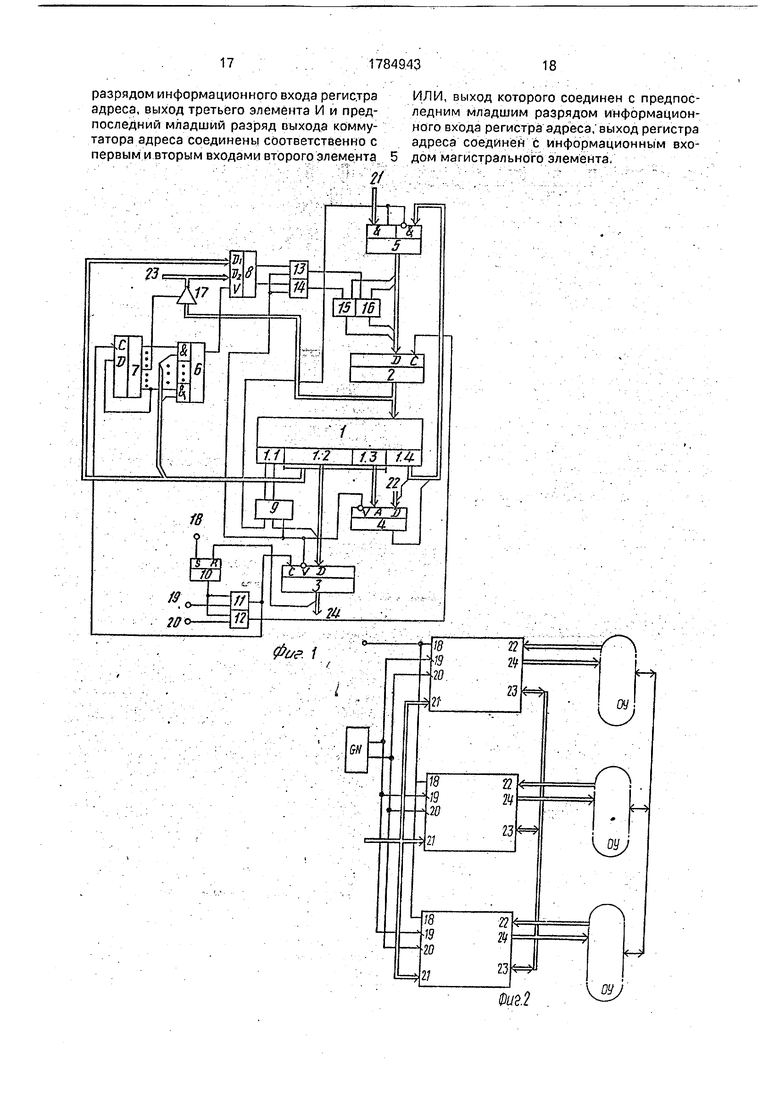

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в распределенных сосредоточенных управляющих системах АСУ ТП, использующих программный принцип управления, работающих по модели коллектива вычислителей. Кроме того, оно может использоваться в средствах контроля и отладки сложных управляющих комплексов. Цель изобретения-повышение быстродействия управляющего модуля. Поставленная цель достигается тем, что в устройство для программного управления и контроля дополнительно введены коммутатор управления, регистр сдвига и схема сравнения, а также соответствующие связи между ними. Использование данного устройства позволяет повысить быстродействие в 1,8-7,6 раза. 3 ил. (Л С

Фиг 1

S

Г

I ч

ИНычная линейная МК

МК анализа текущего crfyeca i-eoMofyw системы, ожидание L-&O mer/fma ру&о/пб; fl&7

L-й тахт pffffow Д5-7, текущий afoec . 1-го модуля соВлал со cpfffat/fae/w

ааресом 0 рассмег/приваемом wfyrfe -Обычная МК

ffocaSffaffft МК оа&ты Mfffyj)#.

Конец раооты

Фиг.З

п и п

IX П П

гх:

J

t

t

t

t

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-12-30—Публикация

1991-02-15—Подача