оно дополнительно содержит блок приоритета логических условий, блок пуска-останова, триггер адресации, со второго по (К+1)-ый коммутаторы, где (Х+1) - число модифицируемых разрядов адреса следующей микрокоманды, группу блоков элементов И, дешифратор типа микрокоманд, дешифратор несовместимых микроопераций, элемент ИЛИ и второй блок элементов И, причем группа выходов второго блока элементов И соединена с группой адресных выходов усП ойства и со второй группой и форма{щонных входов коммутатора адреса, третья группа информационных входов которого является группой адресных входов устройства, первые входа1 второго блока элементов И соединены со входом признака адресации к внешней памяти устройства, вход признака начала работы устройства соединен с первым входом блока пуска-останова, выход которого соединен со входом запуска генератора тактовых импульсов, группа выходов кода пша микрокоманды регистра микрокоманд соединена с группой входов дешифратора типа я кpoкоманд, -и выход которого, где 1( 1,2,...,т, (П) - количество групп сов.местимых микроопераций первого типа) соединен с первыми входами -го блока элементов И группы, вторые входы которого соединены со входами дешифратора несовместимых микроопераций и с выходами кода микроопераций регистра микрокоманд второй группы, группа выходов блоков элементов И группы является второй группой управляющих выходов устройства, группа выходов дешифратора несовместимых микроопераций является третьей группой управляющих выходов устройства, стробирующий вход дешифратора несовместимых микрооперащШ соединен с (fn+1) -м выходом дешифратора типа микрокоманд, второй выходгенератора

..тактовых ИМПУЛЬСОВ coejaHHeH с первьй входом элемента ИЛИ и со вторым

.входом блока пуска-останова, третий вход которого соединен с выходом признака конца работы регистра микрокоманд, третий и четвертый выходы генератора тактовых импульсов соединены соответственно со входами установки в 1 и установки в О триггера адресации, выход которого соединен с П -м адресным входом блок памяти микрокоманд, вход синхронизации регистра адреса микрокоманд соединен с выходом элемента ИЛИ, второй вход которого является входом управления записью адреса от внешних объектов устройства, входы приоритетных логических условий группы входов логических условий устройства соединены со входами блока приоритета логических условий, первый выход блока приоритета логических условий соединен с о -м информационным входом мультиплексора логических условий, р -и выход блока приоритета

логических условий,где р 2,3

(К+ 1), соединен с первым информационнь1М входом р -го коммутатора группы, выход 5-го коммутатора, где 5 1,2,i. {К+1)соединен cfl -ым информационным входом первой группы коммутатора адреса.( (L-H),(L+2),...,(L+l;+1) и с S-M входом первой группы второго блока элементов И, Lвходов второй групп которого соединены с t выходами немодифицируемых разрядов адреса блока памяти микрокоманд, второй информационный вход 5-го коммутатора соединен с 5-м выходом модифицируемых разрядов адреса блока памяти микрокоманд, управляющий вход р-го коммутатора соединен с выходом признака анализа приоритетных логических условий регистра микрокоманд, выход признака анализа неприоритетных логических условий которого соединен с управляющим входом первого коммутатора.

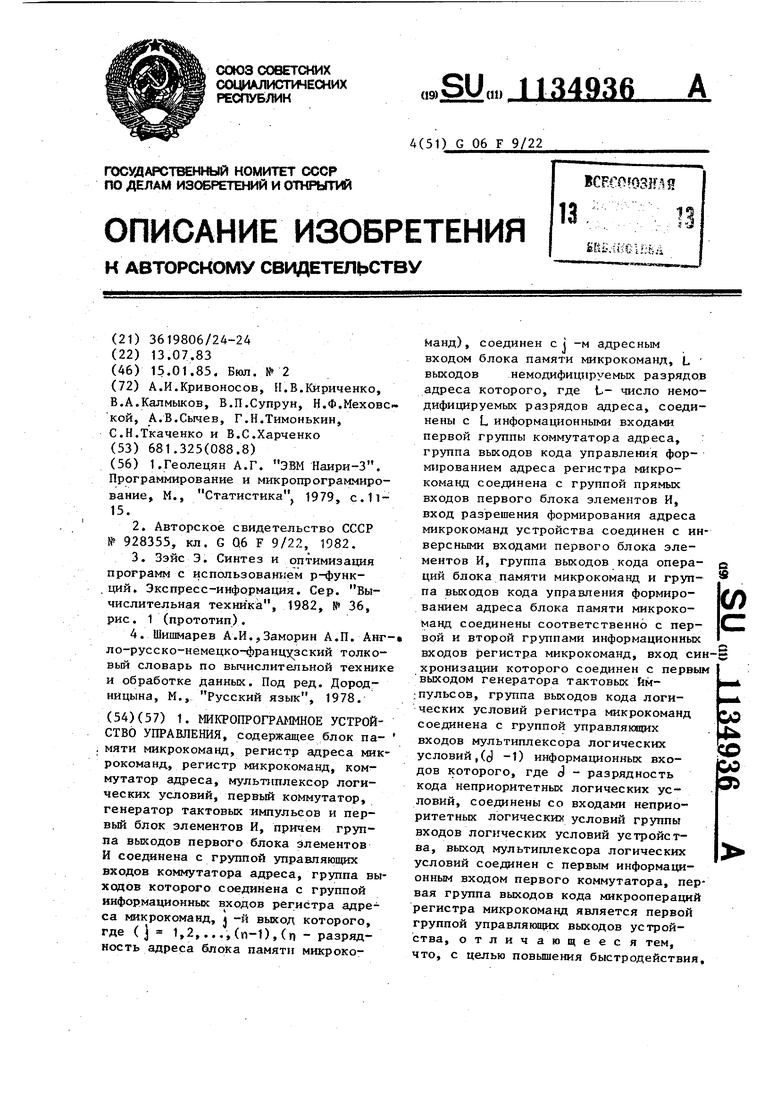

2.Устройство по п. 1, отличающееся тем, что блок приоритета логических условий содержит, k-элементов И, причем прямые входы k-элементов И являются k-входами.блока, инверсный вход первого элемента

И является (К+О-м входом блока и nepBbiM выходом блока и соединен с W-M инверсным входом -го элемента И, где / 2,3,...,k,N М , выход t-ro элементам где i 1,2,...,(4-1) является (t + 1)-M выходом блока и соединен с (N-1)-M инверсным входом V-г элемента И, выходы V-го элемента И являются (k + l)-м выходом блока.

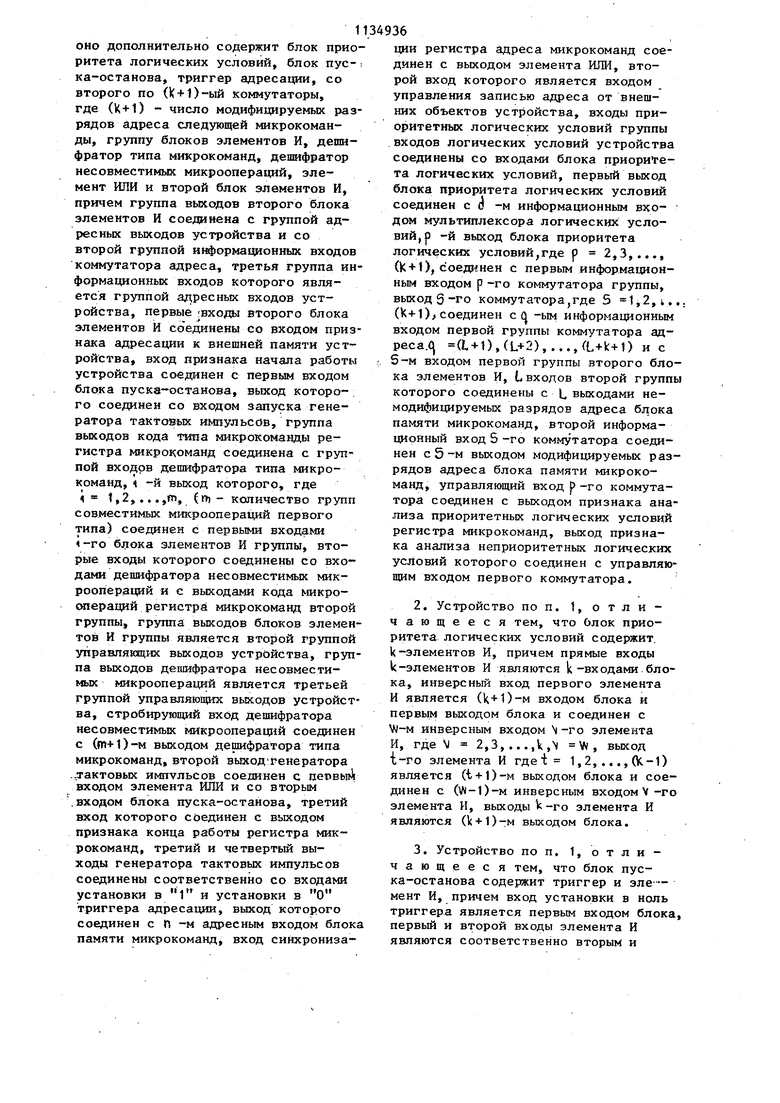

3.Устройство по п. 1, отличающееся тем, что блок пуска-останова содержит триггер и эле - мент И, причем вход установки в ноль триггера является первым входом блок первый и второй входы элемента И являются соответственно вторым и

третьим входами блока, выход элемен- 1 триггера, выход которого является та И соединен со входом установки в выходом блока. .

1134936

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр адреса микрокоманд, регистр микрокоманд, коммутатор адреса, мультиплексор логических условий, первый коммутатор, генератор тактовых импульсов и первьй блок элементов И, причем группа выходов первого блока элементов И соединена с группой управляющих входов коммутатора адреса, группа выxctqoB которого соединена с группой информационных входов регистра адреса микрокоманд, j -и выход которого, где (« 1,2,..., (п-1),(п - разрядность адреса блока памяти микрокоманд), соединен сj -м адресным входом блока памяти микрокоманд, L выходов немодифицируемых разрядов адреса которого, где t- число немодифицируемых разрядов адреса, соединены с L информационными входами первой группы коммутатора адреса, группа выходов кода управления формированием адреса регистра микрокоманд соединена с группой прямых входов первого блока элементов И, вход разрешения формирования адреса микрокоманд устройства соединен с инверсными входами первого блока элементов И, группа выходов кода операций блока памяти микрокоманд и груп(/) па выходов кода управления формированием адреса блока памяти микрокоманд соединены соответственно с первой и второй группами информационных входов регистра микрокоманд, вход син -С хронизации которого соединен с первым выходом генератора тактовых йм;пульсон, группа выходов кода логических условий регистра микрокоманд DO соединена с группой управляющих 1 входов мультиплексора логических :О условий,(cJ -1) информационных вхосо дов которого, где d - разрядность кода неприоритетных логических условий, соединены со входами неприоритетных логических условий группы входов логических условий устройства, выход мультиплексора логических условий соединен с первым информационным входом первого коммутатора, первая группа выходов кода микроопераций регистра микрокоманд является первой группой управляющих выходов устройства, отличающееся тем, что, с целью повышения быстродействия.

Изобретение относится к вычислительной технике и может быть использовано для построения устройств управления вычислительных систем. Известно микропрограммное устройство управления, содержащее блоки па мяти адресных и операционных микрокоманд, регистр адреса, счетчик микрокоманд, блок синхронизации, элемен ты И, ИЛИ l . Недостатком этого устройства явля ется узкая область применения, обусловленная невозможностью реализации проверки приоритетных логических условий. Известно также микропрограммное устройство управления, содержащее ре гистры адреса и микрокоманд, блок памяти микрокоманд, элементы И, ИЛИ Недостатком устройства является узкая область применения. Наиболее близким к предлагаемому устройству по технической сущности и достигаемому эффекту является мИкпропрограммное устройство управления содержащее, блок памяти микрокоманд, регистр микрокоманд, коммутатор адреса, мультиплексор логических условий, первый коммутатор и блок элемен тов И, причем выход блока элементов И соединен с первой группой входов коммутатора адреса, группа выходов которого соединена с информащнэнными входами регистра адреса ьмкрокоманд, группа выходов регистра адреса микро команд соединена с соответствуюпщми fl разрядами (где (n + t) - число ячеек в блоке памяти микрокоманд), груц пы адресных входов блока памяти микрокоманд,- выходы немодифицируемых ра рядов группы выходов которого соединены с соответствующими входами немодифицируемьк разрядов второй группы входов коммутатора адреса, выход первого модифицируемого разряда груп пы выходов блока памяти и микрокоманд соединен с первым информационным входом первого коммутатора, выход которого соединен.с соответствующим -вход ом модифицируемых разрядов второй группы входов коммутатора адреса, группа выходов блока памяти микрокоманд соединена с группой информационных входов регистра микрокоманд первая группа выходов которого соединена с -группой информационных входов блока элементов И, выходы разрядов логических условий второй группы выходов регистра микрокоманд соединены с группой управляющих входов мультиплексора логических условий, .первая группа информационных входов которого соединена со входами разрядов бесприоритетных логических условий группы входов лог.ических условий устройства, выход первого управляющего разряда второй группы выходов регистра микрокоманд соединен с управляющим входом первого коммутатора 3 . Недостатком данного устройства является низкое быстродействие, обусловленное сложностью обработки прерываний на микропрограммном уровне. Для реализации реакции на приоритетные логические условия, вызывающие прерывания, в прототипе необходимо выполнить следующие действия. Периодически, с требуемой частотой реакции на приоритетные логические условия в устройстве должно передаваться управление специальной микропрограмме, осуществляющей так называемый полпинг М т.е. циклическую проверку этих логических условий в порядке уменьшения приоритета. В случае положительного исхода проверки какого-либо приоритетного условия управление должно передаваться микСопрограмме организа1даи реакции на это условие , а адрес возврата в микропрограмму поллинга - запоминаться. После завершения обработки данного приоритетного логического условия производится возврат к микропрограмме поллинга и далее на прерванную полингом микропрограмму.

Поскольку микропрограмма поллинга должна выполняться довольно часто, то быстродействие прототипа существенно снижается. Кроме того, после выполнения поллинга для осуществления возврата в основную микропрограмму для каждой точки возврата необходимо вырабатывать фиктивные логические условия, гщентифицирующие точку возврата. Сказанное относится также к возврату из микропрограммыобработчика прерывания.

Целью изобретения является повышение быстродейстзия,

Поставленная цель достигается тем,

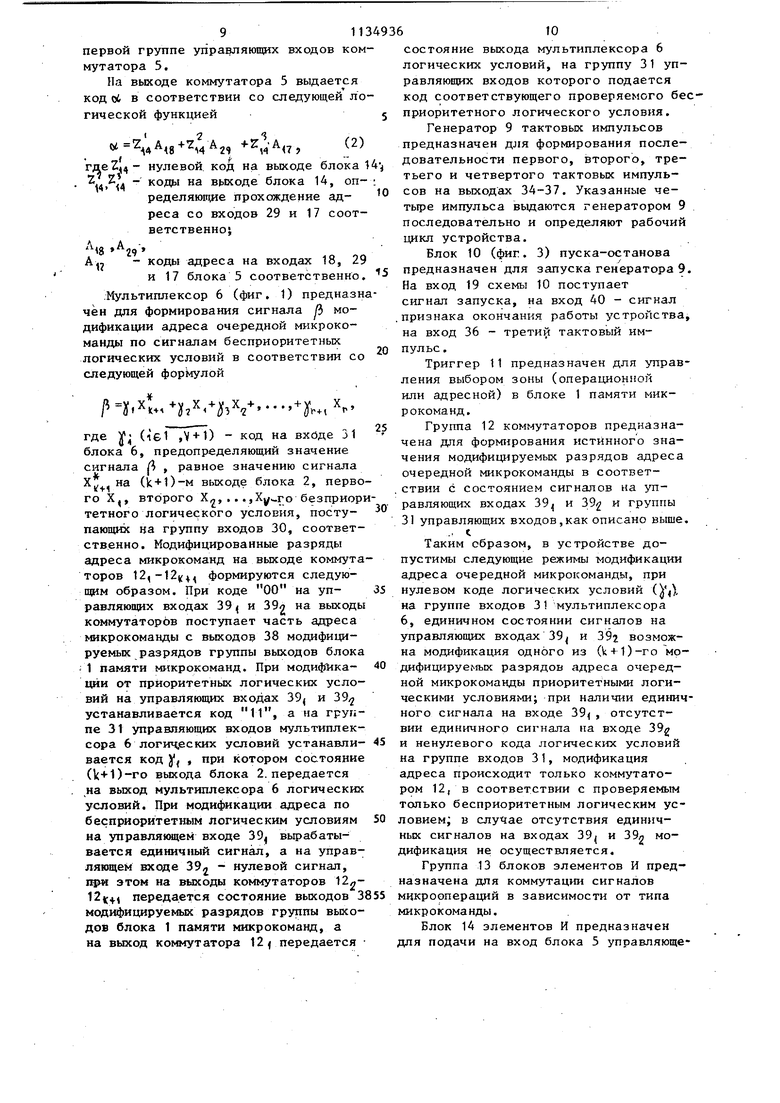

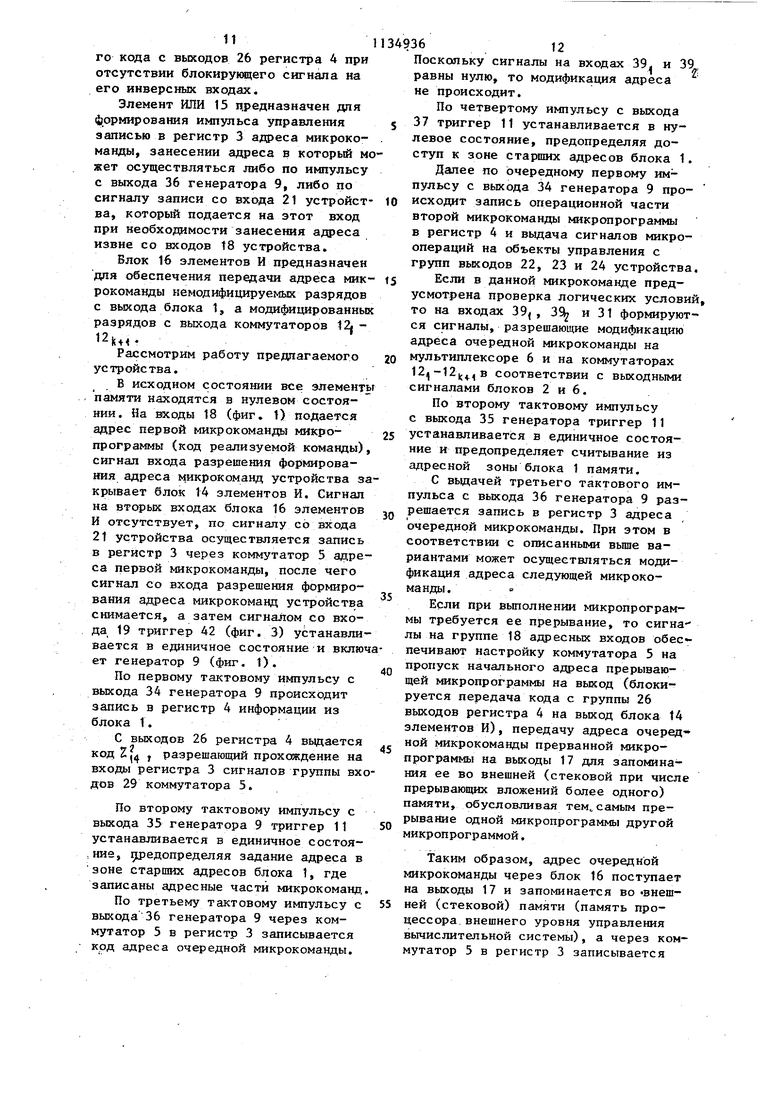

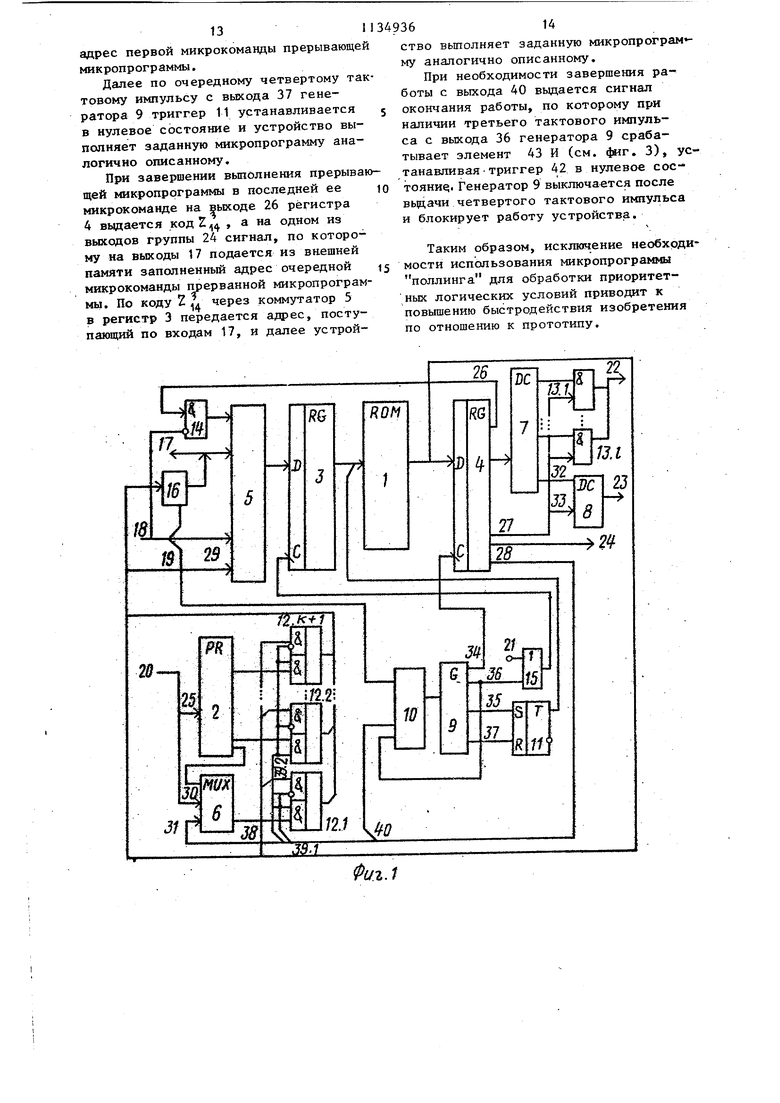

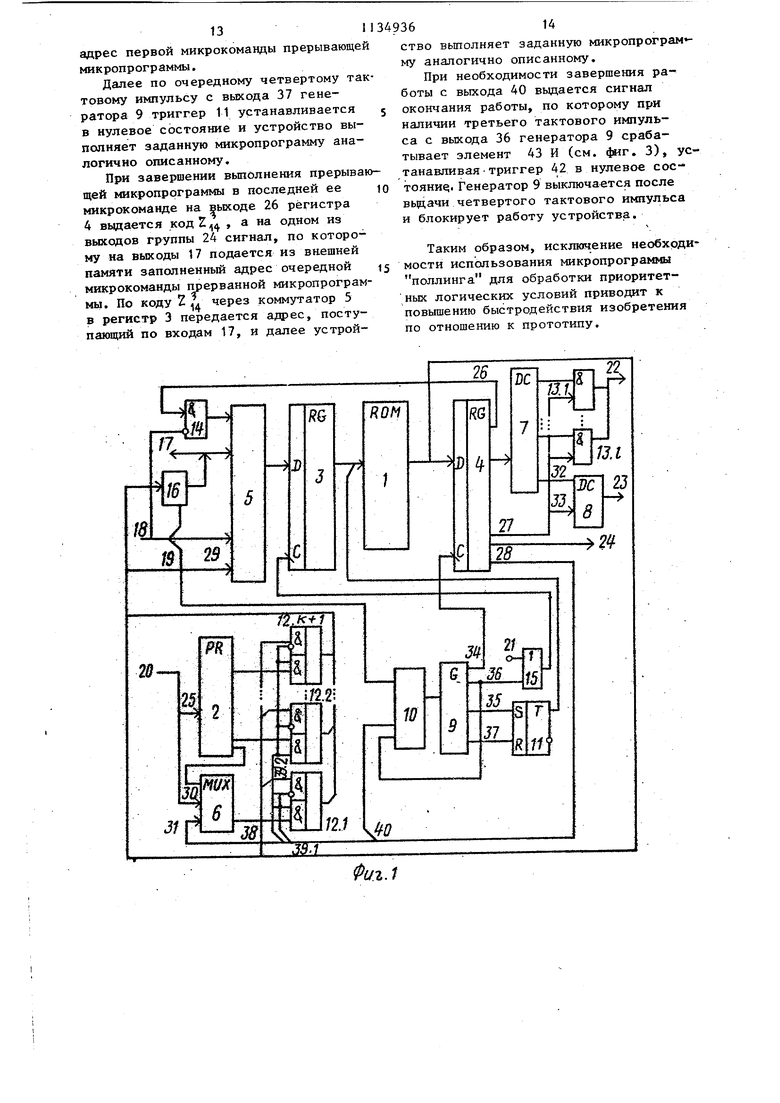

что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр адреса микрокомавд, регистр микрокоманд, коммутатор адреса, мульт шлёксор логических условий первый коммутатор, генератор тактовых импульсов и первый блок элементов и, причем группа выходов первого блока элементов И соединена с группой управляющих входов коммутатора адреса, группа вькодов которого соедииена с группой информационных вхдов регистра микрокоманд, )-и выход которого, где 1,2,..., (п-О ( П- разрядность адреса блокапамяти микрокоманд, соединен с -м адресным входом блока памя-ти микрокоманд, L-выходов немодифицируемых разрядов адреса кoтopoгo гдe число немодифицируемых разрядов адреса, соедине1Й51 с L информационными, входами первой группы коммутатора адреса,. группа вьвсодов Кода управления формированием адреса регистра микрокоманд соединена с группой прямых входов первого блока элементов И,вход разрешения формирования адреса микрокоманд устройства соединен с инверсными входами первого блока элементов; И, группа выходов кода операций блока памяти микрокоманд и группа выходов кода управления формирования адреса блока памяти микрокоманд соединены соответственно с первой и второй группами информационных входов регистра мик рокоманд, вход Синхронизации которого соединен с первым выходом генератора тактовых импульсов, группа вькодов кода логических условий регистра микрокоманд соединена с группой управляющих входов мультиплексора логических условий, (d-1) информационных входов которого, где Д - разрядность кода неприоритетных логический условий, соединеяы со входами неприоритетных логических условий группы входов логических условий устройства, выход мультиплексора логических условий соединен с первым информационным входом первого коммутатора, первая группа выходов кода микроопераций регистра микрокоманд является первой группой управляющих вькодов устройства, дополнительно введены блок приоритета логических условий, блок пуска-останова, триггер адресации, со второго по (k+1)-й коммутаторы, где (+1) - число модифицируемых разрядов адреса следующей микрокоманды, группу блоков элементов И, дешифратор типа микрокоманд, дешифратор несовместимых микроопераций, элемент ИЛИ и второй блок элементов И, причем группа выходов второго блока элементов И соединена с группой адресных выходов устройства и со второй группой информационных входов коммутатора адреса, третья группа информационных входов которого является группой адресных входов устройства, первые входы второго блока элементов И соединены со входом признака адресации и внешней памяти устройства, вход признака начала работы устройства соединен с первым входом блока пуска-останова, выход которого соединен со входом запуска генератора тактовых иьтульсов, группа вькодов кода типа микрокомандь ре гистра микрокоманд соединена с группой дешифратора типа микроко- . манд, -и выход которого, где 1,2,...,т, (tn - количество групп совместимых микроопераций первого типа) соединен с первыми входами i -го блока элементов И группы, вторые входы которого соединены со входами дешифратора несовместимых микроопераций и с выходами кода микроопераций регистра микрокоманд второй группы, группа выходов блоков элементов И группы является второй группой управ ляющих выходов устройства, группа выходов дешифратора несовместимьк микроопераций является третьей группой управляющих выходов устройства, стробирующий вход дешифратора несовместимых микроопераций соединен с (|71+1)-м выходом дешифратора типа микрокоманд, второй выход генератора тактовых импульсов соединен с первым входом элемента ИЛИ и со вторым входом блока пуска-останова, третий вход ко торого соединен с выходом признака конца работы регистра микрокоманд, третий и четвертый выходы генератора тактовых импульсов соединены соответственно со входами установки в 1 и установки в О триггера адресации выход которого соединен с п-м адресным входом блока памяти микрокоманд-, вход синхронизации регистра адреса микрокоманд соединен с выходом элемента ИЛИ, второй вход которого является входом управления записью адр са от внешних объектов устройства, входы приоритетных логических условий группы входов логических условий устройства соединены со входами блока приоритета логических условий, первый выход блока приоритета логических условий соединен cd -м информационным входом мультиплексора логи ческих условий, р -и выход блока приоритета логических условий, где р 2,3,...,(k+1) соединен с первым информационным входом р-го коммутатора группы, выходS -20 коммутатора, где 5 1,2, . ..,(k + 1) соединен с Q-M информационным входом первой гру пы коммутатора адреса (( (i+1), (1+2),. .,,() и с5-м входом пер вой группы второго блока элементов И Lвходов, второй группы которого сое динены с (.выходами немодифицируемых разрядов адреса блока памяти микрокоманд, второй информационный вход 5-го коммутатора соединен с 5-м выхо дом модифицируемых разрядов, адреса блока памяти микрокоманд, управляю1ЦИЙ вход р -го коммутатора соединен с выходом признака анализа приоритет ных логических условий регистра микрокоманд , выход признака анлиза неприоритетных логических условий которого соединен с управляющим взводом первого ком утатора. .I Кроме того, блок приоритета логи.ческих условий содержитk-элементов И, причем прямые входы k-злементов И являются |с-входаьш блока, инверсный вход первого элемента И является (k+O-M входом блока и первым выходом блока и соединен инверсным входом V -го элемента И, где / , ...,k, V-W, выxoдt-го элемента И, 1,2,...,(ic-1)j, является (t+1)-M выходом блока и соединен с (V/-1)-M инверсным входом V -го элемен та И, выходы к-го элемента И является (k+1)-M выходом блока. Кроме того, блок пуска-останова содержит триггер и элемент И, причем вход установки в ноль триггера является первым входом блока, первый и второй входы элемента И являются соответственно вторым и третьим входами блока, выход элемента И соединей со входом установки в 1 триггера, выход которого является-выходом блока. На фиг. 1 приведена функциональная схема предлагаемого микропрограммного устройства управления на фиг. 2 функциональная схема блока приоритета логических условий; на фиг. 3 функциональная схема блока пуска-останова . Устройство содержит блок 1 ламяти микрокоманд, блок 2 приоритета логических условий, регистр 3 адреса микрокоманд, регистр Д микрокоьитнд, коммутатор 5 адреса, мультшшексор 6 логических условий, дешифратор 7 типа микрокоманды, дешифратор 8 несовместных микроопераций, генератор 9 тактовых импульсов, блок 10 пускаостанова, триггер 11 адресации, груп12 коммутаторов 12. 12/7...., 12, коммутаторов iz; , t,,,., ,:, 12k+1, группу 13 блоков 13, Пл, .... 138 элементов И, первый блок 14 элементов И, элемент 15 ИЛИ, второй блок 16 элементов И, группу 17 адресных вькодов, группу 18 адресных входов устройства, вход 19 признака начала работы, группу 20 входов логических условий, вход 21 управления за писью адреса от внешних объектов. вторую группу 22 управляющих выходов, третью группу 23 управляющих вькодов, первую группу 24 управляющих выходов, группу входов 25 блока 2 приоритета огических условий, группы .26, 27, 28 выходов регистра 4, группу 29 входов коммутатора 5, группу 30 информационных входов мультиплексора 6 логических условий, группу 31 управяющих входов мультиплексора 6логи-. еских условий, стабилизирующий вход 32 дешифратора 8 несовместимых микрор операций, выходы несовместимых микроопераций 33, выходы 34-37 генератора тактовых импульсов, выходы 38 мо7 ифицируемых разрядов группы выходов лока 1 памяти микрокоманд, управляюие входы 39 и 39 группы ком {утатоов и выход 40 признака конца рабоы регистра 4. 71 Блок 2 приоритета логических усло вий (фиг. 2) содержит k-элементов И . Блок 10 пуска-останова (фиг. 3) (одержит триггер 42 и элемент И 43. Блок 1 (фиг. 1) предназначен для хранения микропрограммы работы устройства. Он может быть вьшолнен на типовых интеграпьньк схемах, например 556РУ1. В блоке 1 размещаются операционны и адресные части микрокоманд Причем операционные части микрокоманд расположены в зоне блока I с адресами 0-(), где (л + 1) - разрядность блока 1, а адресные части в зо не (). Для адресации внутри каждой из зон блока 1 необходимо разрядов регистра 3 адреса микрокоманды. Для межзонной селекции необходим еще один адресный разряд, который реализуется триггером 11. При единичном состоянии триггера 11 осуществляется обращение к адресной зоне блока 1, а при нулевом - к операционной. Описанная компоновка информации блока 1 Позволяет сократить на один разряд адресную часть микрокоманды з счет необходимости задания в формате микрокоманды только внутри зонного адреса. С выхода блока 1 адрес очередной микрокоманды поступает модифицируемым разрядами на группу 12 коммутато ров, выходы которого совместно с не- модифицируемыми разрядами адреса образуют группу разрядов инстинного адреса микрокоманды, соединенную с группой входов второгоблока 16 элементов И и группой 29 входов мультиплексора .5. Блок 2 (фиг. 2) приоритета логиче ких условий предназначен для выделения унитарного .кода сигнала логического условия старшего приоритета. Предлагаемое устройство позволяет обрабатывать логические условия двух типов: приоритетные и бесприоритетны Дпя подмножества приоритетных логических условий X(X%}f,, где X 5 подмножества приоритетных и бесприоритетных логических условий соответственно, U -множество логических условий ,блок 2 устанавливает порядок выбора для анализа в соответствии с системой функций y;{i6l,k гдеК-И - мощность множества X) его 6 Регистр 4 предназначен для хранения операционной части микрокоманды. С выходов 26 регистра 4 на блок 14 элементов И поступает код управления мультиплексора 14. Выходы типа микрокоманды регистра 4 соеданены со входами дешифратора 7, который в зависимости от типа реализуемой микрокоманды (тип микрокоманды соответствует объекту управления) открывает соответствующий блок 13; (ife TTS ) элементов И или дешифратор несовместимых ьшкроопераций 8, Группа выходов 27 регистра 4 предназначена для вьщачи кода микроопераций. Группа вькодон 24 предназначена дпя выдачи совместимых микроопераций. С группы выходов 28 регистра 4 поступает на группу входов 31 мультиплексора 6 код проверяемых логических условий, на вход 39 сигнал управления группой 12 коммутаторов, на вход 40 блока 10 - сигнал признака окончания работы устройства. Коммутатор 5 адреса предназначен для коммутации адреса очередной микрокоманды. При этом адрес очередной микрокоманды может поступать от следующих источников: начальный адрес микропрограммы работы устройства поступает с группы входов 18 устройства при нулевом (00) коде на группе управляющих входов коммутатора 5 адреса; адрес может поступать с блока 16 элементов И, предназначенного для передачи на хранение во внешнюю память и восстановления адреса микропрограммы, прерванной по сигналам с группы адресных входов 18 устройства, например, при коде 10 на группе выходов 26 регистра 4 и соответственно на группе управляющих входов коммутатора 5 адреса, третьим источником адреса является истинный адрес очередной микрокоманды, поступающий на группу входов 29 коммутатора 5, например при коде 01 на группе выходов 26 регистра 4 и соответственно на первой группе управляющих входов коммутатора 5. Па выходе коммутатора 5 выдается код об в соответствии со следующей логической функцией ,4Аг, ,(2) VneZ;,- нулевой ко на выходе блока 14 . - кода на вдаоде блока 14, оп . ределяющие прохождение адреса со входов 29 и 17 соответственно„ - коды адреса на входах 18, 29 и 17 блока 5 соответственно. /Мультиплексор 6 (фиг. 1) предназна чен для формирования сигнала р модификации адреса очередной микрокоманды по сигналам бесприоритетных логических условий в соответствии со следующей фopkyлoй .x....., где у (ie1 ,V + 1) - код на входе 31 блока 6, предопределяющий значение сигнала | , равное значению сигнала Х на (k+1)-M выходе блока 2, первого X,, второго Х2,...,.о безприоритетного логического условия, посту,, пающих на группу входов 30, соответств.енно. Модифицированные разряды адреса микрокоманд на выходе комнутаторов 12,-12((4 формируются следующим образом. При коде 00 на уп-3 равляющих входах 39 и 39 на выходы коммутаторов поступает часть адреса микрокоманды с выходов 38 модифицируемых разрядов группы выходов блока ;1 памяти микрокоманд. При модифйкации от приоритетных логических уеловий на управляющих входах 39( и устанавливается код 11, а на группе 31 управляющих входов мультиплексора 6 логических условий устанавли-4 вается код у , при котором состояние ()ro выхода блока 2. передается на выход мультиплексора 6 логических условий. При модификации адреса по бесприоритетным логическим условиям5 на управляющем входе 39,| вырабатывается единичный сигнал, а на управляющем входе 392 нулевой сигнал. ифи этом на выходы коммутаторов 12 12jf, передается состояние выходов 385 модифицируемых разрядов группы выходов блока 1 памяти микрокоманд, а на выход коммутатора 12 передается состояние выхода мультиплексора 6 логических условий, на группу 31 управляющих входов которого подается код соответствующего проверяемого бесприоритетного логического условия. Генератор 9 тактовых импульсов предназначен для формирования послеДовательности первого, второго, и четвертого тактовых импульсов на выходах 34-37. Указанные чегтлп ня Tij4TvonaY Утгд ч дн«ме tip - тыре импульса выдаются генератором 9 последовательно и определяют рабочий цикл устройства. Блок 10 (фиг. 3) пуска-останова предназначен для запуска генератора 9. На вход 19 схемы 10 поступает сигнал запуска, на вход 40 - сигнал признака окончания работы устройства, на вход 36 - третий тактовый импульс. Триггер 11 предназначен для управления выбором зоны (операцион юй или адресной) в блоке 1 памяти микрокоманд. Группа 12 коммутаторов предназначена для формирования истинного значения модифицируемых разрядов адреса очередной микрокоманды в соответствии с состоянием сигналов на уп 39. и 39. и группы ,it управляющих входов,как описано выше, .с- Таким образом, в устройстве допустимы следующие режимы модификации адреса очередной микрокоманды, при нулевом коде логических условий (V), на группе входов 31 мультиплексора 6, единичном состоянии сигналов на управляющих входах 39 и 39 возможна модификация одного из (k+1)-ro мрдифицируемых разрядов адреса очеред- ной микрокоманды приоритетными логическими условиями; при наличии единичного сигнала на входе 39, отсутствии единичного сигнала па входе 39д и ненулевого кода логических условий на группе входов 31, модификация адреса происходит только коммутатором 12, в соответствии с проверяемым только бесприоритетным логическим условием; в случае отсутствия единичньк сигналов на входах 39 и 39 моификация не осуществляется. Группа 13 блоков элементов И пред- назначена для коммутации сигналов икроопераций в зависимости от типа икрокоманды. Блок 14 элементов И предназначен ля подачи на вход блока 5 управляющего кода с выходов 26 регистра 4 при отсутствии блокирующего сигнала на его ииверсных входах. Элемент ИЛИ 15 предназначен для формирования импульса управления записью в регистр 3 адреса микрокоманды, занесении адреса в который мо жет осуществляться либо по импульсу с выхода 36 генератора 9, либо по сигналу записи со входа 21 устройства, который подается на этот вход при необходимости занесения адреса извне со входов 18 устройства. Блок 16 элементов И предназначен для обеспечения передачи адреса микрокоманды немодифицируемых разрядов с выхода блока 1, а модифицированных разрядов с выхода коммутаторов 12| 12k,. Рассмотрим работу предлагаемого устройства. В исходном состоянии все элементы памяти находятся в нулевом состоянии. На кходы 18 (фиг. 1) подается адрес первой микрокоманды микропрограммы (код реализуемой команды), сигнал входа разрешения формирования адреса микрокоманд устройства за крывает блок 14 элементов И. Сигнал на вторых входах блока 16 элементов И отсутствует, по сигналу со входа 21 устройства осуществляется запись в регистр 3 через коммутатор 5 адреса первой микрокоманды, после чего сигнал со входа разрешения формирования адреса микрокоманд устройства снимается, а затем сигналом со входа 19 триггер 42 (фиг. 3) устанавли вается в единичное состояние и вклю ет генератор 9 (фиг, 1). По первому тактовому импульсу с выхода 34 генератора 9 происходит запись в регистр 4 информации из блока 1. С выходов 26 регистра 4 вьщается код I разрешающий прохождение на входы регистра 3 сигналов группы вх дов 29 коммутатора 5. По второму тактовому импульсу с выхода 35 генератора 9 триггер 11 устанавливается в единичное состоя,ние, гцэедопределяя задание адреса в зоне старших адресов блока 1, где записаны адресные части микрокоманд По третьему тактовому импульсу с выхода 36 генератора 9 через коммутатор 5 в регистр 3 записывается код адреса очередной микрокоманды. Поскольку сигналы на входах 39. и 39 равны нулю, то модификация адреса не происходит. По четвертому импульсу с выхода 37 триггер 11 устанавливается в нулевое состояние, предопределяя доступ к зоне старших адресов блока 1. Далее по очередному первому импульсу с выхода 34 генератора 9 происходит запись операционной части второй микрокоманды микропрограммы в регистр 4 и выдача сигналов микроопераций на объекты управления с групп выходов 22, 23 и 24 устройства. Если в данной микрокоманде предусмотрена проверка логических условий, то на входах 39, 39 и 31 формируются сигналы, разрешающие модификацию адреса очередной микрокоманды на мультиплексоре 6 и на коммутаторах 12,j-12,,B соответствии с выходными сигналами блоков 2 и 6. По второму тактовому импульсу с выхода 35 генератора триггер 11 устанавливается в единичное состояние и предопределяет считывание из адресной зоны блока 1 памяти. С выдачей третьего тактового импульса с выхода 36 генератора 9 разрешается запись в регистр 3 адреса очередной микрокоманды. При этом в соответствии с описанными вьш1е вариантами может осуществляться модификация адреса следующей микрокоманды. ЕСЛИ при вьшолнении микропрограммы требуется ее прерывание, то сигна лы на группе 18 адресных входов обес«печивают настройку коммутатора 5 на пропуск начального адреса прерывающей микропрограммы на выход (блокируется передача кода с группы 26 выходов регистра 4 на выход блока 14 элементов И), передачу адреса очеред ной микрокоманды прерванной микропрограммы на выходы 17 для запоминания ее во внешней (стековой при числе прерывающих вложений более одного) памяти, обусловливая тем самым прерывание одной микропрограммы другой микропрограммой. Таким образом, адрес очередной микрокоманды через блок 16 поступает на выходы 17 и запоминается во -внешней (стековой) памяти (память процессора внешнего уровня управления вычислительной системы), а через коммутатор 5 в регистр 3 записывается

адрес первой микрокоманды прерывающей микропрограммы.

Далее по очередному четвертому тактовому импульсу с выхода 37 генератора 9 триггер 11 устанавливается в нулевое состояние и устройство выполняет заданную микропрограмму аналогично описанному.

При завершении вьтолнения прерывающей микропрограммы в последней ее микрокоманде на |ькоде 26 регистра 4 выдается код2,4 одном из выходов группы 24 сигнал, по которому на выходы 17 подается из внешней памяти заполненный адрес очередной микрокоманды гшерванной микропрограммы. По коду 1 ц через коммутатор 5 в регистр 3 передается адрес, поступающий по входам 17, и далее устройство вьшолняет заданную микропрограм му аналогично описанному.

При необходимости завершения работы с выхода 40 выдается сигнал окончания работы, по которому при наличии третьего тактового импульса с выхода 36 генератора 9 срабатывает элемент 43 И (см. 4«г. 3), устанавливая триггер 42 в нулевое состояние- Генератор 9 выключается после вьдачи четвертого тактового импульса и блокирует работу устройства.

Таким образом, исключение необходимости использования микропрограммы поллинга для обработки приоритетных логических условий приводит к повышению быстродействия изобретения по отношению к прототипу.

i/.Z.1

мЧГ-nrrfrill 1РЦ , t

fic

Cl

ю

««««. o

Й

.J

| ЬГеолецян А.Г | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Программирование и микропрограммирование, М., Статистика 1979, c.ll15 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синтез и оптимизация программ с использованием р-функ.ций | |||

| Экспресс-информация | |||

| Сер | |||

| Вычислительная техника, 1982, № 36, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Анг- ло-русско-немецко-францу зский толковый словарь по вычислительной технике и обработке данных | |||

| Под ред | |||

| Дородницына, М., Русский язык, 1978. | |||

Авторы

Даты

1985-01-15—Публикация

1983-07-13—Подача