Изобретение относится к. цифровым вычислительным устройствам, а именно к устройствам для формирования векторов, и может быть использовано в самых различных устройствах, например, для построения на экране ЭЛТ векторов произвольных наклонов и величин.

Цель изобретения - повышение быстродействия за счет одновременно- го формирования рескольких векторов

На чертеже приведен схема интерполятора. .

Интерполятор содержит регистры 1-4, вычитатели 5 и 6, умножители 7 и 8, сумматоры 9 и 10, блок 11 постоянной памяти и счетчик 12.

Интерполятор работает следующим образом.

На входы X и у интерполятора поступают координаты X и У узловых точек интерполирования.; Запись координат производится последовательно сначала в четный, затем в нечетный регистры. Например, имеется последовательность координат узловых

гУ zn-i

точек Хр,у. . X,

о

УгпУin- 1п

из указанной последовательности координаты XQ, Xj, .tn y.jf, будут записаны в четные регистры 1 и 3, а координаты х , у -, х,

У2й-1 в нечетные регистры 2 и 4. Вычитатели 5 и 6 всегда формируют разности д У шГУмин признак того, какая из координат - четная .или нечетная больше. Сформированные разности дх и Ду поступают соответственно на четвертый и пятый входы блока 11.

968951

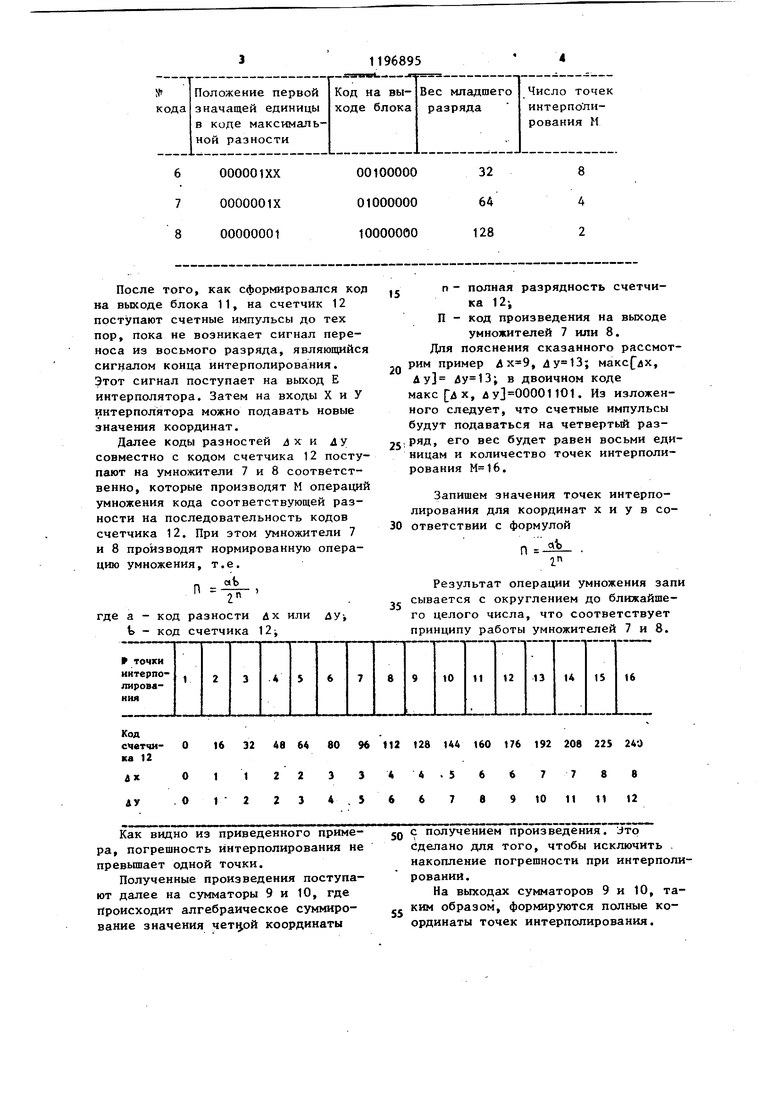

Блок 11 работает при наличии на его первом входе сигнала разрешения Р. При этом при наличии команды записи W и по приходу очередного 5 строб-импульса на втором или третье выходе блока 11 появится сигнал занесения соответственно в четные 1, 3 или нечетные 2, 4 регистры. Далее из поступающих на блок 11 разностей Л X и л у вычисляется максимальная по модулю величина мо(, 4yJ и определяется номер разряда, в котором находится первая единица со стороны старших разрядов. Например, дх 10001101, ду 00010010, , ду} дх 10001101. Первая значащая единица со стороны старших разрядов находится в восьмом разряде, считая первый разряд младшим, а восьмой - старшим. В результате проведенного анализа блок 11 сформирует на выходе код 00000001, поступакиций на счетчик 12 и разрешающий прохождение счетных импульсов на 25 первый - самый младший - разряд счетчика 12. Если в максимальной разности первая значащая единица будет в седьмом разряде, то код на выходе блока логики будет 00000010 и счетные импульсы на счетчик 12 будут проходить уже не на первый, а на второй разряд.

Ниже показано соответствие, выходного кода блока 11 положению первой значащей единицы в коде максимальной разности. Единица в выходном коде блока 11 определяет, на какой разряд счетчика 12 будут поступать счзтныё импульсы, т.е. какой разряд в этом случае будет считаться младшим, а значит и его вес, а также число точек интерполирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| Устройство для вывода графической информации | 1978 |

|

SU752403A1 |

| Интерполятор | 1985 |

|

SU1309039A1 |

| Устройство для формирования графических изображений | 1978 |

|

SU752404A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1317452A1 |

| Устройство для регистрации информации | 1978 |

|

SU769576A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Двумерный линейный интерполятор | 1985 |

|

SU1269152A1 |

| Многоканальный интерполятор для программного управления многокоординатным станком | 1978 |

|

SU746429A1 |

ИНТЕРПОЛЯТОР, содержащий .два регистра, два умножителя, два сумматора, блок постоянной , причем выходы умножителей подключены к первым информационным входам сумматоров, выходы которых являются выходами координат интерполятора, отличающийся тем, что, с целью повышения быстродействия за счет одновременного фор мирования нескольких векторов, в него введены два регистра, два вычитателя и счетчик, причем второй информационный вход первого сумматора, первый информационньй вход первого вычитателя и второй информационный вход второго сумматора, первый информационный вход второго вычитателя соединены с выходами г .y.,.. JJ первого и третьего регистров соответственно, выходы второго и четвертого регистров подключены к вторым информационным входам первого и второго вычитателей соответственно, выходы которых подключены к первой и второй группам адресных входов блока постоянной памяти и к первым информационным входам умножителей, к вторым информационным входам которых подключены информационные входы счетчика, выходы переноса первого и второго вычитателей соеди нены с входами знака первого и второго сумматоров соответственно, вход счетчика соединен с информационным выходом блока постоянной па(Л мяти, выход переноса счетчика является выходом конца интерполирования интерполятора, выход поля разрешения записи первой координаты блока постоянной памяти соединен с входами разрешения записипервого и третьего регистров, а выход со поля разрешения записи второй коор05 00 динаты блока постоянной памяти соединен с входами разрешения записи ю сд второго и четвертого регистров, информационные входы первого и второго регистров и информационные входы третьего и четвертого регистров попарно объединены и являются входами первой и второй координат интерполятора, входы разрешения, записи и синхронизации блока постоянной памяти являются группой управляющих входов интерполятора.

00000001 00000010 00000100 00001000 00010000

256

128

64

32

16

После того, как сформировался кор на выходе блока 11, на счетчик 12 поступают счетные импульсы до тех пор, пока не возникает сигнал переноса из восьмого разряда, являющийся сигналом конца интерполирования. Этот сигнал поступает на выход Е интерполятора. Затем на входы X и У интерполятора можно подавать новые значения координат.

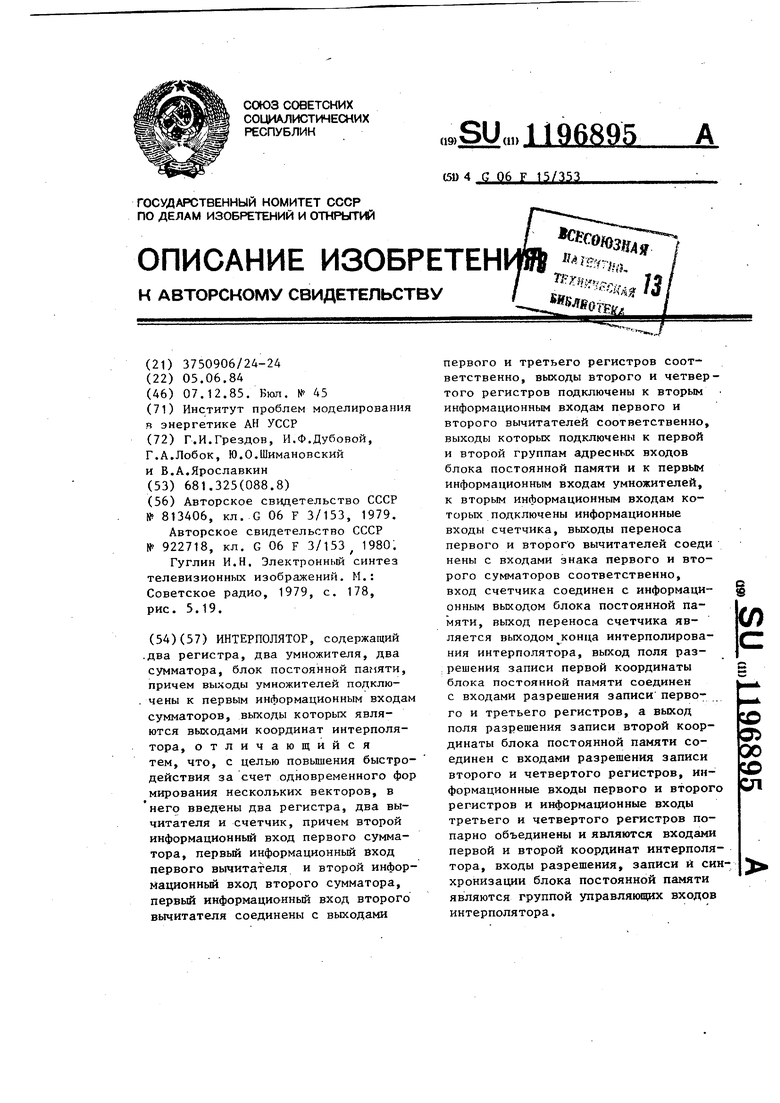

Далее коды разностей 4х и у совместно с кодом счетчика 12 поступают на умножители 7 и 8 соответственно, которые производят М операций умножения кода соответствующей разности на последовательность кодов счетчика 12. При этом умножители 7 и 8 производят нормированную операцию умножения, т.е.

П - « 2

где а - код разности лх или ду-, Ь - код счетчика 12j

Как видно из приведенного примера, погрешность интерполирования не превьш1ает одной точки.

Полученные произведения поступают далее на сумматоры 9 и 10, где происходит алгебраическое суммирование значения координаты

п- полная разрядность счетчика 12-, П - код произведения на выходе

умножителей 7 или 8. Для пояснения сказанного рассмотрим пример , , 4у в двоичном коде , ду 00001101. Из изложенного следует, что счетные импульсы будут подаваться на четвертьй раз25,ряд, его вес будет равен восьми единицам и количество точек интерполирования .

Запишем значения точек интерполирования для координат х и у в соответствии с формулой

flt

П -

1

Результат операции умножения запи сывается с округлением до ближайшего целого числа, что соответствует принципу работы умножителей 7 и 8.

5Q с получением произведения. Утр

Сделано для того, чтобы исключить . накопление погрешности при интерполирований.

На выходах сумматоров 9 и 10, таким образом, формируются полные координаты точек интерполирования.

| Устройство для отображения графи-чЕСКОй иНфОРМАции HA эКРАНЕТЕлЕВизиОННОгО пРиЕМНиКА | 1978 |

|

SU813406A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для генерации векторов на индикаторе с черезстрочной разверткой | 1980 |

|

SU922718A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гуглин И.Н, Электронный синтез телевизионных изображений | |||

| М.: Советское радио, 1979, с | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-05—Подача