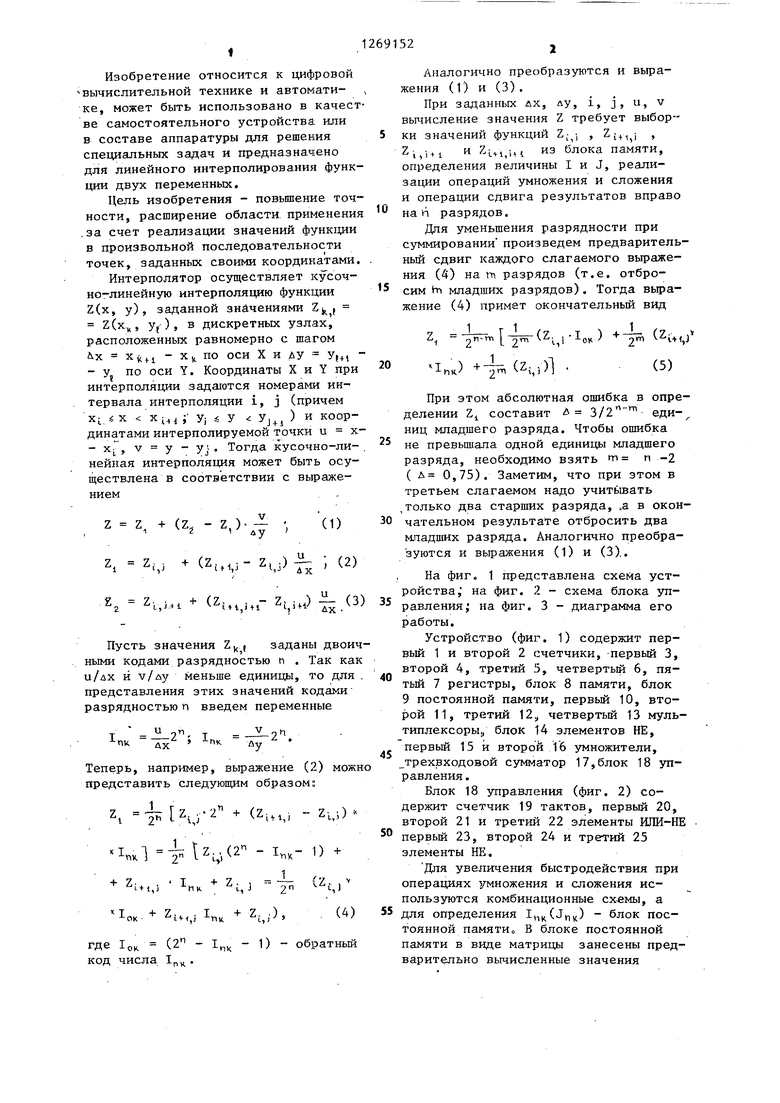

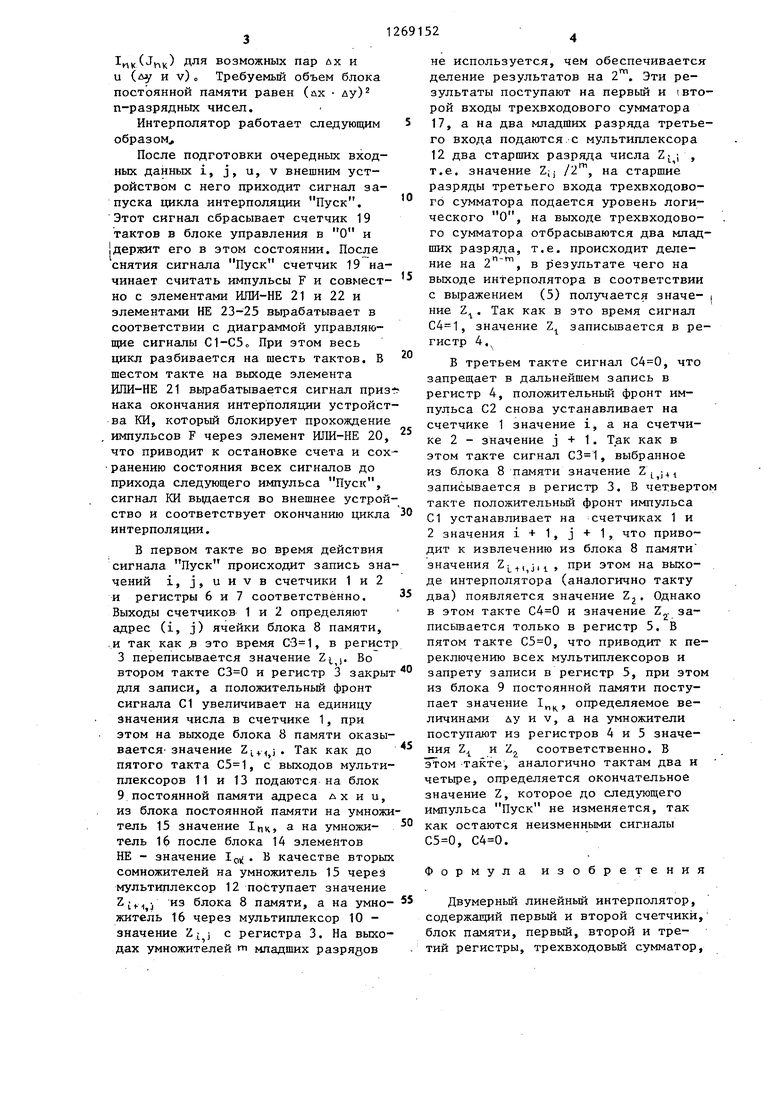

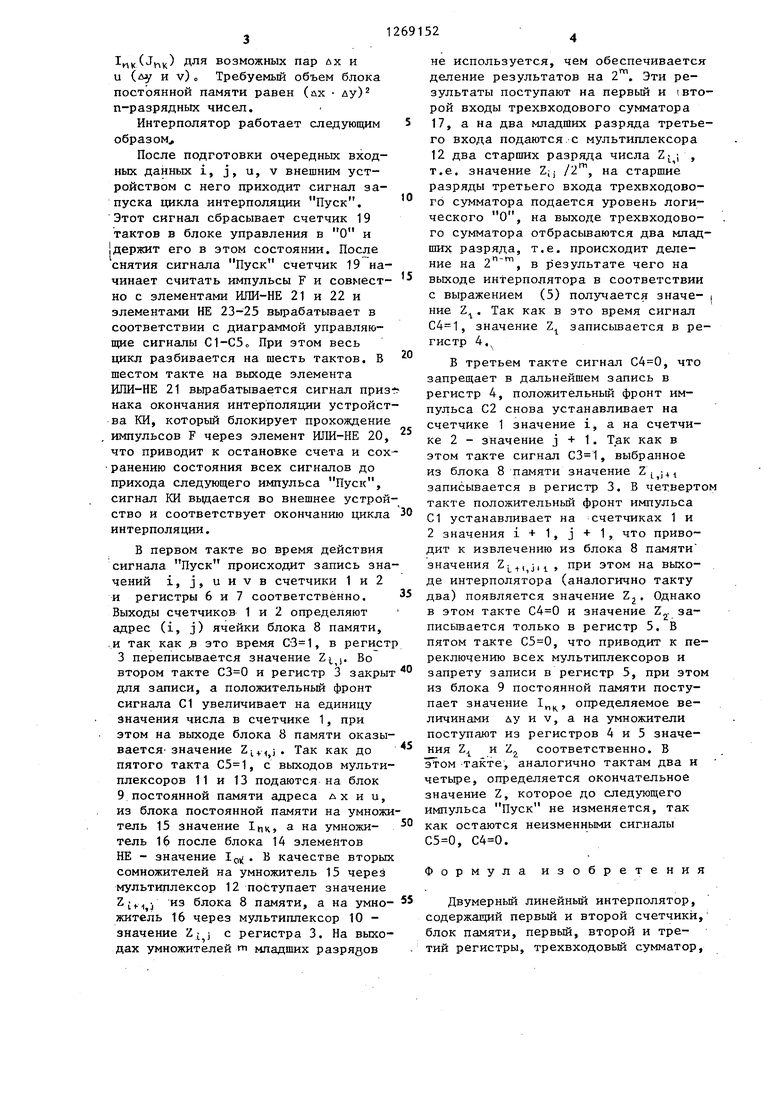

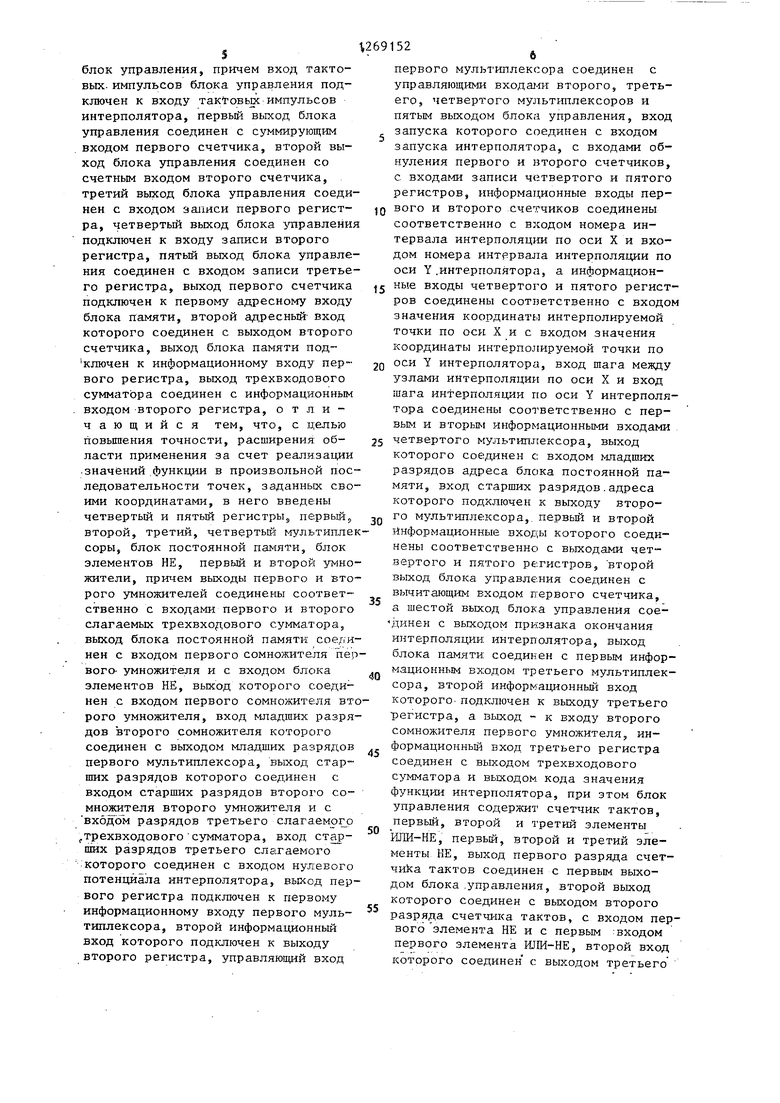

Изобретение относится к цифровой вычислительной технике и автоматике, может быть использовано в качес ве самостоятельного устройства или в составе аппаратуры для решения специальных задач и предназначено для линейного интерполировани51 функ ции двух переменных. Цель изобретения - повышение точ ности, расширение области применени .за счет реализации значений функции в произвольной последовательности точек, заданных своими координатами Интерполятор осуществляет кусочно-линейную интерполяцию функции Z(x, у), заданной значениями Zj , Z(x.|,, У( ) в дискретных узлах, расположенных равномерно с шагом й.х Х(( оси X и ду у у по оси Y. Координаты X и Y при интерполяции задаются номерами интервала интерполяции i, j (причем X S X X i 1 ; У; 4 у : Vj J ) и координатами интерполируемой точки и х - х-, V у - У. Тогда кусочно-линейная интерполяция может быть осуществлена в соответствии с выражениемz z + (Z, - z,).- - (1) Z, Z;,J - (Zuv- ZI,J)T- ; (2) l,j.4i + (Ui,itr L.JM) - , 2 Пусть значения Z. , заданы двоич ными кодами разрядностью п . Так как и/дх и v/ду меньше единицы, то для представления этих значений кодаки разрядностью п введем переменные U оп , V ц « -Lui; Т . ДХ Лу Теперь, например, выражение (2) можн представить следующим образом:; i i «1«к1 ,;,(2 - I,- 1) н (7 V T- 4) IHK Z.j Z,,;), (4) где IOK (2 - 1,ц - 1) - обратный код числа . Аналогично преобразуются ивьфажения (Г) и (3) . При заданных лх, ду, i, j,u, v вычисление значения Z требуетвыборКИ значений функций , Z;,; , и , из блока памяти, определения величины I и J, реализации операций умножения и сложения и операции сдвига результатов вправо на vi разрядов. Для уменьшения разрядности при суммировании произведем предварительный сдвиг каждого слагаемого выражения (4) на m разрядов (т.е. отбросим (т( младших разрядов) . Тогда выражение (4) примет окончательный вид 7 JГ J( 7 loti) i+SJ i - n L 2 (Zi,i)l . ПЧ- 2 При этом абсолютная ошибка в определении Z составит А 3/2 единиц младшего разряда. Чтобы ошибка не превьш1апа одной единицы младшего разряда, необходимо взять п -2 ( А 0,75). Заметим, что при этом в третьем слагаемом надо учитьшать только два старших разряда, л в окончательном результате отбросить два м.падших разряда. Аналогично преобразуются и вьфажения (1) и (3).. На фиг. 1 представлена схема устройства, на фиг. 2 - схема блока управления; на фиг. 3 - диаграмма его работы. Устройство (фиг. 1) содержит первый 1 и второй 2 счетчики, первый 3, второй 4, третий 5, четвертый 6, пятый 7 регистры, блок 8 памяти, блок 9 постоянной памяти, первьй 10, второй 11, третий 12., четвертый 13 мультиплексоры,, блок 14 элементов НЕ, первый 15 и второй 16 умножители, трехвходовой сумматор 17,блок 18 управления. Блок 18 управления (фиг. 2) содержит счетчик 19 тактов, первый 20, второй 21 и третий 22 элементы ИЛИ-НЕ . первый 23, второй 24 и третий 25 элементы НЕ. Дпя увеличения быстродействия при операциях умножения и сложения используются комбинационные , а для определения I,i(Jn(() - блок постоянной памяти В блоке постоянной памяти в виде матрицы занесены предварительно вычисленные значения

I(Jf() для возможных пар дх и U (лу и v)о Требуемый объем блока постоянной памяти равен (дх ду) п-разрядных чисел.

Интерполятор работает следующим образом

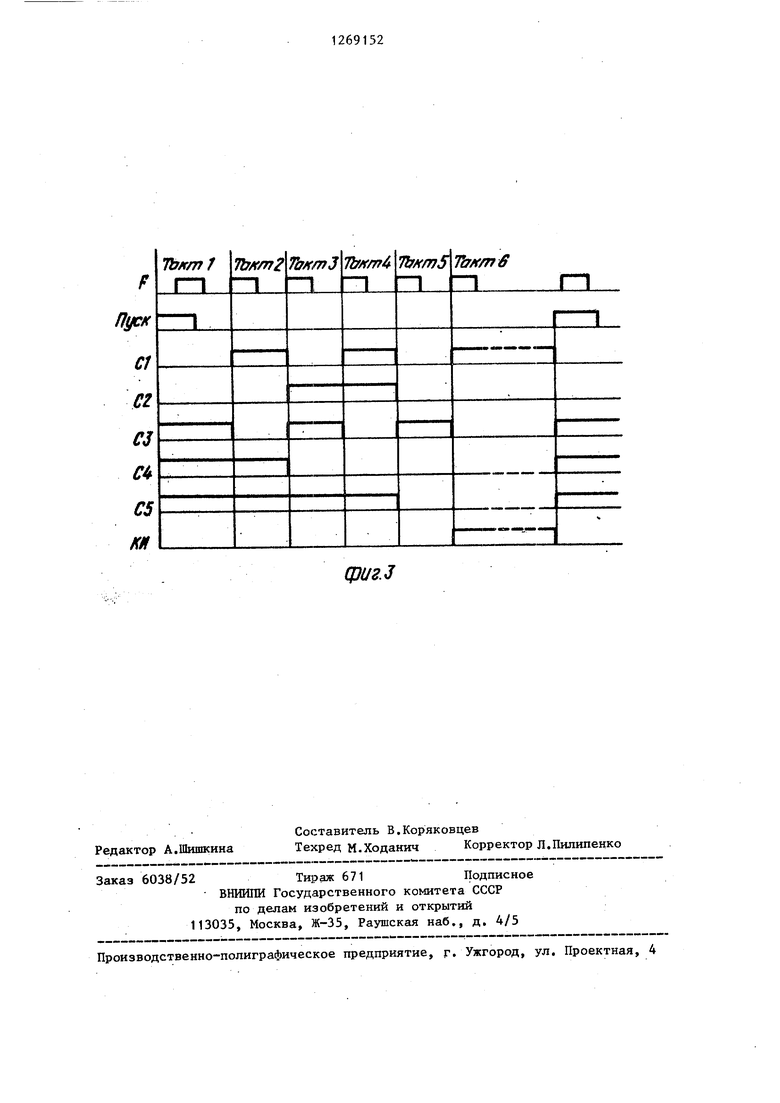

После подготовки очередных входных данных i, j, u, V внешним устройством с него приходит сигнал запуска цикла интерполяции Пуск. Этот сигнал сбрасывает счетчик 19 тактов в блоке управления в О и держит его в этом состоянии. После снятия сигнала Пуск счетчик 19 начинает считать импульсы F и совместно с элементами ИЛИ-НЕ 21 и 22 и элементами НЕ 23-25 вырабатывает в соответствии с диаграммой управляющие сигналы С1-С5о При этом весь цикл разбивается на шесть тактов. В шестом такте на выходе элемента ИЛИ-НЕ 21 вырабатывается сигнал приз нака окончания интерполяции устройства КИ, который блокирует прохождение импульсов F через элемент ШШ-НЕ 20, что приводит к остановке счета и сохранению состояния всех сигналов до прихода следзтощего импульса Пуск, сигнал КИ вьщается во внешнее устройство и соответствует окончанию цикла интерполяции.

В первом такте во время действия сигнала Пуск происходит запись значений i, j, u и V в счетчики 1 и 2 и регистры 6 и 7 соответственно. Выходы счетчиков 1 и 2 определяют адрес (i, j) ячейки блока 8 памяти, ,и так как это время , в регист 3 переписывается значение Zj. Во втором такте и регистр 3 закрыт для записи, а положительньй фронт сигнала С1 увеличивает на единицу значения числа в счетчике 1, при этом на выходе блока 8 памяти оказывается- значение Zl.j . Так как до пятого такта , с выходов мультиплексоров 11 и 13 подаются на блок 9 постоянной памяти адреса дх и и, из блока постоянной памяти на умножитель 15 значение 1,, а на умножитель 16 после блока 14 элементов НЕ - значение Ip,; . В качестве вторых сомножителей на умножитель 15 через мультиплексор 12 поступает значение 2ui,j з блока 8 памяти, а на умножитель 16 через мультиплексор 10 значение с регистра 3. На выходах умножителей m младших разрязов

не используется, чем обеспечивается деление результатов на 2. Эти результаты поступают на первый и (второй входы трехвходового сумматора 17, а на два младших разряда третьего входа подаются.с мультиплексора 12 два старших разряда числа , т.е. значение Z;j /2, на старшие разряды третьего входа трехвходового сумматора подается уровень логического О, на выходе трехвходового сумматора отбрасьшаются два младших разряда, т.е. происходит деление на 2, в результате чего на выходе интерполятора в соответствии с выражением (5) получается значение Z. Так как в это время сигнал , значение Z записьшается в регистр 4.

В третьем такте сигнал , что запрещает в дальнейшем запись в регистр 4, положительный фронт импульса С2 снова устанавливает на счетчике 1 значение i, а на счетчике 2 - значение j + 1. Так как в этом такте сигнал , выбранное из блока 8 памяти значение записывается в регистр 3. В четверто такте положительный фронт импульса С1 устанавливает на счетчиках 1 и 2 значения i + 1, j + 1, что приводит к извлечению из блока 8 памяти значения Z, j, , при этом на выходе интерполятора (аналогично такту два) появляется значение Z. Однако в этом такте и значение Z записБшается только в регистр 5. В пятом такте , что приводит к переключению всех мультиплексоров и запрету записи в регистр 5, при этом из блока 9 постоянной памяти поступает значение .„, определяемое величинами ду и V, а на умножители поступают из регистров 4 и 5 значения Z и Z соответственно. В этом такте, аналогично тактам два и четыре, определяется окончательное значение Z, которое до следующего импульса Пуск не изменяется, так как остаются неизменньп-ш сигналы , .

Формула изобретения

Двумерный линейный интерполятор, содержащий первый и второй счетчики, блок памяти, первый, второй и третий регистры, трехвходовый сумматор. блок управления, причем вход тактовых, импульсов блока управления подключен к входу такТовьк импульсов интерполятора, первый выход блока управления соединен с суммирующим входом первого счетчика, второй выход блока управления соединен со счетным входом второго счетчика, третий выход блока управления соединен с входом записи первого регистра, четвертый выход блока управления подключен к входу записи второго регистра, пятый выход блока управления соединен с входом записи третьего регистра, выход первого счетчика подключен к первому адресному входу блока памяти, второй адресный- вход которого соединен с выходом второго счетчика, выход блока памяти подключен к информационному входу первого регистра, выход трехвходового сумматора соединен с информационным входом второго регистра, отличающийся тем, что, с целью повышения точности, расширения области применения за счет реализации .значений функции в произвольной пос ледовательности точек, зэданньк сво ими координатами, в него введены четвертый и пятый регистры, первый,, второй, третий, четвертый мультипле соры, блок постоянной , блок элементов НЕ, первый и второй умно жители, причем выходы первого и вто рого умножителей соединены соответственно с входами первого и второго слагаемых трехвходового сумматора, выход блока постоянной памяти соеди нен с входом первого сомножите.пя пер вого- умножителя и с входом блока элементов НЕ, выход которого соединен с входом первого сомножителя вт рого умножителя, вход младших разря дов второго сомножителя которого соединен с выходом младших разрядов первого мультиплексора, выход старших разрядов которого соединен с входом старших разрядов второго сомножителя второго умножителя и с входём разрядов третьего слага. ,трехвходовогосумматора, вход старпшх разрядов третьего слагаемого которого соединен с входом нулевого потенциала интерполятора, выход пер вого регистра подключен к первому информационному входу первого мультиплексора, второй информа.ционный вход которого подключен к выходу второго регистра, управляющий вход первого мультиплексора соединен с управляющш-ш входш и второго, третьего, четвертого мульт шлексоров и пятым выходом б.пока управления, вход запуска которого соединен с входом запуска интерполятора, с входами обнуления первого и второго счетчиков, с входами записи четвертого и пятого регистров, информационные входы первого и второго счетчиков соединены соответственно с входом номера интервала интерполяции по оси X и входом номера инт(рвала интерполяции по оси Y .интерпо.пятора, а информационные входы четвертого и пятого регистров соединены соответственно с входом значения координаты интерполируемой точки по оси X и с входом значения координаты интерполируемой точки по оси Y интерполятора, вход шага между узлами интерполяции по оси X и вход шага интерполяции по оси Y интерполятора соединены соответственно с первым и вторым информационными входами . четвертого мультиплексора, выход которого соединен с входом младших разрядов адреса блока постоянной памяти, вход старших разрядов.адреса которого подключен к выходу второго мультиплексора,, первьй и второй информационные входы которого соединены соответственно с выходами четвертого и пятого регистров, второй выход блока управлб.ния соединен с вычитающим входом первого счетчика, а шестой выход блока управления соединен с выходом признака окончания интерполяции интерполятора, выход блока памяти соединен с первым информационнь м входом третьего мультиплексора, второй информационный вход которого, подключен к выходу третьего регистра, а выход - к входу второго сомножителя первого умножителя, информационный вход третьего регистра соединен с выходом трехвходового сумматора и выходом кода значения функции интерполятора, при этом блок управления содержит счетчик тактов, первый, второй и третий элементы ИШ-НЕ, первый, второй и третий элементы НЕ, выход первого разряда счетчи а тактов соединен с первым выходом блока .управления, второй выход которого соединен с выходом второго разряда счетчика тактов, с входом первого элемента НЕ и с первым :входом первого элемента ШШ-НЕ, второй вход которого соединен с выходом третьего

разряда счетчика тактов и с входом второго элемента НЕ, выход которого соединен с первым входом второго элемента ШШ-НЕ, второй вход которого соединен с выходом первого элемента НЕ, выход первого разряда счетчика тактов соединен с входом третьего элемента НЕ, выход которого соединен с третьим выходом блока управления, вькоды первого и второго элементов ИЛИ-НЕ соединены с четвертым и шестым выходами блока управления

соответственно, кроме того, выход второго элемента ИЛИ-НЕ соединен с первым входом третьего элемента ИЛИ-НЕ, выход которого подключен к

счетному входу счетчика тактов, вход обнуления которого подключен к входу запуска блока управления, синхровход блока управления подключен к второму входу третьего элемента

ИЛИ-НЕ, выход второго элемента НЕ подключен к пятому выходу блока управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| Интерполятор | 1986 |

|

SU1405074A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Цифровой интерполятор | 1983 |

|

SU1140098A1 |

Изобретение относится к средствам обработки экспериментальной информации. Целью изобретения является повышение точности и расширение области применения за счет реализации значений функции в произвольной последовательности точек. Предлагаемьй интерполятор содержит два счетчика 1, 2, блок 8 памяти, блок -9 постоянной памяти, блок 18 управления, трехвходовый сумматор 17 пять регис1т ов 3-7, блок 14 элемен7 тов НЕ, четьфе мультиплексора 10-13 и два умножителя 15, 16. Указаннаяi совокупность признаков позволяет достигнуть цель изобретения. 3 ил. (Л С ки ipuz.f тг

/w

фиг.2

(PU2.J

| Устройство для сбора и удаления мусора | 1987 |

|

SU1413045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1985-01-22—Подача