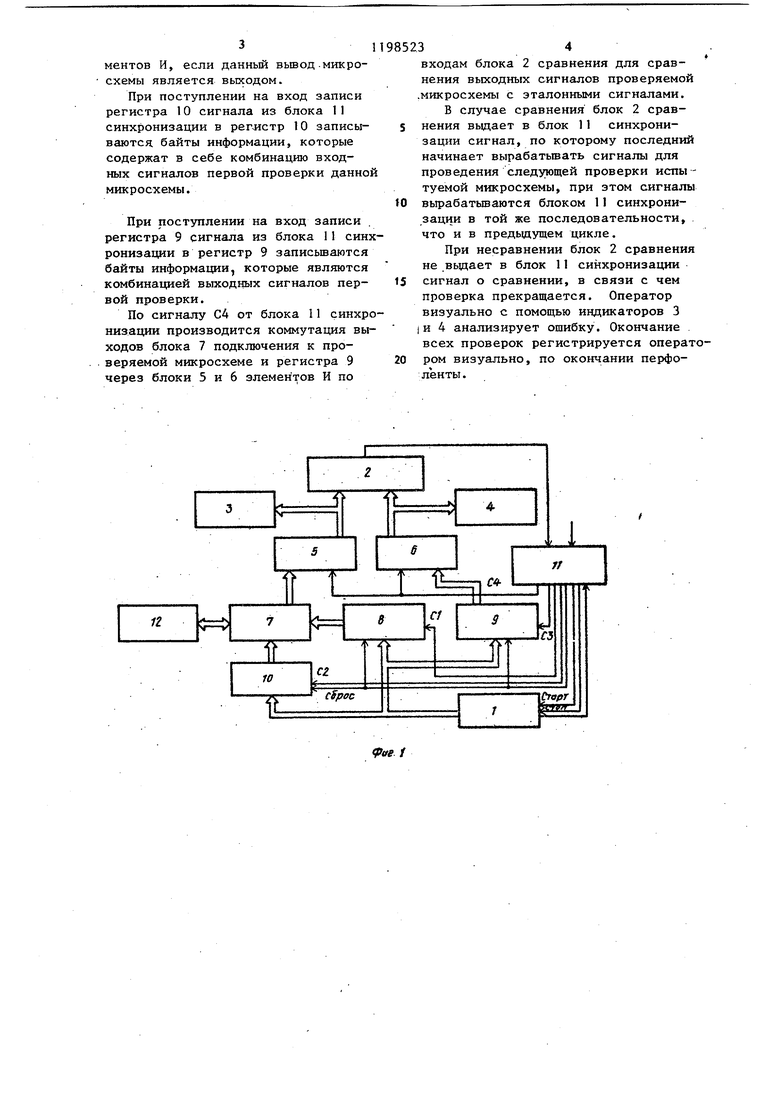

которых соединены с входами второго элемента ИЛИ, выход которого соединен с входом второго элемента .задерж ки, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого соединен с единичным входом второго триггера, прямой выход которого соед нен с входом второго усилителя, вход синхронизации счетчика соединен с выходом пятого одновибратора, вход которого объединен с входом третьего усилителя и подключен к инверсному выходу триггера, нулевой вход которого является входом синхросигнала блока синхронизации, выходы первого, второго и третьего усилите113 лей являются соответственно выходами Сброс, Старт и Стоп блока синхронизации, с первого по десятый выходы дешифратора соединены соответственно с входами с шестого по i пятнадцатый одновибраторов, выходы которых являются выходами записи блока синхронизации, одиннадцать выход дешифратора соединен с входом элемента НЕ и с входом третьего элемента задержки, выход которого является выходом разрешения сравнения блока синхронизации, выход элемента НЕ и выход первого элемента задержки соединены соответственно с вторыми входами элемента И и третьего элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1984 |

|

SU1216776A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1376092A1 |

| Устройство для сопряжения вычислительной машины с внешними абонентами | 1984 |

|

SU1265784A1 |

| Устройство для контроля перфоратора | 1986 |

|

SU1410072A1 |

| Устройство для программного управления | 1984 |

|

SU1198461A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для программного управления | 1987 |

|

SU1418652A1 |

| Устройство для адресации памяти микро-ЭВМ | 1980 |

|

SU991427A1 |

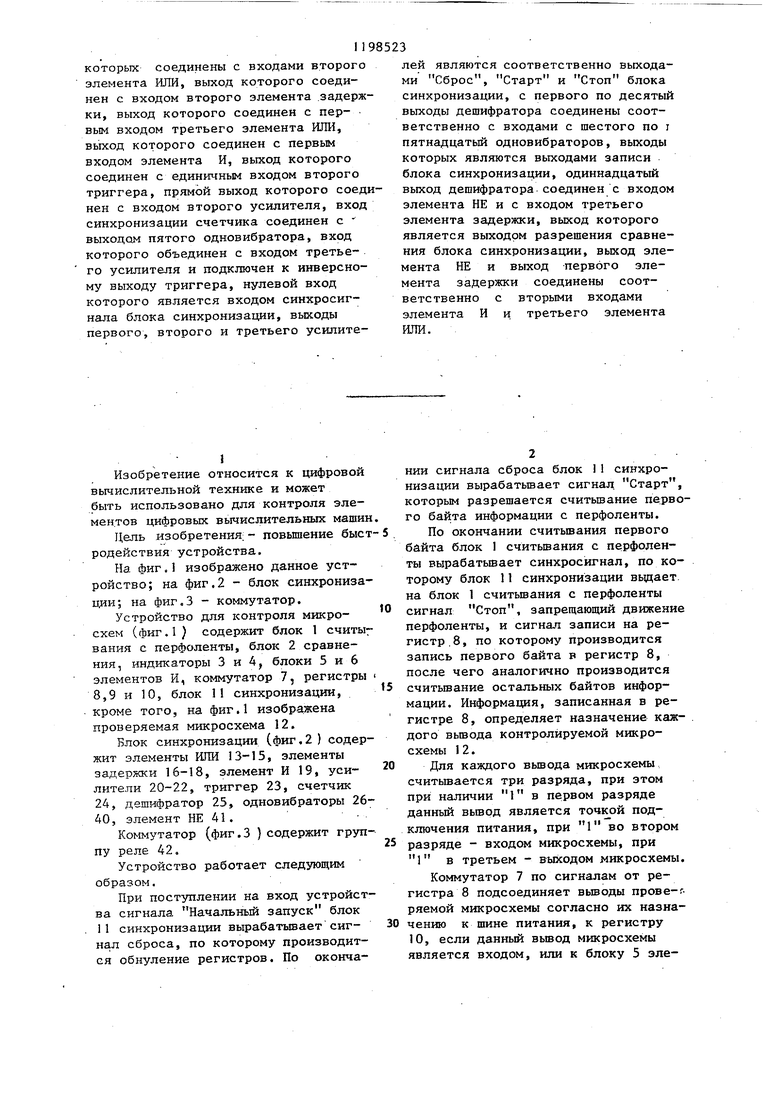

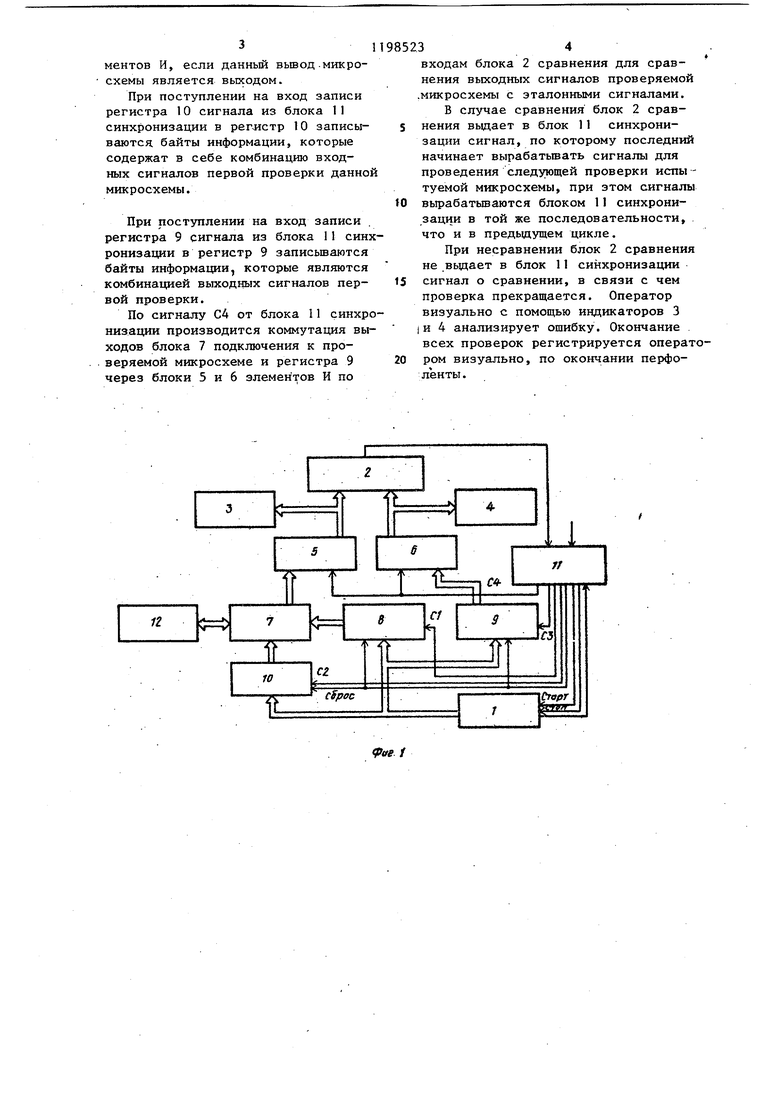

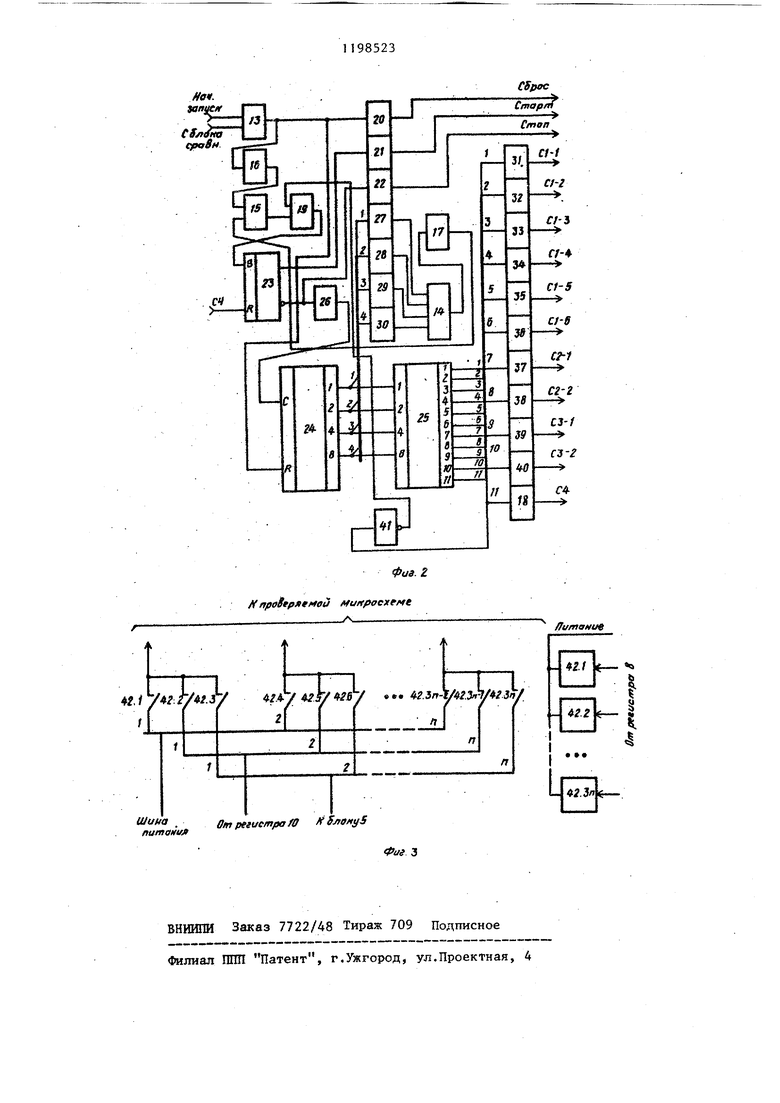

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля элементов цифровых вычислительных маши Цель изобретения; - повьш1ение быс родействия устройства. На фиг.1 изображено данное устройство; на фиг.2 - блок синхрониза ции; на фиг.З - коммутатор. Устройство для контроля микросхем (фиг.1) содержит блок 1 считы вания с перфоленты, блок 2 сравнения, индикаторы 3 и 4, блоки 5 и 6 элементов И, коммутатор 7, регистры 8,9 и 10, блок 11 синхронизации, кроме того, на фиг.1 изображена проверяемая микросхема 12. Блок синхронизации (фиг,2 ) содер жит элементы ИЛИ 13-15, элементы задержки 16-18, элемент И 19, усилители 20-22, триггер 23, счетчик 24, дешифратор 25, одновибраторы 26 40, элемент НЕ 41. Коммутатор (фиг.З ) содержит груп пу реле 42, Устройство работает следующим образом. При поступлении на вход устройст ва сигнала Начальный запуск блок 11 синхронизации вырабатывает сигнал сброса, по которому производится обнуление регистров. По окончаНИИ сигнала сброса блок 11 синхронизации вырабатьшает сигнал, Старт, которым разрешается считьшание пе:рвого байта информации с перфоленты. По окончании считьшания первого байта блок 1 считьшания с перфоленты вырабатывает синхросигнал, по которому блок 11 синхронизации вьщает. на блок 1 считьшания с перфоленты сигнал Стоп, запрещающий движение перфоленты, и сигнал записи на регистр. 8, по которому производится запись первого байта в регистр 8, после чего аналогично производится считывание остальных байтов информации. Информация, записанная в регистре 8, определяет назначение каждого вьтода контролируемой микросхемы 1 2. Для каждого вьшода микросхемы считьшается три разряда, при этом при наличии 1 в первом разряде данный вьшрд является точкой подключения питания, при 1 во втором разряде - входом микросхемы, при в третьем - выходом микросхемы. Коммутатор 7 по сигналам от регистра 8 подсоединяет вьшоды прозе-г. ряемой микросхемы согласно их назначению к шине питания, к регистру 10, если данный вьюод микросхемы является входом, или к блоку 5 эле31

ментов И, если данньй вьшод.микросхемы является выходом.

При поступлении на вход записи регистра 10 сигнала из блока 11 синхронизации в регистр 10 записываются, байты информации, которые содержат в себе комбинацию входных сигналов первой проверки данной микросхемы.

При поступлении на вход записи регистра 9 сигнала из блока 11 синхронизации в регистр 9 записьшаются байты информации, которые являются комбинацией выходных сигналов первой проверки.

По сигналу С4 от блока 11 синхронизации производится коммутация выходов блока 7 подключения к проверяемой микросхеме и регистра 9 через блоки 5 и 6 элементов И по

985234

входам блока 2 сравнения для сравнения выходных сигналов проверяемой .микросхемы с эталонными сигналами. В случае сравнения блок 2 сравнения выдает в блок 11 синхронизации сигнал, по которому последний начинает вырабатьшать сигналы для проведения следующей проверки испытуемой микросхемы, при этом сигналы to вырабатываются блоком 11 синхронизации в той же последовательности, . что и в предьщущем цикле.

При несравнении блок 2 сравнения не .вьщает в блок 11 синхронизации 15 сигнал о сравнении, в связи с чем проверка прекращается. Оператор визуально с помощью индикаторов 3 i и 4 анализирует ошибку. Окончание всех проверок регистрируется оператором визуально, по окончании перфоленты .

К npeitf n aa AfuftftoexfHe

Шина

От регистра /О SjtOMi/S питомил

Авторы

Даты

1985-12-15—Публикация

1984-06-14—Подача