вертым. управляющим входом - с выхо дом второго блока сравнения и счетным входом второго счетчика

198461

импульсов, подключенного выходом к второму информационному входу первого блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1987 |

|

SU1418652A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения электронно-вычислительной машины с накопителями на магнитных носителях | 1983 |

|

SU1156082A1 |

УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее пульт, связанный выходом с управляющим входом блока ввода информа1Ц1и и первыми управляющими входами коммутатора, блока задания режима и блока синхронизации, подключенного первым информационным входом к управляющему входу устройства, дешифратор, связанный с информационным входом блока ввода информации, вторым информационным входом блока синхронизации, информационным входом блока задания режима и первь1м информационным .входом первого регистра, а также три блока сравнения, подключенных выходами соответственно к второму, третьему и четвертому управляющим блока задания режима, отличающееся тем, что, с целью повышения производительности устройства, в него введены второй регистр, элемент И, два счетчика импульсов и блок памяти, подключенный информационным входом к информационному выходу блока ввода информации, адресным входом - к выходу первого счетчика импульсов и первому информационному входу второго регистра, первым управляющим входом - к выходу коммутатора и первому управляющему входу первого счетчика, BTopbiM управляющим входом - выходу пульта, а выходом - к входу дешифратора и второму информационному входу первого регистра, соединенного управляющим входом с управляющими входами второго счетчика и второго регистра, первым выходом блока хронизации, пятым управляющим входом (Л блока задания режима и вторыми управляющими входами коммутатора и первого счетчика. Подключенного информационным входом к первым информационным входам трех блоков сравнения . и выходу второго регистра, соединен ного вторым информационным входом (;О с вторыми информационными входами второго и третьего блоков сравнения 00 с информационной шиной устройства и ВЫХОДОМ первого регистра, связанноо: го первым информационным входом с первым входом элемента И, подключенного вторым входом к выходу блока задания режима и второму управляющему входу блока синхрйнизации, а выходом - к разрещающим входам трех блоков сравнения, причем синхровыход блока ввода информации подключен к информационному входу коммутатора, выход первого блока сравнения подключен к третьему управляющему входу блока синхронизации, связанного вторым выходом с управляющим выходом устройства, а чет

гЛ

, Изобретение относится к автоматике и вычислительной технике и может быть использовано для программного управления технологическим оборудованием, например сверлильньми станками, автоматами укладки радиокомпонентов на печатные платы, станками ,для прошивки постоянных запоминающих устройств.

Цель изобретения - повышение производительности работы устройства.

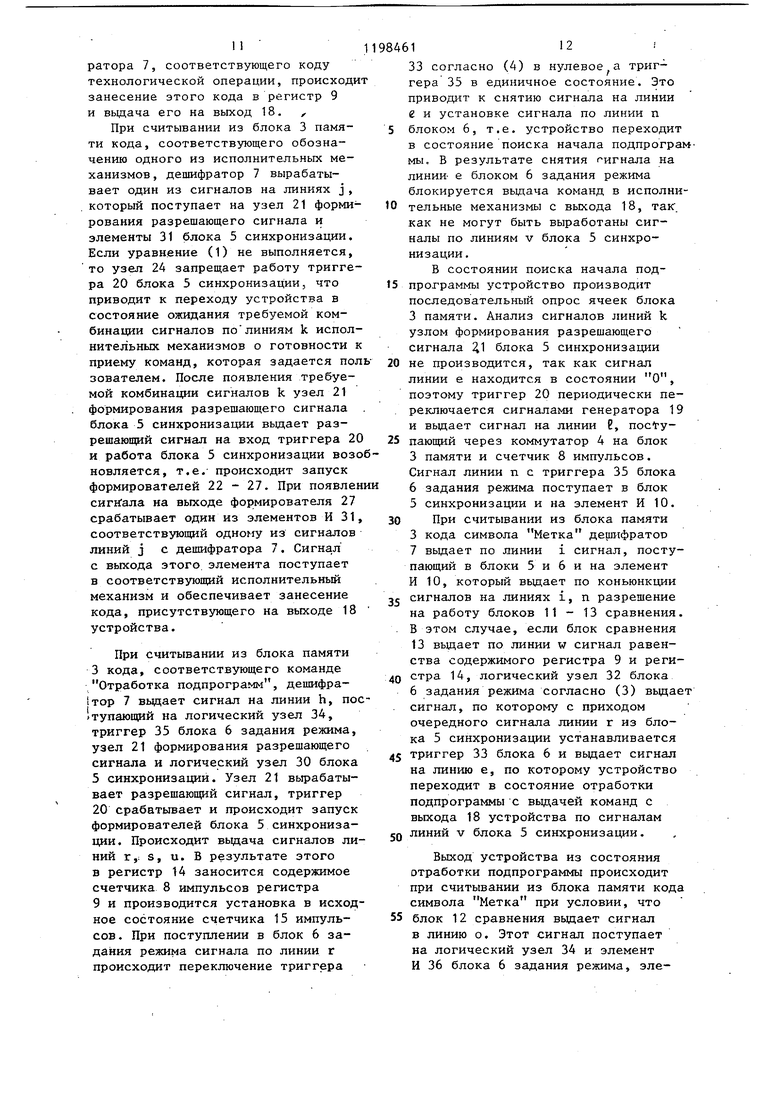

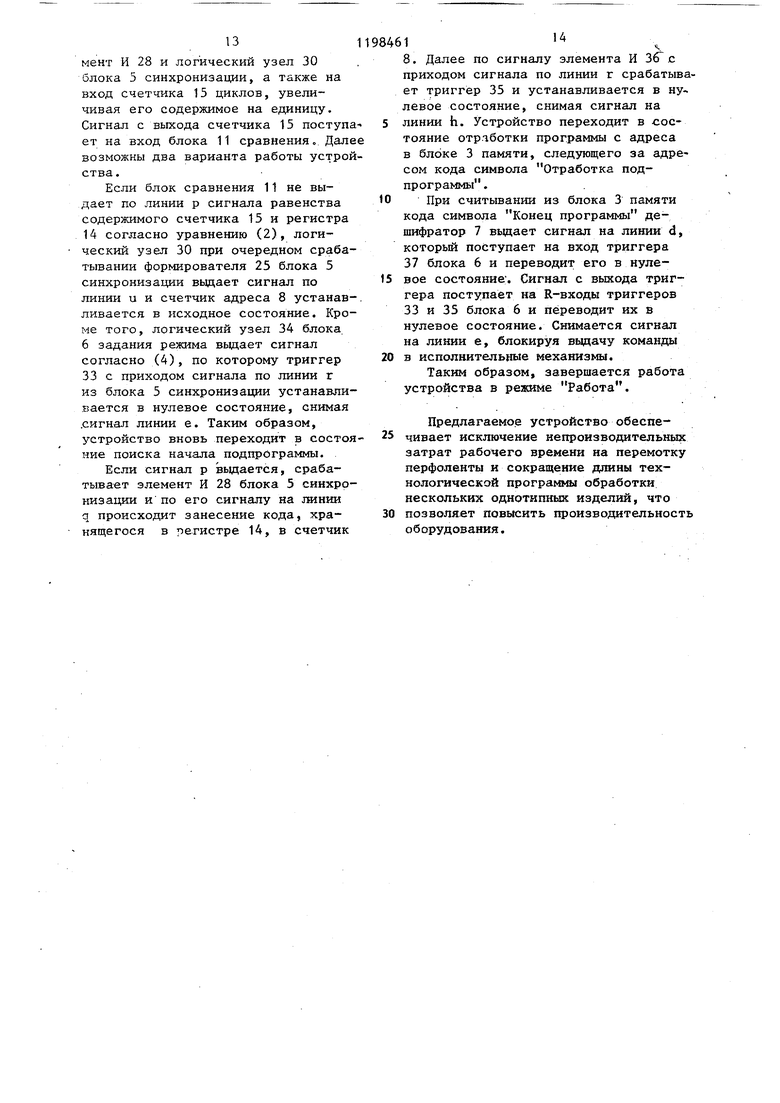

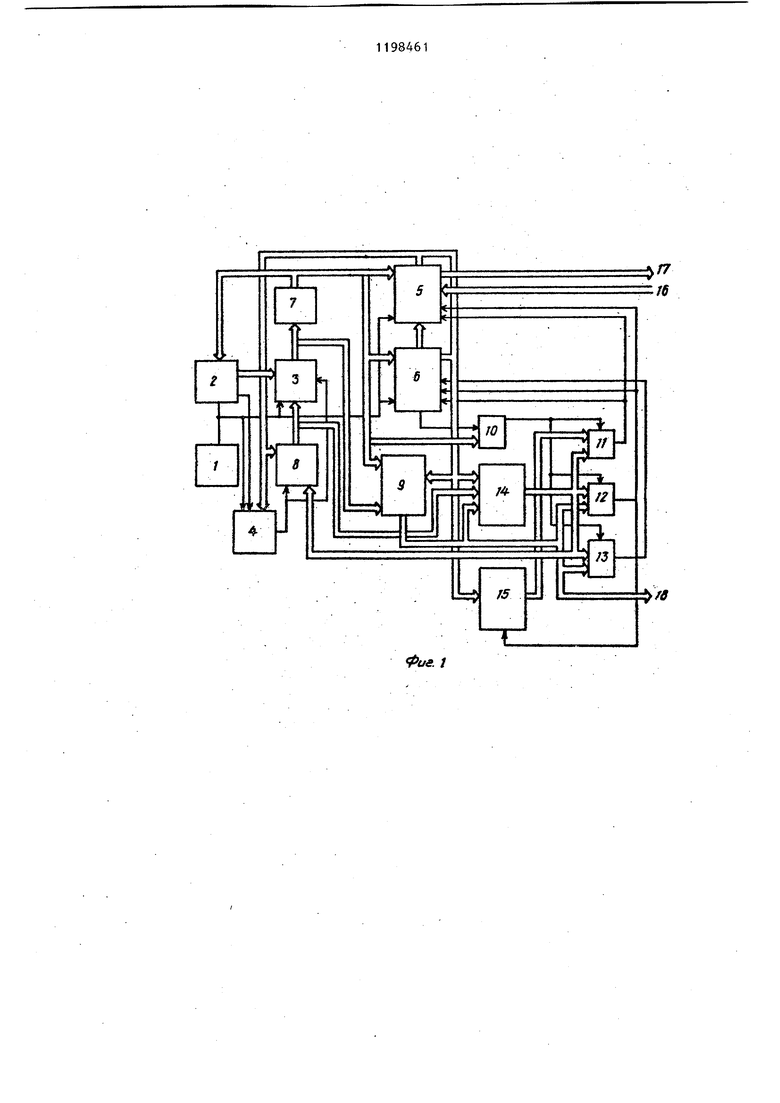

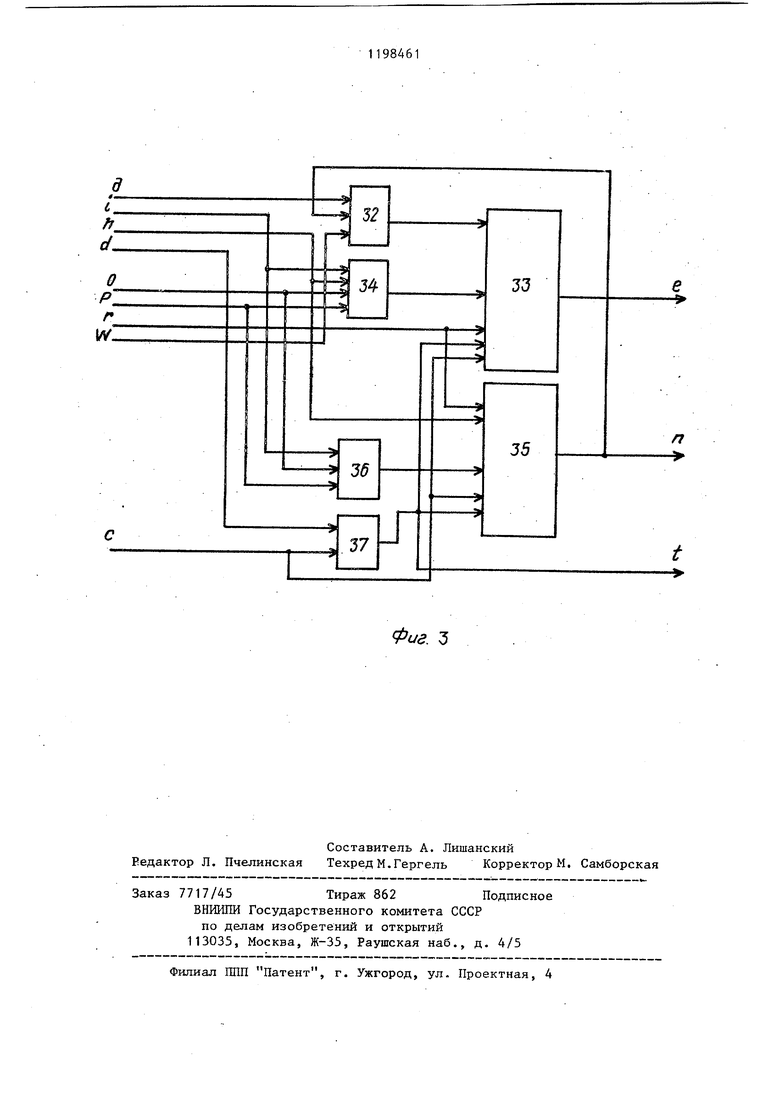

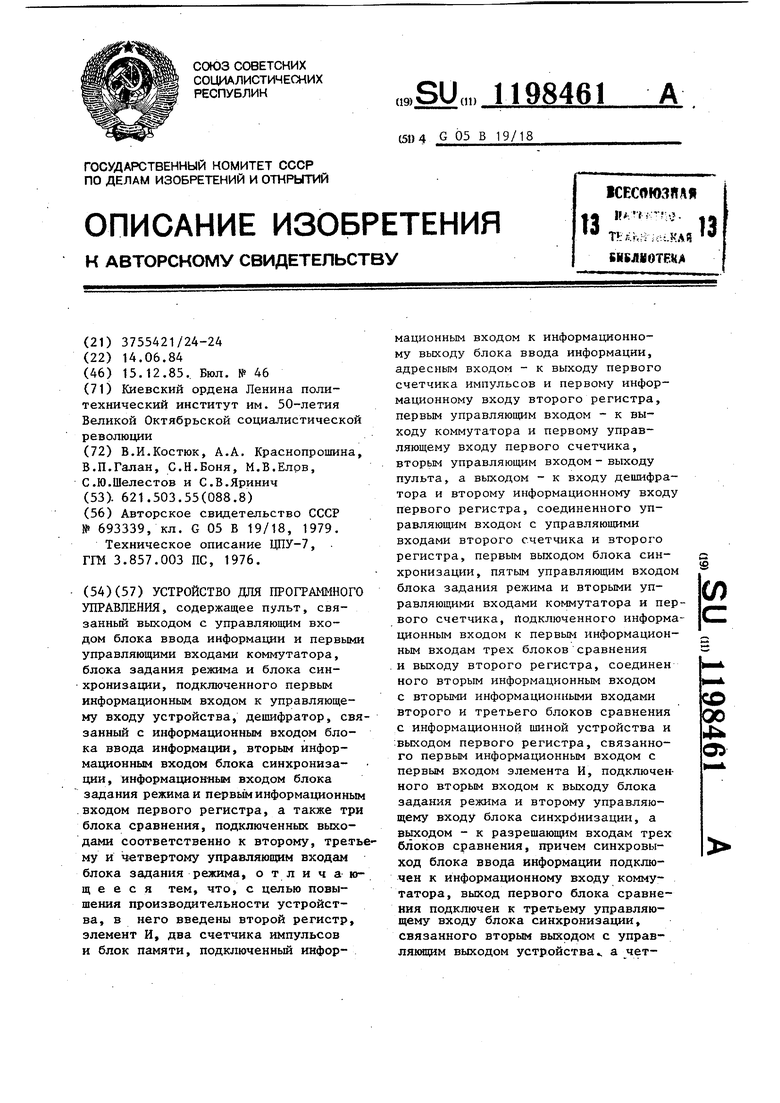

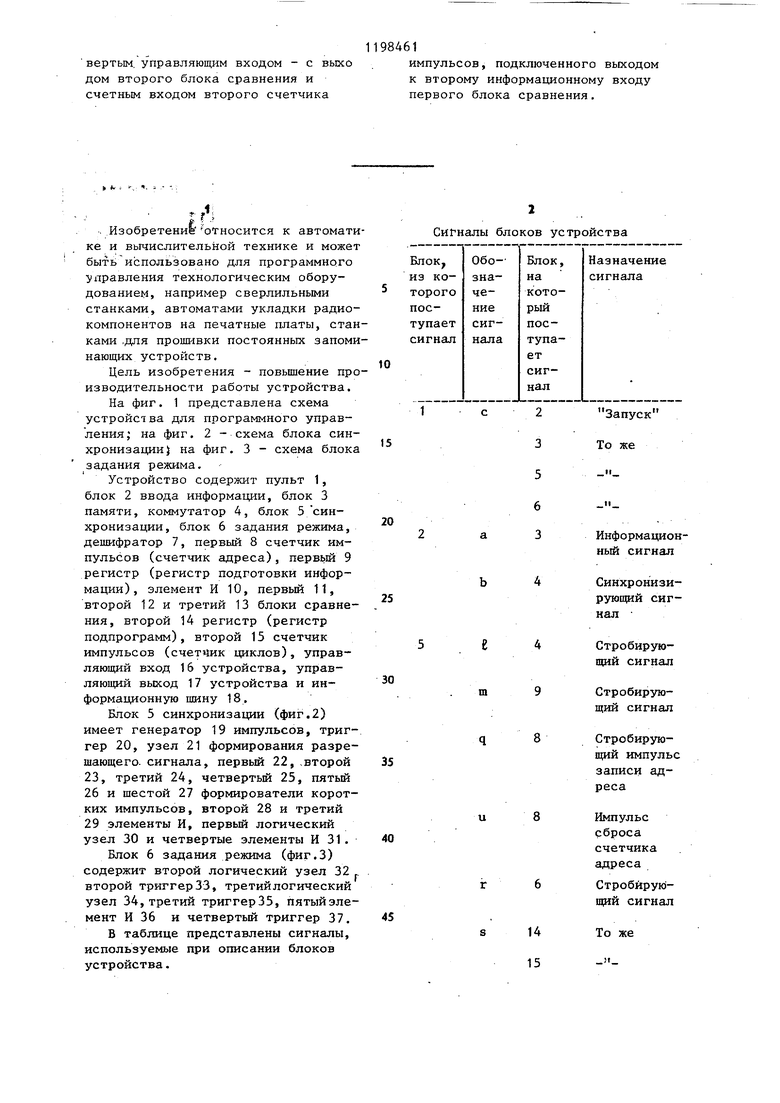

На фиг. 1 представлена схема устройства для программного управления; на фиг. 2 - схема блока синхронизации} на фиг. 3 - схема блока задания режима.

Устройство содержит пульт 1, блок 2 ввода информации, блок 3 памяти, коммутатор 4, блок 5 синхронизации, блок 6 задания режима, дешифратор 7, первый 8 счетчик импульсов (счетчик адреса), первьй 9 регистр (регистр подготовки информации), элемент И 10, первый 11, второй 12 и третий 13 блоки сравнения, второй 14 регистр (регистр подпрограмм), второй 15 счетчик импульсов (счетчик циклов), управляющий вход 16 устройства, управляющий выход 17 устройства и информационную шину 18.

Блок 5 синхронизации (фиг.2) имеет генератор 19 импульсов, триггер 20, узел 21 формирования разрешающего, сигнала, первый 22,,второй 23, третий 24, четвертьй 25, пятый 26 и шестой 27 формирователи коротких импульсов, второй 28 и третий 29 элементы И, первый логический узел 30 и четвертые элементы И 31.

Блок 6 задания режима (фиг.З) содержит второй логический узел 32 второй триггер 33, третийлогический узел 34,третий триггер35, пятыйэлемент И 36 и четвертый триггер 37.

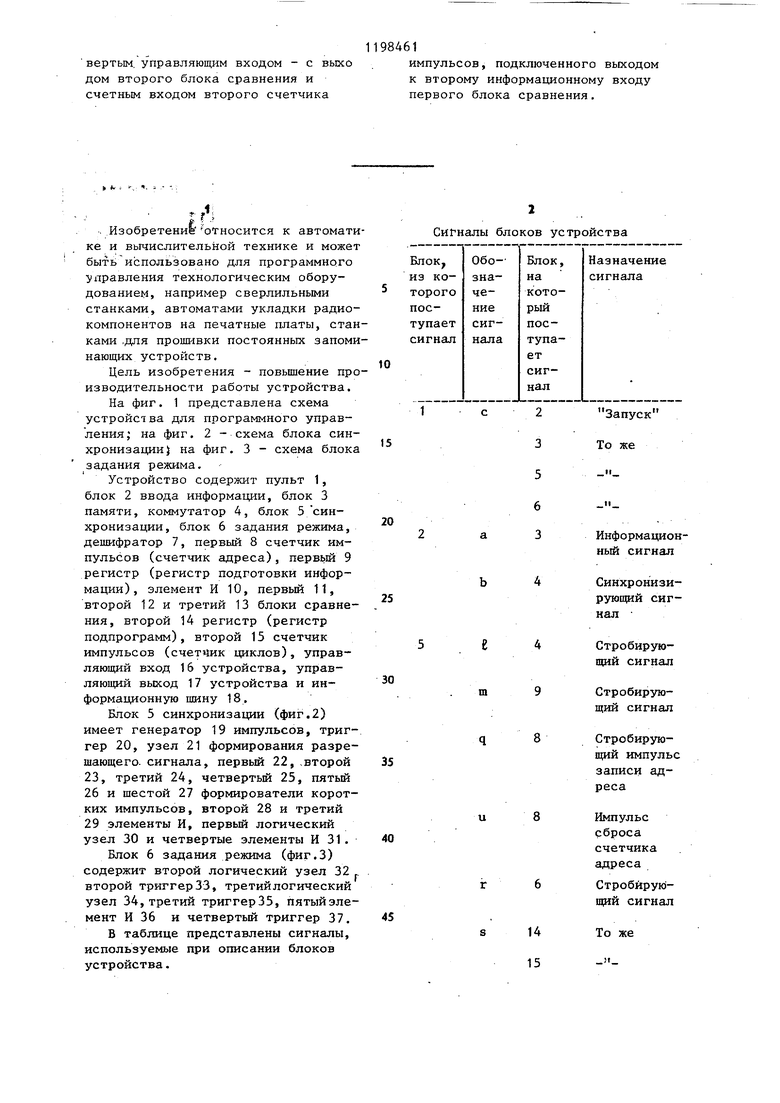

В таблице представлены сигналы, используемые при описании блоков устройства.

Сигналы блоков устройства

Запуск

3 5 6 3 То же

11

Информационный сигнал

Синхронизирующий сигнал

Стробируюпщй сигнал

Стробирующий сигнал

Стробирующий импульс записи адреса

Импульс сброса счетчика адреса

Стробйрующий сигнал

14

То же

)t

15

31198461

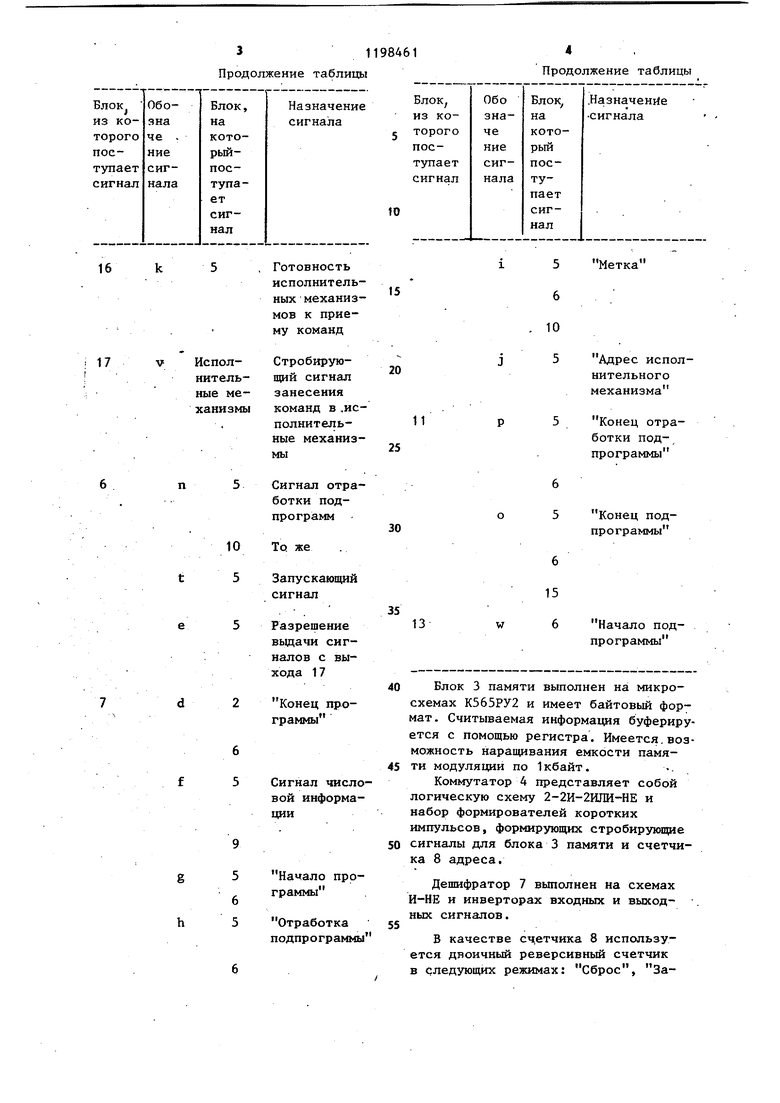

Продолжение таблицы

Готовность

6 исполнительных механизмов к приему команд

СтробируюИспол7

V щий сигнал нительзанесенияные мекоманд в,исханизмыполнительные механизмы

Сигнал отрапботки подпрограмм

10 5

То же

Запускающий сигнал

Разрешение выдачи сигналов с выхода 17

Конец программы

6 5

Сигнал числовой информации

Начало программы

Отработка подпрограммы

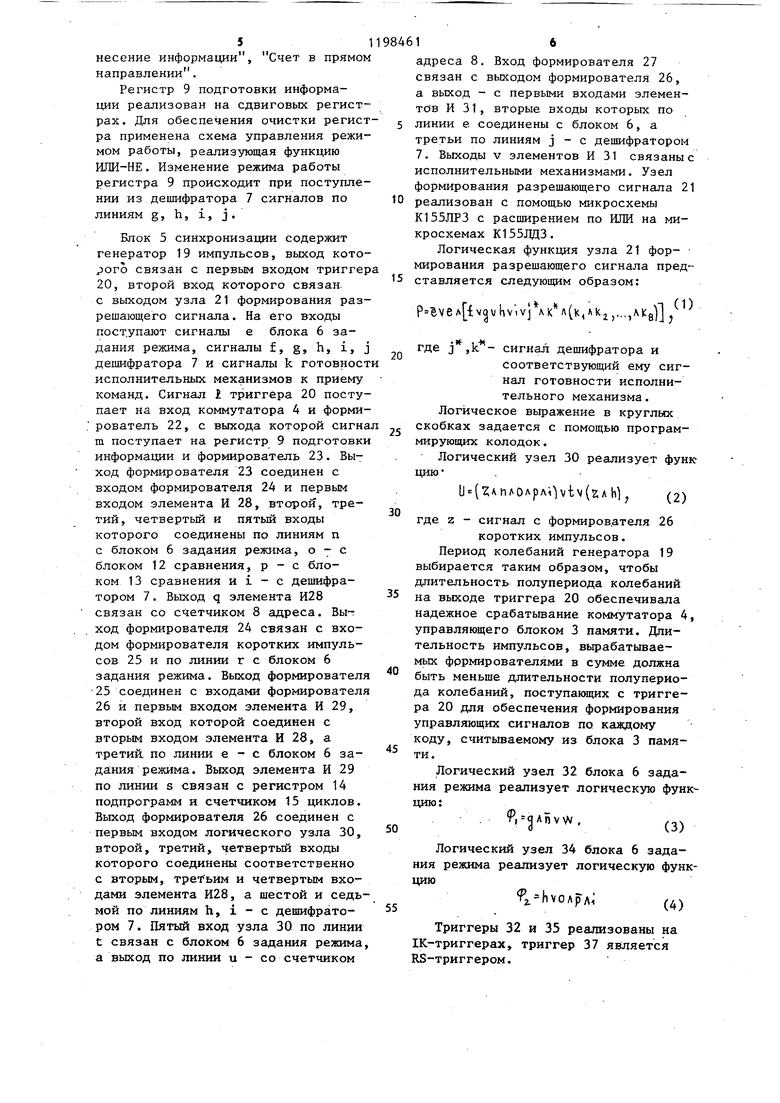

Продолжение таблицы

Метка

5

6

10

Адрес испол5нительного механизма

Конец отра1ботки подпрограммы

6

Конец под5программы

6

15

Начало под6

3

W программы

Блок 3 памяти выполнен на микросхемах К565РУ2 и имеет байтовый формат. Считываемая информация буферируется с помощью регистра. Имеется.возможность наращивания емкости памяти модуляции по 1кбайт.

Коммутатор 4 представляет собой логическую схему 2-2И-2ШШ-НЕ и набор формирователей коротких импульсов, формирующих стробирующие

сигналы для блока 3 памяти и счетчика 8 адреса.

Дешифратор 7 выполнен на схемах И-НЕ и инверторах входных и выходных сигналов.

В качестве сч.етчика 8 используется двоичный реверсивный счетчик в следующих режимах: Сброс, Занесение информации, Счет в прямо направлении. Регистр 9 подготовки информации реализован на сдвиговых регист рах. Для обеспечения очистки регис ра применена схема управления режи мом работы, реализующая функцию ИЛИ-НЕ. Изменение режима работы регистра 9 происходит при поступле нии из дешифратора 7 сигналов по линиям g, h, i, j. Блок 5 синхронизации содержит генератор 19 импульсов, выход кото рого связан с первым входом тригге 20, второй вход которого связан с выходом узла 21 формирования раз решающего сигнала. На его входы поступают сигналы е блока 6 задания режима, сигналы f, g, h, i, дешифратора 7 и сигналы k готовнос исполнительных механизмов к приему команд. Сигнал i триггера 20 посту пает на вход коммутатора 4 и форми рователь 22, с выхода которой сигн m поступает на регистр 9 подготовк информации и формирователь 23. Выход формирователя 23 соединен с входом формирователя 24 и первым входом элемента И 28, второй, третий, четвертый и пятый входы которого соединены по линиям п с блоком 6 задания режима, о - с блоком 12 сравнения, р - с блоком 13 сравнения и i - с дешифратором 7. Выход q элемента И28 связан со счетчиком 8 адреса. Выт ход формирователя 24 связан с входом формирователя коротких импульсов 25 и по линии г с блоком 6 задания режима. Вькод формировател 25соединен с входами формировател 26и первым входом элемента И 29, второй вход которой соединен с BTopbtM входом элемента И 28, а третий, по линии е - с блоком 6 задания режима. Выход элемента И 29 по линии S связан с регистром 14 подпрограмм и счетчиком 15 циклов. Выход формирователя 26 соединен с первьм входом логического узла 30, второй, третий, четвертый входы которого соединены соответственно с вторым, третьим и четвертым входами элемента И28, а шестой и седь мой по линиям h, i - с дешифратором 7. Пятый вход узла 30 по линии t связан с блоком 6 задания режима а выход по линии и - со счетчиком адреса 8. Вход формирователя 27 связан с выходом формирователя 26, а выход - с первыми входами элементов И 31, вторые входы которых по линии е соединены с блоком 6, а третьи по линиям j - с дешифратором 7. Выходы V элементов И 31 связаны с исполнительными механизмами. Узел формирования разрешающего сигнала 21 реализован с помощью микросхемы К155ЛРЗ с расширением по ИЛИ на микросхемах К155ЛДЗ. Логическая функция узла 21 формирования разрешающего сигнала представляется следующим образом: P BveA lv uhviVj A|((K,Ak.jj...,) . где j , сигнал дешифратора и соответствующий ему сигнал готовности исполнительного механизма. Логическое выражение в круглых скобках задается с помощью программирующих колодок. Логический узел 30 реализует функциюU (nAOApAi1vtv(2;Ah)j (2) где Z - сигнал с формирователя 26 коротких импульсов. Период колебаний генератора 19 выбирается таким образом, чтобы длительность полупериода колебаний на выходе триггера 20 обеспечивала надежное срабатьшание коммутатора 4, управляющего блоком 3 памяти. Длительность импульсов, вьфабатываемых Формирователями в сумме должна быть меньше длительности полупериода колебаний, поступакндих с триггера 20 для обеспечения формирования управляющих сигналов по каждому коду, считьшаемому из блока 3 памяти. Логический узел 32 блока 6 задания режима реализует логическую функцию:«P.AnvW.(3) Логический узел 34 блока 6 задания режима реализует логическую функциюР2. Ьуолрл; (4) триггеры 32 и 35 реализованы на 1К-триггерах, триггер 37 является RS-триггером.

7

Функционирование блока 5 синхронизации происходит следующим образом

После подачи сигнала по линии t на выходе логического узла 30 форми руется сигнал и, вызывающий установку счетчика 8 адреса в исходное состояние, С входа е на узел 21 формирования разрешающегося сигнала поступает сигнал и согласно вьфажению (1) происходит формирование сигнала р, поступающего на вход триггера 20, разрешая его работу. Триггер 20 производит деление частоты генератора 19 импульсов. По высокому уровню сигнала линии Е производится считывание информации из блока 3 памяти, по низкому уровню происходит последовательньй запуск формирователей и выдаются сигналы т, г.

При считьшании из блока памяти кода символа Начало программы после формирования снимается сигнал е и в дальнейшем сигнал р выдается только при наличии сигналов с дешифратора 7 и истинности выражения (1) .

При считьтании из блока 3 памяти кода исполнительного механизма блокируется работа триггера 20 в случае отсутствия сигналов готовности исполнительных механизмов согласно (1) и тем cat-ibiM прекращается считывание информации из блока-3 памяти После восстановления сигналов готовности узел 21 формирования разрешающего сигнала формирует сигнал р, а на выходе одного из элементов И 31 соответствующего сигналу дешифратора 7, формируется сигнал v.

При считывании из блока 3 памяти кода Отработка подпрограммы после формирования сигнала г в блок 5 синхронизации поступает сигнал п, который поступает на вход элемента И 29, на выходе которого при появлений на втором входе сигнала формирователя 25 формируется сигнал 3. Сигнал h поступает на вход логического узла 30, и при поступлении сигнала с формирователя 26 на выходе логического узла 30 формируется сигнал U согласно (2).

При наличии сигналов п, i в зависимости от состояния сигналов о, р формируется сигнал q на вькоде элемента И 28 либо сигнал и на выходе логического узла 30.

Блок функционирует следуницим образом.

84618

При поступлении сигнала С с пульта 1 триггер 37 устанавливается в единичное состояние, инициируя с помощью сигнала на линии t установку счетчика 8 в исходное состояние. По окончании ввода технологической программы по сигналу дешифратора. 7 на линии d производится установка триггера 37 в исходное состояние. В режиме Работа сигналом с с пульта 1 управления устанавливается триггер 37 и вновь производится установка счетчика 8 в исходное ;состояние. Наличие на входах триггег

15 ров 33 и 35 сигналов, поступающих с пульта 1 и триггера 37 в этом режиме разрешает их работу.

При считывании из блока 3 памяти кода Начало программы на первом входе логического узла 32 по является сигнал g дешифратора 7 и с приходом сигнала г на второй вход триггера 32 происходит его установка в единичное состояние. На

25 линии е формируется активньм уровень сигнала.

При считывании из блока 3 памяти кода Отработка программы на первом входе логического узла 34 и втором входе триггера 35 появляется сигнал h с дешифратора 7 и с приходом сигнала г триггер 33 устанавливается в О (снимается сигнал е) а триггер 25 - в 1, т.е. вырабатывается сигнал на линии п.

При этом согласно (3) запрещается срабатывание логического узла 32 по сигналу g с дешифратора 7 н.а время отработки подпрограммы.

При поступлении сигнала w от блока 13 сравнения с приходом сигнала

г триггер 33 устанавливается в 1, вырабатывая сигнал е. При поступлении сигнала линии i с дешифратора 7 переключаются триггеры 33 и 35 в зависимости от состояния сигналов на линиях о, р блоков 12 и 11 сравнения. При этом триггер 3 устанавливается в О согласно (4), а триггер 35 - в О при условии появления на выходе элемента И 36 сигнала 1.

Устройство работает следующим

образом.

Устройство работает в двух режимах: Запись и Работа, которые задаются оператором с пульта I.

В режиме Запись производится перезапись программы с перфоленты с помощью блока 2 ввода информации

9

в блок 3 памяти. С пульта 1 на управляющие входы блока 2 ввода информации, коммутатора 4, блока 3 памяти, блока 5 синхронизации, блока 6 задания режима поступает сигнал. По этому сигналу в блоке 3 памяти устанавливается режим записи информации, коммутатор 4 подключает к своему выходу синхронизирующий вьпсод блока 2 ввода информации, срабатывает триггер 37 блока 6 задания режима и вьфабатывает сигнал,поступающий в блок 5 синхронизации. Блок 5 синхронизации согласно уравнению (3) формирует на линии U сигнал,который поступает на счетчик 8 адреса и устанавливает его в исходное положение. После выработки сигналов на линиях t, и работа блоков 5 и 6 в режиме Запись прекращается, так как сигнал на линии С с пульта 1 запрещает переключение триггеров 35 и 36 и бл ка 6 задания режима. При этом не могут быть выработаны сигналы по линиям п, е блоком 6 задания режима, а блок 5 синхронизации вырабатывать только сигналы на линиях

г, которые не могут измега,

нить состояние устройства. Одновременно в блоке 2 ввода информации по сигналу линии С пульта 1 происходит включение фотосчитывающего устройства (не показано). Начинается движение перфоленты и происходит считывание информации, которая поступает на информационный вход блока 3 памяти. Сигналы с синхронизирующего выхода блока 2 ввода информации, являющиеся сигналами синхродорожки перфоленты, чере коммутатор 4 поступают на входы управления блока 3 памяти и счетчика 8 и вызывают запись на них единицы, т.е. задается номер следующей ячейки блока памяти, в которую запишется очередная команда программы

На выходе блока памяти присутствует очередная записанная информация. Поэтому при записи в символа Конец программы дешифратор 7 по линии d вьщает сигнал, который поступает на входы блока 2 ввода информации и блока 6 задания режима, завершая работу устройства в режиме Запись.

В режиме Работа сигнал линии С пульта 1 запрещает работу блока

9846110

2 ввода информации и задает в бло- . ке памяти режим считывания. В блоке 6 задания режима сигнал линии С устанавливает триггер 37 в единич5 но состояние и разблокирует триггеры 33 и 35. Сигнал по линии t блока 6 задания режима поступает в блок 5 синхронизации, который вырабатывает сигнал на линии и согласно

10 уравнению (3) для установки счетчика 8 в исходное состояние. Одновременно сигнал с пульта 1 переключает коммутатор 4 на работу по сигналам линии блока 5 синхрониза15 Ции.

В соответствии с уравнением (1) узел 2 формирования разрешающего сигнала блока 5 синхронизации при равенстве О сигнгша на линии С

20 блока 6 задания режима разрешает работу триггера 20 блока 5 синхронизации. Блок 5 вырабатывают сигналы , поступающие через коммутатор 4 на блок 3 памяти и счетчик 8 адреса.

25 Происходит последовательное считьшание информации из блока памяти и увеличение содержимого счетчика адреса 8 на единицу. Кроме того, вырабатываются сигналы линий т, г, поступающие на регистр 9 и блок 6 задания режима соответственно.

Считываемая из блока 3 памяти информация поступает на вход дешифратора 7. При считьшании информации, соответствующей коду Начало программы , дешифратор 7 вьщает сигнал на линии g на блок 6 задания режима. Логический узел 32 согласно уравнению (3) вырабатывает сигнал 1, и по приходу очередного сигнала линии г блока 5 синхронизации триггер 33 блока 6 задания режима устанавливается в единичное состояние и тем самым вырабатывается сигнал линии е, разрешающий выдачу в дальнейшем сигналов линии v блоком 5 синхронизации на управляемые устройством исполнительные механизмы. Этот же сигнал лереключает узел 21 формирования разрешающего сигнала на работу по сигналам линий k исполнительных механизмов о готовности к приему команд и сигналам линий f, g, h, i, j поступаюшр;1м из депшфратора 7 в соответствии с уравнением (t).

При совпадении на входах регистра 9 сигнала линии m с блока 5 синхронизации и сигнала линии f с дешиф11ратора 7, соответствующего коду технологической операции, происходи занесение этого кода в регистр 9 и выдача его на выход 18. , При считывании из блока 3 памяти кода, соответствующего обозначению одного из исполнительных механизмов , дешифратор 7 вырабатывает один из сигналов на линиях j, который поступает на узел 21 формирования разрешающего сигнала и элементы 31 блока 5 синхронизации. Если уравнение (1) не выполняется, то узел 24 запрещает работу тригге ра 20 блока 5 синхронизации 5 что приводит к переходу устройства в состояние ожидания требуемой комбинации сигналов полиниям k испол нительных механизмов о готовности приему команд, которая задается пол зователем. После появления треб уемой комбинации сигналов k узел 21 формирования разрешающего сигнала блока 5 синхронизации вьщает разрешающий сигнал на вход триггера 2 и работа блока 5 синхронизации воз новляется, т.е. происходит запуск формирователей 22 - 27, При появле сигнала на выходе формирователя 27 срабатывает один из элементов И 31 соответствующий одному из сигналов линий j с дешифратора 7. Сигнал с выхода этого, элемента поступает в соответствующий исполнительный механизм и обеспечивает занесение кода, присутствующего на выходе 18 устройства. При считывании из блока памяти 3 кода, соответствующего команде Отработка подпрограмм, дешифра1тор 7 выдает сигнал на линии h, по тупающий на логический узел 34, триггер 35 блока 6 задания режима, узел 21 формирования разрешающего сигнала и логический узел 30 блока 5 синхронизации. Узел 21 вьфабатывает разрешающий сигнал, триггер 20 срабатывает и происходит запуск формирователей блока 5 синхронизации. Происходит выдача сигналов ли ний г, S, U. В результате этого в регистр 14 заносится содержимое счетчика 8 импульсов регистра 9 и производится установка в исход ное состояние счетчика 15 импульсов , При поступлении в блок 6 задания режима сигнала по линии г происходит переключение триггера 112 33 согласно (4) в нулевое а триггера 33 в единичное состояние. Это приводит к снятию сигнала на линии е и установке сигнала по линии п блоком 6, т.е. устройство переходит в состояние поиска начала подпрограм мы. В результате снятия сигнала на линии- е блоком 6 задания режима блокируется вьщача команд в исполнительные механизмы с выхода 18, так. как не могут быть выработаны сигналы по линиям V блока 5 синхронизации. В состоянии поиска начала подпрограммы устройство производит последовательный опрос ячеек блока 3 памяти. Анализ сигналов линий k узлом формирования разрешающего сигнала 1 блока 5 синхронизации не производится, так как сигнал линии е находится в состоянии О, поэтому триггер 20 периодически переключается сигналами генератора 19 и выдает сигнал на линии Е, noctyпающий через коммутатор 4 на блок 3 памяти и счетчик 8 импульсов, Сигнал линии п с триггера 35 блока 6задания режима поступает в блок 5синхронизации и на элемент И 10. При считывании из блока памяти 3 кода символа Метка дешифратор 7выдает по линии i сигнал, поступающий в блоки 5 и 6 и на элемент И 10, который выдает по конъюнкции сигналов на линиях i, п разрешение на работу блоков 11-13 сравнения. В этом случае, если блок сравнения 13 вьщает по линии w сигнал равенства содержимого регистра 9 и регистра 14, логический узел 32 блока 6задания режима согласно (3) вьщает сигнал, по которому с приходом очередного сигнала линии г из блока 5 синхронизации устанавливается триггер 33 блока 6 и вьщает сигнал на линию е, по которому устройство переходит в состояние отработки подпрограммы с вьщачей команд с выхода 18 устройства по сигналам линий V блока 5 синхронизации, Выход устройства из состояния отработки подпрограммы происходит при считывании из блока памяти кода символа Метка при условии, что блок 12 сравнения вьщает сигнал в линию о. Этот сигнал поступает на логический узел 34 и элемент И 36 блока 6 задания режима, эле13мент И 28 и логический узел 30 блока 5 синхронизации, а также на вход счетчика 15 циклов, увеличивая его содержимое на единицу. Сигнал с выхода счетчика 15 поступа ет на вход блока 11 сравнения. Дале возможны два варианта работы устрой ства. Если блок сравнения 11 не выдает по линии р сигнала равенства содержимого счетчика 15 и регистра 14 согласно уравнению (2), логический узел 30 при очередном срабатывании формирователя 25 блока 5 синхронизации вьщает сигнал по линии U и счетчик адреса 8 устанавливается в исходное состояние. Кроме того, логический узел 34 блока. 6 задания режима вьщает сигнал согласно (4), по которому триггер 33 с приходом сигнала по линии г из блока 5 синхронизации устанавливается в нулевое состояние, снимая .сигнал линии е. Таким образом, устройство вновь переходит в состоя ние поиска начала подпрограммы. Если сигнал р выдается, срабатывает элемент И 28 блока 5 синхронизации и по его сигналу на линии q происходит занесение кода, хранящегося в регистре 14, в счетчик 1 8. Далее по сигналу злемента И 36 с приходом сигнала по линии г срабатывает триггер 35 и устанавливается в нулевое состояние, снимая сигнал на линии h. Устройство переходит в состояние отр.1ботки программы с адреса в блоке 3 памяти, следующего за адресом кода символа Отработка подпрограммы . При считывании из блока 3 памяти кода символа Конец программы дешифратор 7 вьщает сигнал на линии d, который поступает на вход триггера 37 блока 6 и переводит его в нуяевое состояние . Сигнал с выхода триггера поступает на R-входы триггеров 33 и 35 блока 6 и переводит их в нулевое состояние. Снимается сигнал на линии е, блокируя выдачу команды в исполнительные механизмы. Таким образом, завершается работа устройства в резише Работа. Предлагаемое устройство обеспечивает исключение непроизводительных затрат рабочего времени на перемотку перфоленты и сокращение длины технологической программы обработки нескольких однотипных изделий, что позволяет повысить производительность оборудования.

Фие. i

pL/e. 2

Фиг. 3

| Устройство для программного управления станком | 1977 |

|

SU693339A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-15—Публикация

1984-06-14—Подача