(Л

сх а

СП Ю

Изобретение относится к автоматике и вычислительной технике и может быть использовано для программного управления технологическим оборудова- нием, например автоматами укладки радиокомпонентов на печатные платы, автоматами сборки микросборок, станками для прошивки ПЗУ и т.д.

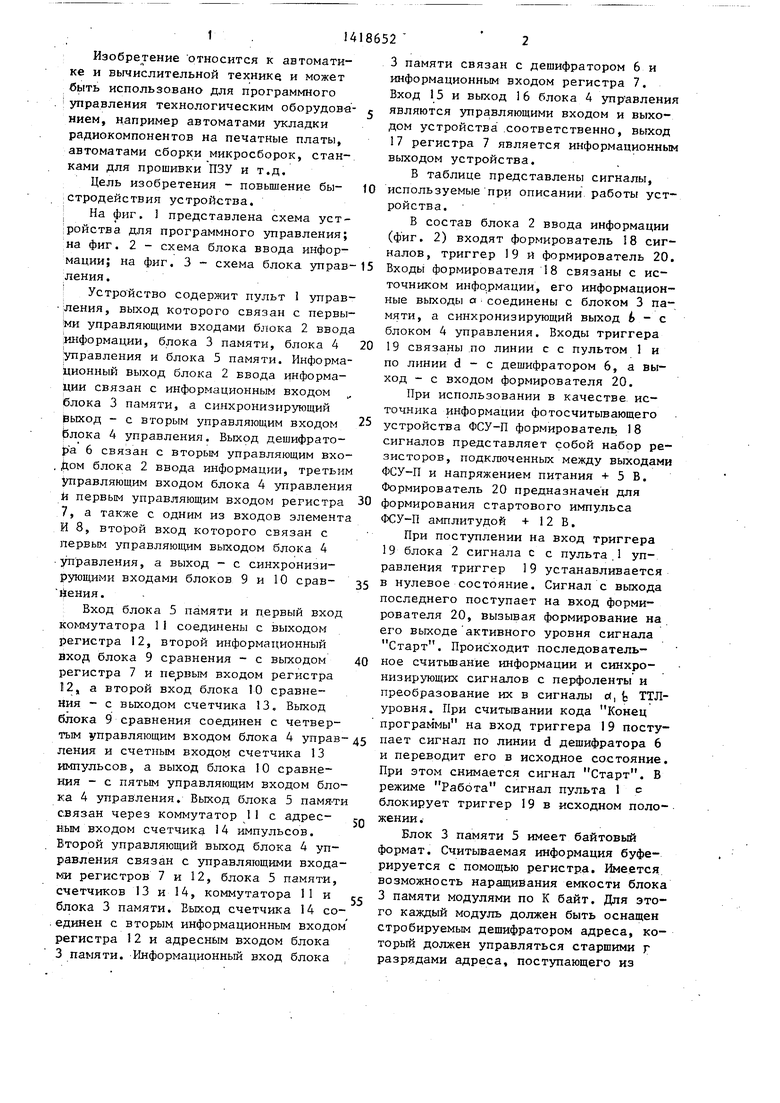

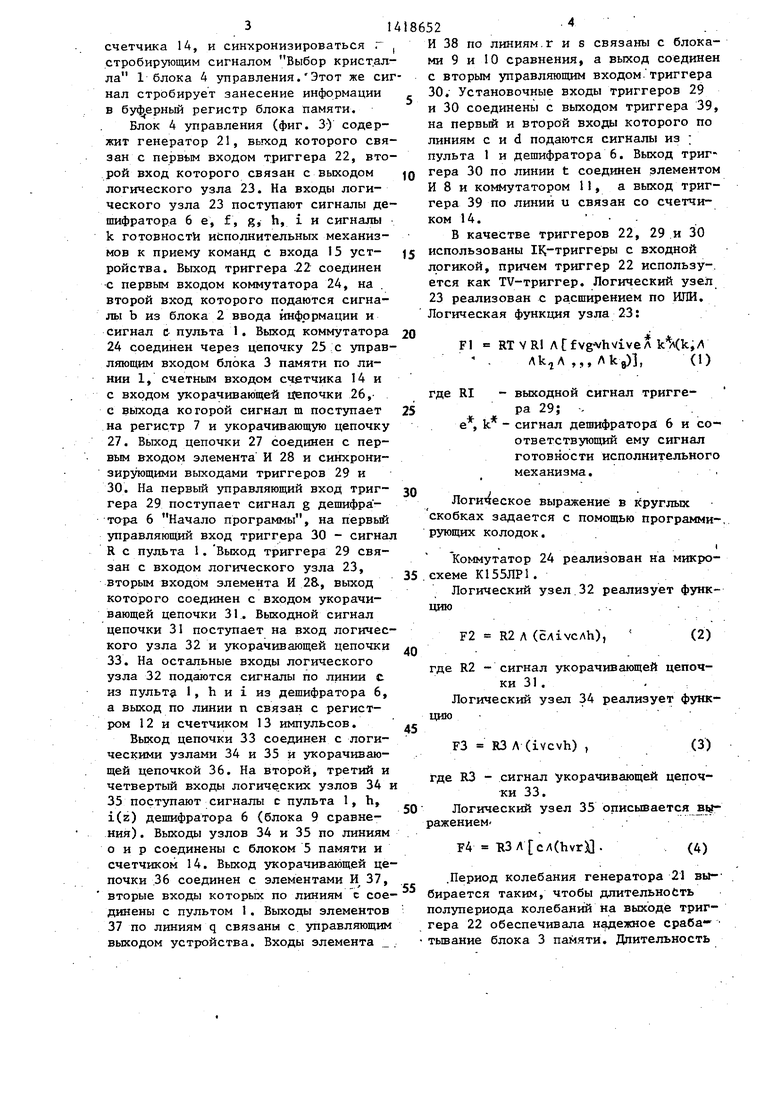

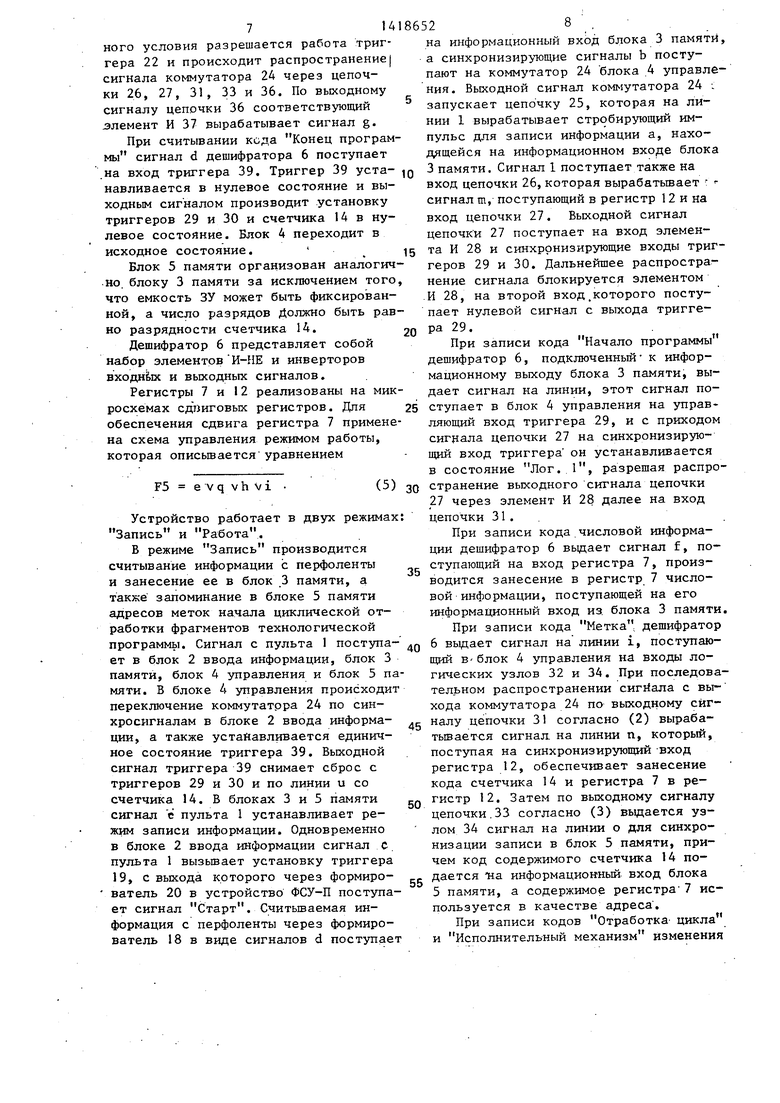

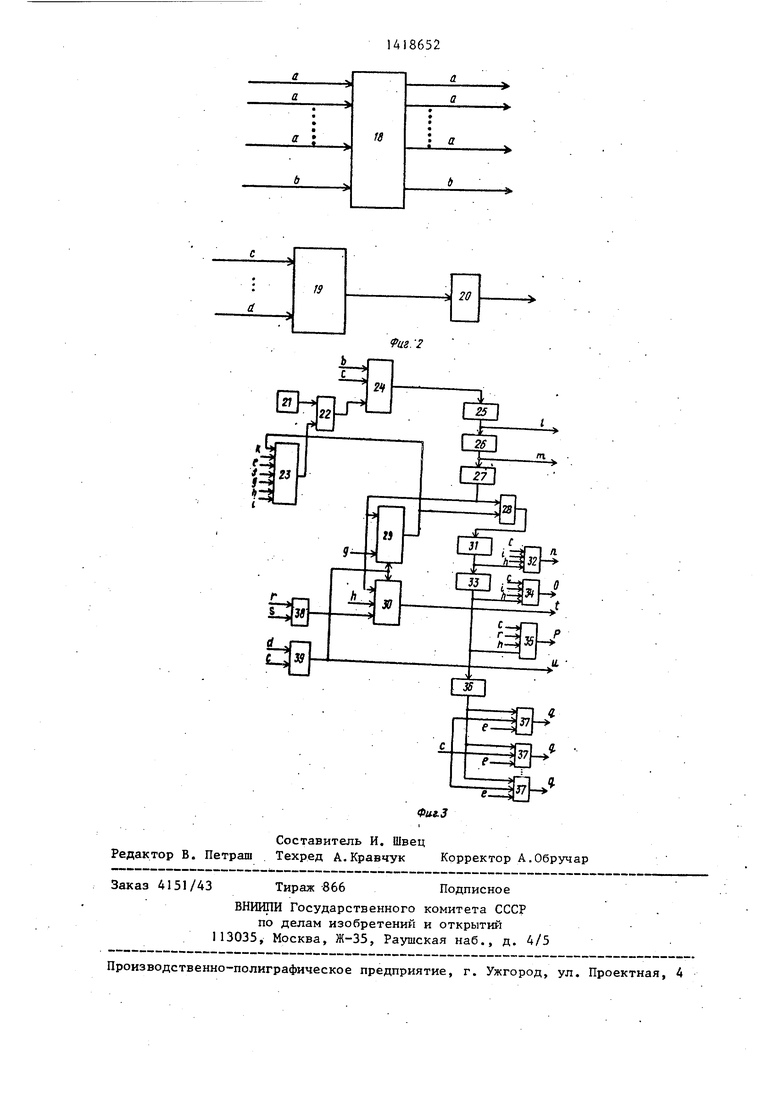

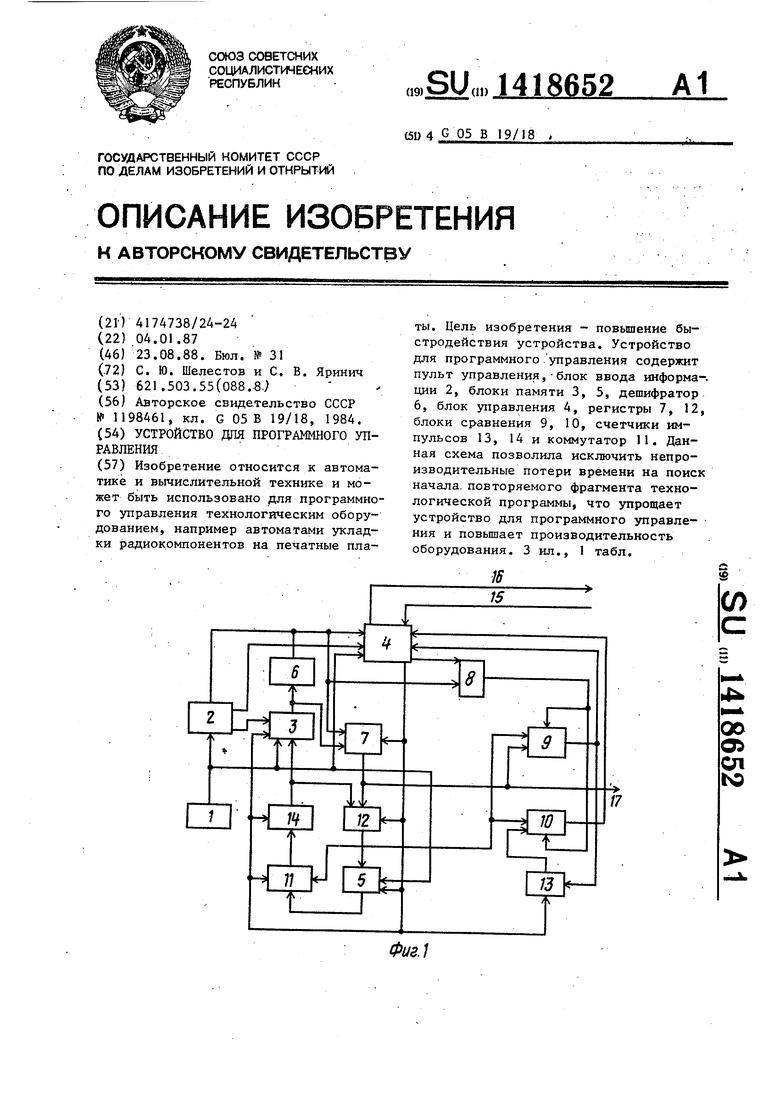

Цель изобретения - повышение бы- стродействия устройства. I На фиг. 1 представлена схема уст- ;ройства для программного управления; на фиг. 2 - схема блока ввода информации; на фиг. 3 - схема блока управления.

: Устро йство содержит пульт 1 управ- |ления, выход которого связан с первы- ми управляющими входами блока 2 ввода ;информации, блока 3 памяти, блока 4 управления и блока 5 памяти. Информационный выход блока 2 ввода информации связан с информационным входом блока 3 памяти, а синхронизирующий Выход - с вторым управляющим входом Ьлока 4 управления. Выход дешифратора 6 связан с вторым управляющим вхо- jii,oM блока 2 ввода информации, третьим управляющим входом блока 4 управления и первым управляющим входом регистра 7, а также с одним из входов элемента И 8, второй вход которого связан с первым управляющим выходом блока 4 управления, а выход - с синхронизирующими входами блоков 9 и 10 срав- йения.

Вход блока 5 памяти и первый вход коммутатора 11 соединены с выходом регистра 12, второй информационный вход блока 9 сравнения - с выходом регистра 7 и входом регистра 12, а второй вход блока 10 сравнения - с выходом счетчика 13. Выход блока 9 сравнения соединен с четвертым управляющим входом блока 4 управ- ления и счетным входог; счетчика 13 импульсов, а выход блока IО сравнения - с пятым управляющим входом блока 4 управления. Выход блока 5 памя-ти связан через коммутатор I1 с адрес- вым входом счетчика 14 импульсов. Второй управляющий выход блока 4 управления связан с управляющими входами регистров 7 и 12, блока 5 памяти, счетчиков 13 и 14, коммутатора 11 и блока 3 памяти. Выход счетчика 14 со- .единен с вторым информационньм входом регистра I2 и адресным входом блока 3 памяти. Информационный вход блока

3 памяти связан с дешифратором 6 и информационным входом регистра 7. Вход 15 и выход 16 блока 4 управления являются управляющими входом и выходом устройства .соответственно, выход 17 регистра 7 является информационным выходом устройства.

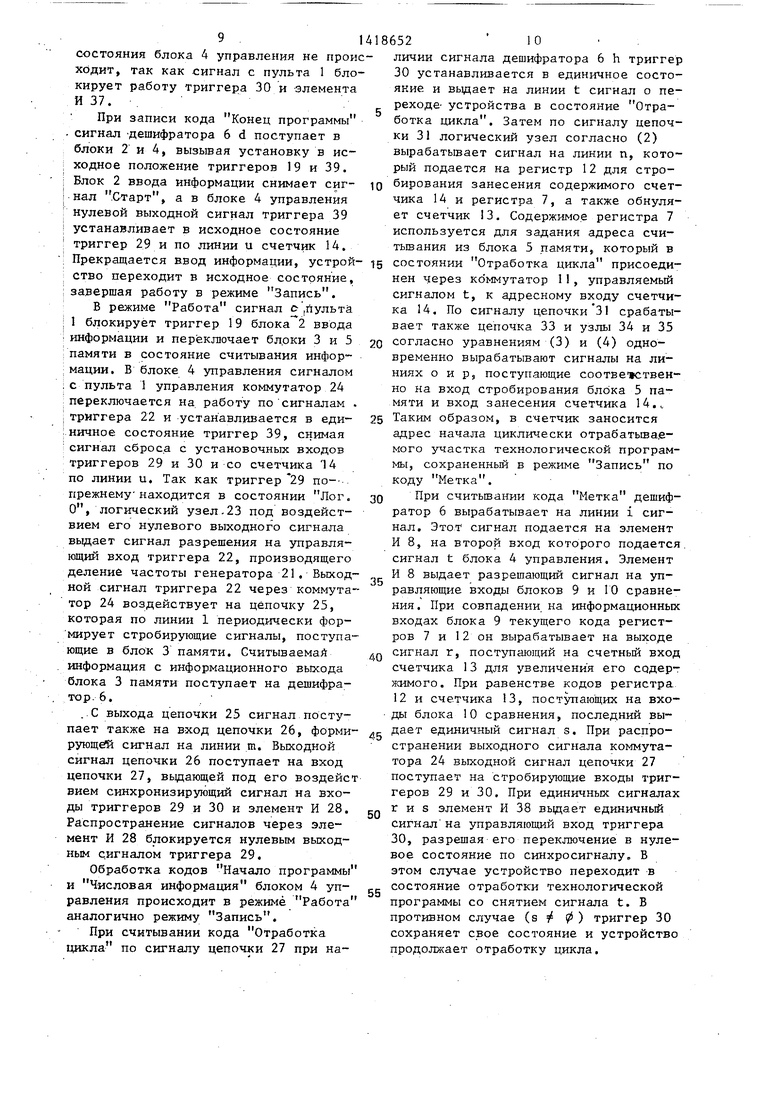

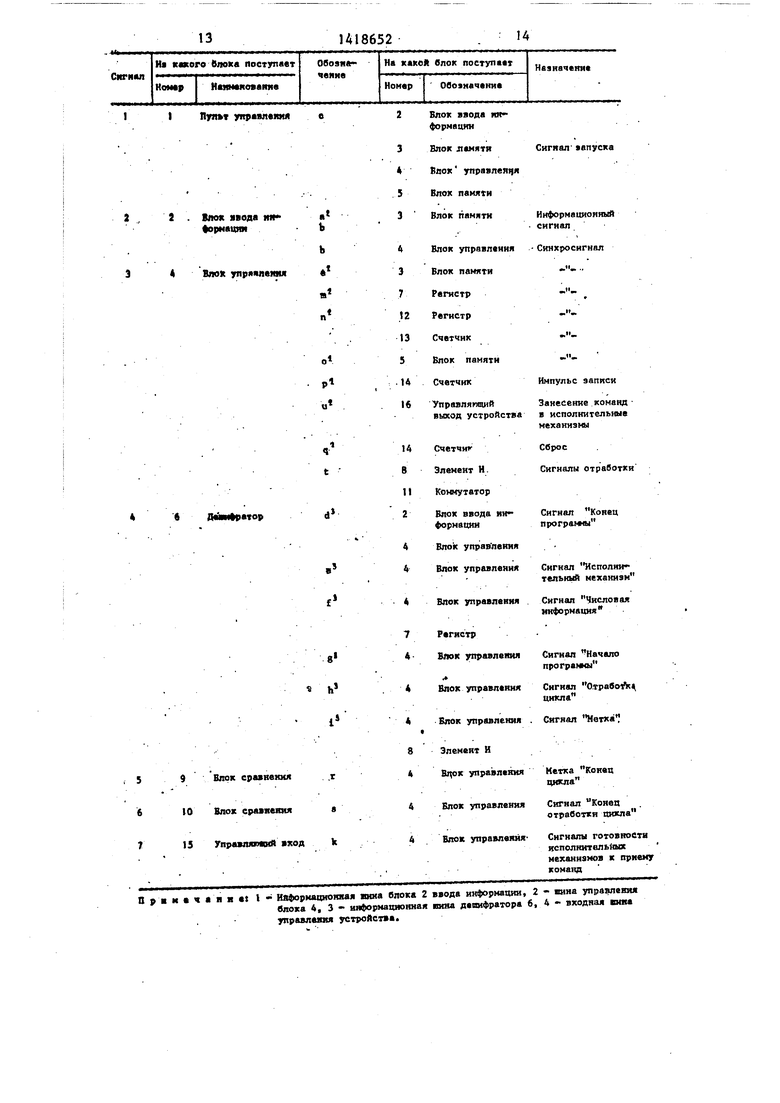

В таблице представлены сигналы, используемые при описании работы устройства.

В состав блока 2 ввода информации (фиг. 2) входят формирователь 18 сигналов, триггер 19 и формирователь 20. Входы формирователя 18 связаны с источником информации, его информационные выходы а соединены с блоком 3 памяти, а синхронизирующий выход - с блоком 4 управления. Входы триггера 19 связаны по линии с с пультом 1 и по линии d - с дешифратором 6, а выход - с входом формирователя 20.

При использовании в качестве источника информации фотосчитьшающего устройства ФСУ-П формирователь 18 сигналов представляет собой набор резисторов, подключенных между выходами ФСУ-П и напряжением питания + 5 В. Формирователь 20 предназначен для формирования стартового импульса ФСУ-П амплитудой + 12 В.

При поступлении на вход триггера 19 блока 2 сигнала с с пульта.1 управления триггер 19 устанавливается в нулевое состояние. Сигнал с выхода последнего поступает на вход формирователя 20, вызывая формирование на его выходе активного уровня сигнала Старт. Происходит последовательное считьюание информации и синхронизирующих сигналов с перфоленты и преобразование их в сигналы d, fc ТТЛ- уровня. При считывании кода Конец программы на вход триггера 19 поступает сигнал по линии d дешифратора 6 и переводит его в исходное состояние. При этом снимается сигнал Старт. В режиме Работа сигнал пульта 1 с блокирует триггер 19 в исходном положении.Блок 3 памяти 5 имеет байтовый формат. Считываемая информация буфе- рируется с помощью регистра. Имеется возможность наращивания емкости блока 3 памяти модулями по К байт. Для этого каждый модуль должен быть оснащен стробируемым дешифратором адреса, который должен управляться старшими г разрядами адреса, поступающего из

25

счетчика 14, и синхронизироваться . стробирующим сигналом Выбор кристалла 1 блока 4 управления. Этот же сигнал стробирует занесение информации . в буферный регистр блока памяти.

Блок 4 управления (фиг. 3-) содержит генератор 21, выход которого связан с первым входом триггера 22, второй вход которого связан с выходом д логического узла 23. На входы логического узла 23 поступают сигналы дешифратора 6 е, f, g, h, i и сигналы k готовности исполнительных механизмов к приему команд с входа 15 устройства. Выход триггера .22 соединен с первым входом коммутатора 24, на . второй вход которого подаются сигналы b из блока 2 ввода информации и сигнал fr пульта 1. Выход коммутатора 20 24 соединен через цепочку 25 с управляющим входом блока 3 памяти по линии 1, счетным входом счетчика 14 и с входом укорачивающей цепочки 26, с выхода которой сигнал m поступает на регистр 7 и укорачивающую цепочку 27. Выход цепочки 27 соединен с первым входом элемента И 28 и синхронизирующими выходами триггеров 29 и 30. На первый управляющий вход триггера 29 поступает сигнал g дешифратора 6 Начало программы, на первый управляющий вход триггера 30 - сигнал R с пульта 1. Выход триггера 29 связан с входом логического узла 23, вторым входом элемента И 28., выход которого соединен с входом укорачивающей цепочки 31. Выходной сигнал цепочки 31 поступает на вход логического узла 32 и укорачивающей цепочки 33. На остальные входы логического узла 32 подаются сигналы по линии с из пульту 1, h и i из дешифратора 6, а выход по линии п связан с регистром 12 и счетчиком 13 импульсов.

Выход цепочки 33 соединен с логическими узлами 34 и 35 и укорачивающей цепочкой 36. На второй, третий и четвертый входы логиче.ских узлов 34 и 35 поступают сигналы с пульта 1, h, i(z) дешифратора 6 (блока 9 сравнения) . Выходы узлов 34 и 35 по линиям о и р соединены с блоком 5 памяти и счетчиком 14. Выход укорачивающей цепочки 36 соединен с элементами И 37,

И 38 по линиям,г и s связаны с бло ми 9 и 10 сравнения, а выход соедин с вторым управляющим входом тригге 30. Установочные входы триггеров 2 и 30 соединены с выходом триггера на первый и второй входы которого п линиям с и d подаются сигналы из ; пульта 1 и дешифратора 6. Выход тр гера 30 по линии t соединен элемен И 8 и коммутатором 11, а выход три гера 39 по линий U связан со счетч ком 14.

В качестве триггеров 22, 29 и 3 J5 использованы IIs-триггеры с входной логикой, причем триггер 22 использ ется как TV-триггер. Логический уз 23 реализован с расширением по ИЛИ Логическая функция узла 23:

F1 RTVR1 Atfvg /hvive (k,A Ak,jA ,,,Лив)1, (

где RI - выходной сигнал триггера 29; е, k - сигнал дешифратора: 6 и с ответствующий ему сигнал готовности исполнительно механизма.

Логическое выражение в круглых скобках задается с помощью программ рующих колодок.

Коммутатор 24 реализован на микр 35.схеме К155ЛР1.

Логический узел 32 реализует фун цию

30

40

45

50

F2 R2 Л (cAivcAh),

где R2 - сигнал укорачивающей цепоч ки 31 .. Логический узел 34 реализует фун цию

F3 R3 Л (ivcvh) ,

Где R3 - сигнал укорачивающей цепоч ки 33.

Логический узел 35 описывается в ражением-,

F4 ИЗЛ cA(hvr5G. (4 .Период колебания генератора 21 в

вторые входы которых по линиям с сое- - бирается таким, чтобы длительность

.

д2018652.4

И 38 по линиям,г и s связаны с блоками 9 и 10 сравнения, а выход соединен с вторым управляющим входом триггера 30. Установочные входы триггеров 29 и 30 соединены с выходом триггера 39, на первый и второй входы которого по линиям с и d подаются сигналы из ; пульта 1 и дешифратора 6. Выход триг гера 30 по линии t соединен элементом И 8 и коммутатором 11, а выход триггера 39 по линий U связан со счетчиком 14.

В качестве триггеров 22, 29 и 30 J5 использованы IIs-триггеры с входной логикой, причем триггер 22 использу-. ется как TV-триггер. Логический узел 23 реализован с расширением по ИЛИ. Логическая функция узла 23:

F1 RTVR1 Atfvg /hvive (k,A Ak,jA ,,,Лив)1, (1)

где RI - выходной сигнал триггера 29; е, k - сигнал дешифратора: 6 и соответствующий ему сигнал готовности исполнительного механизма..

Логическое выражение в круглых скобках задается с помощью программи-, рующих колодок.

I

Коммутатор 24 реализован на микро- схеме К155ЛР1.

Логический узел 32 реализует функцию

F2 R2 Л (cAivcAh),

(2)

где R2 - сигнал укорачивающей цепочки 31 .. Логический узел 34 реализует функцию

F3 R3 Л (ivcvh) ,

(3)

50

Где R3 - сигнал укорачивающей цепочки 33.

Логический узел 35 описывается ву- ражением-,

F4 ИЗЛ cA(hvr5G. (4) .Период колебания генератора 21 вы-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1984 |

|

SU1198461A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для отладки микропроцессорных систем | 1986 |

|

SU1462326A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Логический анализатор | 1983 |

|

SU1170458A1 |

| Обучающее устройство | 1980 |

|

SU875434A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для программного управления технологическим оборудованием, например автоматами укладки радиокрмпонентов на печатные платы. Цель изобретения - повышение быстродействия устройства. Устройство для программного : управления содержит пульт управления,-блок ввода информа-, ции 2, блоки памяти 3, 5, дешифратор 6, блок управления 4, регистры 7, 12, блоки сравнения 9, 10, счетчики импульсов 13, 14 и коммутатор 11. Данная схема позволила исключить непроизводительные потери времени на поиск начала, повторяемого фрагмента технологической программы, что упрощает устройство для программного управления и повьшает производительность оборудования. 3 ил., 1 табл.

динены с пультом 1. Выходы элементов 37 по линиям q связаны с. управляющим выходом устройства. Входы элемента . .

полупериода колебаний На выходе триггера 22 обеспечивала надежное сраба- тьшание блока 3 памяти. Длительность

импульсов, вырабатываемых укорачивающими цепочками 26, 27, 31, 33 и 36, в сумме должна быть меньше длительности полупериода колебаний, поступающих с триггера 22 для обеспечения формирования управляющих сигналов по каждому коду, считываемому из блока 3 памяти.

: Блок 4 управления функционирует IB режимах Запись и Работа. В ре- жиме Запись сигнал с пульта 1 пере- :ключае коммутатор 24 на работу по

rpaMT ibi происходит также формирование сигналов m цепочкой 26 и стробирую- щих сигналов, поступающих на синхро- низирующие входы триггеров 29 и 30. Дальнейшее распространение сигнала с выхода цепочки 27 блокируется элементом И 28, на первый вход которого подаются сигналы с цепочки 27, а на второй - выходной нулевой сигнал R1 триггера 29, В этом состоянии логический .узел 23 по нулевому сигналу R тригсинхронизирующим сигналам b блока 2

;ввода информации. По сигналу е -пульта tg гера 29 формирует единичный управляющий сигнал независимо от сигналов дешифратора 6 на других входах. Входной сигнал логического узла 23 поступает на управляющий вход триггера 22, раз- 20 решая его работу.

При считьшан1-ги кода Начало программы дешифратор 6 выдает сигнал по . линии g, и при постзтлении синхрони- зир лощего сигнала .с выхода цепочки

1 триггер 39 снимает установочный сигнал с триггеров 29 и 30 и по линии t прекращает выдачу сигнала на вход, сброса счетчика 14. При вводе байта информации блок 2 ввода информации .формирует сигнал Ь, который, проходя , через коммутатор 24 и цепочку 25, вы- ;зывает формирование сигнала 1, поступающего в блок 3 памяти ,и счетчик 14,

Выходным сигналом цепочки 25 произво- 25 27 триггер 29 устанавливается в еди- ,дится запуск -цепочки 26, формирующей С игнал на линии т. Выходной сигнал цепочки 26 постзшает также на вход цепочки 27, с выхода которой сигнал Подается на синхронизирующие входы триггеров 29 и 30 и вход элемента И 28. Дальнейшее распространение сиг- Нала блокируется элементом И 28, на Второй вход которого подается нулевой сигнал с выхода триггера 29.

При считывании кода Начало программы из дешифратора 6 по линии g на триггер 29 поступает сигнал, разрешающий его срабатьшание по приходу

ничное состояние, переключая логический узел 23 на работу под управлением сигналов дешифратора 6.

При считывании кода Отработка 30 цикла дешифратор 6 вырабатывает сигнал лршии h,, и при распространении сигнала 1 по цепочкам 26, 27, 31, 33 и 36 вырабатываются сигналы т, п, о и р, причем сигналы о и р вырабатываются одновременно. По сигналу цепочки 27 триггер 30 устанаБливается. в единичное состояние, вырабатьша.ется сигнал на линии t. БЛОК 4 управления переходит в состояние Отработка цик-

35

На синхронизирующий вход сигнала с це- Q ла.

йочки 27. После этого на вход элемен- При считьшании кода Метка по сигта И 28, поступает разрешающий-сигнал, с выхода триггера 29. В дальнейшем |При считьшании кода Метка по сигналам цепочек 3.1 и 33 вырабатываются сигналы на линиях п и о, поступающие на регистр 12 и блок 5 памяти. При считывании кода Конец программы сигналом d дешифратора 6 триггер 39 устанавливается в исходное состояние, и по его выходном сигналу сбрасьша- ются триггеры 29 и 30.

В. режиме Работа по сигналу с -пульта 1 коммутатор 24 переключает- ся на работу по сигналам триггера 22, а также устанавливается триггер 39, вызьшая формирование сигнала линии U. После этого происходит последовательное счи- ывание информации под уп налу цепочки 27 при наличии единичных сигналов г и S устанавливается нуле-, . вое состояние триггера 30, снимая сиг45 иал линии t. Затем по сигналу цепо.чки 38 узлы 34 и 35 выр абатьшают сигналы о Ир. Блок 4 управления завершает работу в состоянии отработка цикла. При считывании кода Исполнитель50 ный механизм из дешифратора 6. поступает один из сигналов е. Согласно .: уравнению (1) логический узел 23 выдает разрешающий сигнал только при .наличии сигнала готовности k этого

gg исполнительного механизма и единичной конъюнкции сигналов в круглых скобках Блок 4 переходит в состояние ожидания готовности исполнительных механизмов. При выполнении заданравлением сигналов 1. из блока 3 памяти кода

До считывания Начало про

rpaMT ibi происходит также формирование сигналов m цепочкой 26 и стробирую- щих сигналов, поступающих на синхро- низирующие входы триггеров 29 и 30. Дальнейшее распространение сигнала с выхода цепочки 27 блокируется элементом И 28, на первый вход которого подаются сигналы с цепочки 27, а на второй - выходной нулевой сигнал R1 триггера 29, В этом состоянии логический узел 23 по нулевому сигналу R триг25 27 триггер 29 устанавливается в еди-

ничное состояние, переключая логический узел 23 на работу под управлением сигналов дешифратора 6.

При считывании кода Отработка 30 цикла дешифратор 6 вырабатывает сигнал лршии h,, и при распространении сигнала 1 по цепочкам 26, 27, 31, 33 и 36 вырабатываются сигналы т, п, о и р, причем сигналы о и р вырабатываются одновременно. По сигналу цепочки 27 триггер 30 устанаБливается. в единичное состояние, вырабатьша.ется сигнал на линии t. БЛОК 4 управления переходит в состояние Отработка цик-

35

налу цепочки 27 при наличии единичных сигналов г и S устанавливается нуле-, . вое состояние триггера 30, снимая сиг45 иал линии t. Затем по сигналу цепо.чки 38 узлы 34 и 35 выр абатьшают сигналы о Ир. Блок 4 управления завершает работу в состоянии отработка цикла. При считывании кода Исполнитель50 ный механизм из дешифратора 6. поступает один из сигналов е. Согласно .: уравнению (1) логический узел 23 выдает разрешающий сигнал только при .наличии сигнала готовности k этого

gg исполнительного механизма и единичной конъюнкции сигналов в круглых скобках Блок 4 переходит в состояние ожидания готовности исполнительных механизмов. При выполнении заданного условия разрешается работа триггера 22 и происходит распространение сигнала коммутатора 24 через цепочки 26, 27, 31, 33 и 36. По выходному сигналу цепочки 36 соответствующий элемент И 37 вырабатывает сигнал g.

При считывании кода Конец программы сигнал d дешифратора 6 поступает .на вход триггера 39. Триггер 39 уста- навливается в нулевое состояние и выходным сигналом производит установку триггеров 29 и 30 и счетчика 14 в нулевое состояние. Блок 4 переходит в исходное состояние.

Блок 5 памяти организован аналогично, блоку 3 памяти за исключением того, что емкость ЗУ может быть фиксированной, а число разрядов Должно быть равно разрядности счетчика 14.

Дешифратор 6 представляет собой набор элементов И-НЕ и инверторов входн&к и выходных сигналов.

Регистры 7 и 12 реализованы на микросхемах сд пиговых регистров. Для обеспечения сдвига регистра 7 применена схема управления режимом работы, которая описьшается уравнением

F5 evqvhvi

Устройство работает в двух режимах Запись и Работа.

В режиме Запись производится считывание информации с перфоленты и занесение ее в блок 3 памяти, а также запоминание в блоке 5 памяти адресов меток начала циклической отработки фрагментов технологической программь. Сигнал с пульта 1 поступа- ет в блок 2 ввода информации, блок 3 памяти, блок 4 управления и блок 5 памяти. В блоке 4 управления происходит переключение коммутатора 24 по синхросигналам в блоке 2 ввода информации, а также устайавливается единичное состояние триггера 39. Выходной сигнал триггера 39 снимает сброс с триггеров 29 и 30 и по линии и со счетчика 14. В блоках 3 и 5 памяти сигнал с пульта 1 устанавливает режим записи информации. Одновременно в блоке 2 ввода информации сигнал с пульта 1 вызьшает установку триггера 19, с выхода которого через формирователь 20 в устройство ФСУ-П поступает сигнал Старт. Считьшаемая информация с перфоленты через формирователь 18 в виде сигналов d поступает

Q 5

, 25

20

30

35

:

.g

50

на информационный вход блока 3 памяти, а синхронизирующие сигналы b поступают на коммутатор 24 блока 4 управления. Выходной сигнал кoм yтaтopa 24 , запускает цепочку 25, которая на линии 1 вырабатывает стробирующий импульс для записи информации а, находящейся на информационном входе блока 3 памяти. Сигнал 1 поступает также на вход цепочки 26, которая вырабатьшает - сигнал т, поступающий в регистр 12 и на вход цепочки 27. Выходной сигнал цепочки 27 поступает на вход элемента И 28 и синхронизирующие входы триггеров 29 и 30. Дальнейшее распространение сигнала блокируется элементом -И 28, на второй вход.которого поступает нулевой сигнал с выхода триггера 29.

При записи кода Начало программы дешифратор 6, подключенный к информационному выходу блока 3 памяти, выдает сигнал на линии, этот сигнал поступает в блок 4 управления на управляющий вход триггера 29, и с приходом сигнала цепочки 27 на синхронизирующий вход триггера он устанавливается в состояние Лог. 1, разрешая распространение выходного сигнала цепочки 27 через элемент И 28 далее на вход цепочки 31..

При записи кода числовой информации дешифратор 6 выдает сигнал f, поступающий на вход регистра 7, производится занесение в регистр 7 числовой информации, поступающей на его информационный вход из. блока 3 памяти.

При записи кода Метка ; дешифратор 6 выдает сигнал на линии i, поступаю- ций в- блок 4 управления на входы логических узлов 32 и 34. При последовательном распространении сигйала с вы- хода коммутатора 24 по выходному сигналу цепочки 31 согласно (2) выраба тьгоаетсн сигнал, на линии п, который, поступая на синхронизирующий вход регистра 12, обеспечэшает занесение кода счетчика 14 и регистра 7 в регистр 12. Затем по выходному сигналу цепочки.33 согласно (3) вьщается узлом 34 сигнал на линии о для синхронизации записи в блок 5 памяти, причем код содержимого счетчика 14 подается на информационньй вход блока 5 памяти, а содержимое регистра 7 используется в качестве адреса .

При записи кодов Отработка- цикла и Исполнительный механизм изменения

состояния блока 4 управления не происходит, так как сигнал с пульта 1 блокирует работу триггера 30 и элемента И 37.

При записи кода Конец программы сигнал -дешифратора 6 d поступает в блоки 2 и 4, вызывая установку в исходное положение триггеров 19 и 39. Блок 2 ввода информации снимает сиг- нал .Старт, а в блоке 4 управления нулевой выходной сигнал триггера 39 устанавливает в исходное состояние триггер 29 и по линии и счетчик 14.

; Прекращается ввод информации, устрой- 15 состоянии Отработка цикла присоеди; ство переходит в исходное состояние,

: завершая работу в режиме Запись. В режиме Работа сигнал с- |Лульта

; 1 блокирует триггер 19 блока 2 ввода

информации и переключает блоки 3 и 5

:памяти в состояние считывания инфор: мации. В блоке 4 управления сигналом

iс пульта 1 управления коммутатор 24

; переключается на. работу по сигналам .

;триггера 22 и устанавливается в еди;ничное состояние триггер 39, снимая

сигнал сброса с установочных входов триггеров 29 и 30 и со счетчика 14 по линии U. Так как триггер 29 по-прежнему находится в состоянии Лог.

20

25

30

нен через коммутатор I1, управляемый сигналом t, к адресному входу счетчика 14. По сигналу цепочки 31 срабатывает также цепочка 33 и узлы 34 и 35 согласно уравнениям (3) и (4) одновременно вырабатывают сигналы на линиях о и р, поступающие соотве ствен- но на вход стробирования блока 5 памяти и вход занесения счетчика 14. Таким образом, в счетчик заносится адрес начала циклически отрабатьша.е- мого участка технологической программы, сохраненный в режиме Запись по коду Метка.

При считывании кода Метка дешифратор 6 вырабатывает на линии i сигнал. Этот сигнал подается на элемент И 8, на второй вход которого подается сигнал t блока 4 управления. Элемент И 8 выдает разрешающий сигнал на управляющие входы блоков 9 и 10 сравнения. При совпадении на информационных входах блока 9 текущего кода регистров 7 и 12 он вырабатывает на выходе сигнал г, поступающий на счетный вход счетчика 13 для увеличения его содержимого. При равенстве кодов регистра. 12 и счетчика 13, поступающих на входы блока 10 сравнения, последний выдает единичный сигнал s. При распространении выходного сигнала коммутатора 24 выходной сигнал цепочки 27 поступает на стробирующие входы триггеров 29 и 30. При единичных сигналах г и S элемент И 38 выдает единичный сигнал на управляющий вход триггера 30, разрешая его переключение в нулевое состояние по синхросигналу, В этом случае устройство переходит в состояние отработки технологической программы со снятием сигнала t. В противном случае (s / ) триггер 30 сохраняет свое состояние и устройство продолжает отработку цикла.

О , логический узел-23 под воздействием его нулевого выходного сигнала вьщает сигнал разрешения на управляющий вход триггера 22, производящего деление частоты генератора 21, Выходной сигнал триггера 22 через коммутатор 24 воздействует на цепочку 25, которая по линия 1 периодически фор- мирует стробирующие сигналы, поступающие в блок 3 памяти. Считываемай информация с информационного выхода блока 3 памяти поступает на дешифратор. 6.

..С выхода цепочки 25 сигнал поступает также на вход цепочки 26, форми- рующе(й сигнал на линии т. Выходной сигнал цепочки 26 поступает на вход цепочки 27, вьщающей под его воздейст вием синхронизирующий сигнал на входы триггеров 29 и 30 и элемент И 28. Распространение сигналов через элемент И 28 блокируется нулевым выходным сигналом триггера 29.

Обработка кодов Начало программы и Числовая информация блоком 4 управления происходит в режиме Работа аналогично режиму Запись.

При считывании кода Отработка цикла по сигналу цепочки 27 при наличии сигнала дешифратора 6 h триггер 30 устанавливается в единичное состояние и выдает на линии t сигнал о переходе- устройства в состояние Отработка цикла. Затем по сигналу цепочки 3 1 логический узел согласно (2) вырабатьюает сигнал на линии п, который подается на регистр 12 для стро- бирования занесения содержимого счетчика 14 и регистра 7, а также обнуляет счетчик 3. Содержимое регистра 7 используется для задания адреса считывания из блока 5 памяти, который в

0

5

0

5

0

5

0

5

нен через коммутатор I1, управляемый сигналом t, к адресному входу счетчика 14. По сигналу цепочки 31 срабатывает также цепочка 33 и узлы 34 и 35 согласно уравнениям (3) и (4) одновременно вырабатывают сигналы на линиях о и р, поступающие соотве ствен- но на вход стробирования блока 5 памяти и вход занесения счетчика 14. Таким образом, в счетчик заносится адрес начала циклически отрабатьша.е- мого участка технологической программы, сохраненный в режиме Запись по коду Метка.

При считывании кода Метка дешифратор 6 вырабатывает на линии i сигнал. Этот сигнал подается на элемент И 8, на второй вход которого подается, сигнал t блока 4 управления. Элемент И 8 выдает разрешающий сигнал на управляющие входы блоков 9 и 10 сравнения. При совпадении на информационных входах блока 9 текущего кода регистров 7 и 12 он вырабатывает на выходе сигнал г, поступающий на счетный вход счетчика 13 для увеличения его содержимого. При равенстве кодов регистра. 12 и счетчика 13, поступающих на входы блока 10 сравнения, последний выдает единичный сигнал s. При распространении выходного сигнала коммутатора 24 выходной сигнал цепочки 27 поступает на стробирующие входы триггеров 29 и 30. При единичных сигналах г и S элемент И 38 выдает единичный сигнал на управляющий вход триггера 30, разрешая его переключение в нулевое состояние по синхросигналу, В этом случае устройство переходит в состояние отработки технологической программы со снятием сигнала t. В противном случае (s / ) триггер 30 сохраняет свое состояние и устройство продолжает отработку цикла.

Ирк срабатьюании цепочки 33 узел 34 вьфабатьшает сигнал о стробирова- ния блока 5 памяти, а узел 35 - сигнал р занесения в счетчик 14. Заносимая в счетчик 14 информация зависит . от. сигнала t, выдаваемого триггером 30. При наличии единичного сигнала t в счетчик 14 заносится содержимое блока 5 памяти (продолжается работа в состоянии Отработка цикла), а при нулевом сигнале t в счетчик 14 через коммутатор 11 по сигналу р заносится содержимое регистра 12 (адрес

команды Отработка цикла). Устройст- 15 рого блоков сравнения, первые инфорво переходит к последовательной выда- че команд технологической программы, прерванной командой Отработка цикла, В случае считывания кода Метка при нулевом сигнале t узел 34 по сигналу цепочки 33 формирует сигнал -о, однако, так как элемент И 8 при нулевом значении сигнала запрещает выработку блоком 9 сравнения сигнала, узел 35

не ведает сигналы р и естественный порядок отработки команд технологической программы не нарушается.

При считывании кода Исполнительный механизм дешифратор 6 вьщает один из сигналов е, который поступит на логический узел 23 и один из элементов И блока 4 управления. Согласно (1) узел 23 выдает разрешающий сигнал на вход триггера 22 только при наличии сигнала готовности, к приему команды указанного -исполнительного . еханизма, а также при наличии- сигнаов готовности исполнительных механизов, заданных в (1) с помощью программирующей колодки. В этом случае сра- батьшает триггер 22 и начинается поседовательное распределение сигналов по цепочкам 25, 27, 31, 33 и 36. Выходной сигнал цепочки 36 поступает на входы элемента И 37. На выходе одного из элементов И 37, выбранного сигналом е дешифратора 6, формируется сигнал занесения числового значения команды с выхода регистра 7 в выбранный исполнительный механизм.

Отработка кода Конец программы в режиме Работа аналогична режиму

Запись. Формула изобретения

Устройство для программного управления, содержащее пульт управления, выход которого соединен с первыми уп- равляющнми входами блока ввода информации, первого блока памяти и блока

управления, второй управляющий вход блока ввода информации соединен с выходом дешифратора, первый н второй вькоды блока ввода информации подключены к информационным входам первого блока памяти и блока управления соответственно, выход дешифратора подклю чен к третьему входу блока управления, к управляющим, входам первого регистра и к первому входу элемента И, второй вход которого соединен с первым выходом блока управления, а вькод - с синхронизирующими входами первого и вто0

5

0

Е

мационные входы которых соединены с выходом второго регистра, второй информационный вход первого блока срав- нения .соединен с выходом первого регистра и с первым входом .второго регистра и является первым выходом устройства для программного управления, второй информационный вход второго блока сравнения соединен.с выходом первого счетчика импульсов, выход первого блока сравнения соединен с четвертым входом блока управления и со счетным входом первого счетчика импульсов, а выход втррого блока сравнения подключен к пятому входу блока управления, второй управляющий выход которого соединен с управляющими входами первого и второго регистров, первого и вто- рого с,четчиков импульсов и первого блока памяти, выход второго счетчика импульсов подключен к вто.рым информационным входам второго регистра -и к адресным входам первого блока памяти, информационный выход которого со единен с входом дешифратора и с информационным входом перво.го регистра, отличающееся тем, что, с целью првьш1ения быстродействия устройства, в него введены коммутатор 5 адреса и второй блок памяти, первый управляющий вход которого соединен с третьим управляющим входом блока управления и с управляющим входом коммутатора адреса, второй управляющий вход второго блока памяти подключен к выходу пульта управления, а информационный вход.- к выходу второго регистра и к первому информационному входу коммутатора адреса, выход второго блока памяти соединен с вторым информационным входом коммутатора адреса, соединенного выходом с информационным входом второго счетчика импульсов .

0

0

5

n р м ч я в «S I - Иафорнащюяяая иияа вяока 2 вводе информация, 2 блоха 4, 3 няформациояяая вина дешифратора 6, улравлевяя устройства

- шияа ртравлевяя 4 входная пша

| Устройство для программного управления | 1984 |

|

SU1198461A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-04—Подача