Изобретение относится к области вычислительной техники, в частности к архитектуре процессоров конвейерного типа, предназначенных для использования при осуществлении параллельных вычислений на уровне элементарных операций, в том числе к технике аппаратной поддержки конвейеризованных циклов для архитектур с использованием широких команд.

Из уровня техники известно, что отдельные независимые операции объединяются в параллельные группы, называемые широкими командами, которые выполняются аппаратурой как единое целое в каждом машинном такте (см. патент США 5418975, кл. G 06 F 009/00 от 23 мая 1995 г.). Высокая производительность вычислительной системы на базе процессоров широкого командного слова достигается при помощи оптимизирующего компилятора - системной программы, осуществляющей перевод прикладного математического обеспечения с языков программирования в параллельный объектный код. При этом при использовании широких команд обеспечивается оптимизация процессов обработки, главным образом состоящая в выявлении параллельных операций исходной программы и наборе из них широкого командного слова (см. патент СССР 1804645, кл. G 06 F 15/76 от 27.03.91).

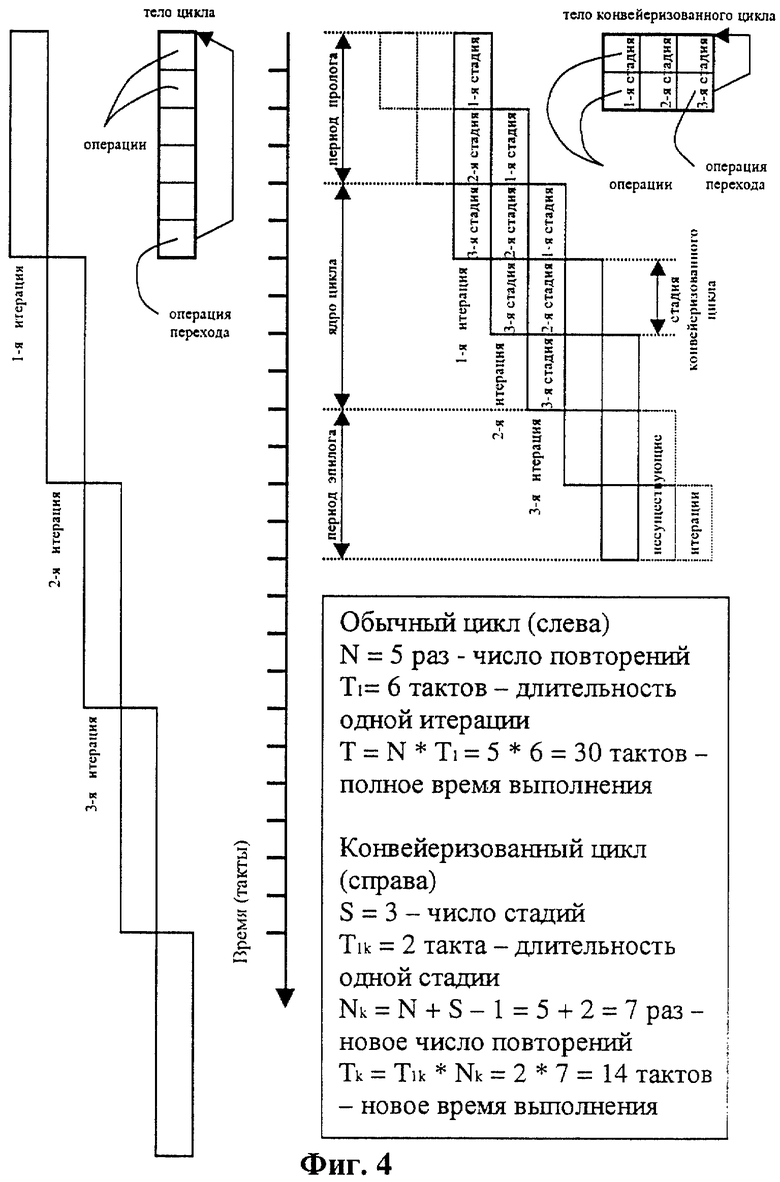

Производительность современных вычислительных систем в значительной степени определяется скоростью обработки регулярно повторяющихся участков программ (циклов). Совокупность вычислений, реализующих регулярно повторяющееся действие цикла, называют итерацией цикла (loop iteration), а машинный код итерации - телом цикла (loop body). Скорость вычислений для таких участков обычно определяется временем выполнения одной итерации цикла и числом повторений цикла, которое задано алгоритмом программы. Ускорить обработку цикла можно путем совмещения во времени вычислений с нескольких соседних итераций цикла. При этом очередная итерация цикла начинается не ожидая окончания текущей итерации, как бы образуя конвейер. Оптимизация такого рода получила название программной конвейеризации цикла, а оптимизированный цикл считается конвейеризованным (pipelined loop). Исходная итерация цикла разбивается на одинаковые интервалы времени, содержащие фрагменты вычислений и называемые стадиями конвейера (pipeline stage). Конвейеризованный цикл содержит параллельный код всех стадий конвейера. Количество стадий и их продолжительность (в машинных тактах) определяются исходя из вычислительных возможностей архитектуры процессора и характеристик самого цикла.

При работе конвейеризованного цикла за время, равное длительности стадии конвейера, выполняется первая стадия текущей i-й итерации исходного цикла, вторая стадия предыдущей (i-1)-й итерации, третья стадия (i-2)-й и т. д. При числе стадий конвейера цикла, равном S, параллельно выполняются вычисления сразу для S соседних итераций, смещенных по времени друг относительно друга на одну стадию конвейера. Для разгона и остановки конвейера, как правило, строится отдельный код. Можно выполнить эту функцию и с помощью кода самого конвейеризованного цикла при наличии специальной аппаратной поддержки (системы управления конвейеризованным циклом). Данная система обеспечивает плавное включение в работу вычислений первых S-1 стадий, которые принято называть периодом пролога (loop prologue period) конвейеризованного цикла, и плавное выключение вычислений последних S-1 стадий опорожнения конвейера, образующих период эпилога (loop epilogue period) конвейеризованного цикла. Между периодами пролога и эпилога неограниченно долго цикл может работать с полностью загруженным конвейером (ядро конвейеризованного цикла - loop kernel). Например, для цикла с числом стадий S=3 и числом повторений N=5 периоды пролога и эпилога будут длиться в течение 2-х стадий, а ядро займет К= 3 стадий. Число повторений конвейеризованного цикла с учетом разгона и остановки конвейера в этом случае составит Nk=7 раз (см. фиг.4). Управление работой конвейеризованного цикла в течение периодов пролога и эпилога осуществляется путем отмены операций обращения в оперативную память и изменения условий операций перехода, относящихся к несуществующим итерациям исходного цикла.

Известна система управления работой конвейеризованного цикла процессора широкого командного слова, содержащая КЭШ память широких команд, регистровую матрицу, дешифратор широких команд, устройство управления, устройство команд, исполнительное устройство, подключенные к системной шине (см. статью "The Cydra 5 Minisupercomputer: Architecture and Implementation", Journal of Supercomputing, 7, 143-180 (1993)).

Указанная система рассчитана на построение кода цикла без программного пролога и эпилога.

Однако функции разгона и остановки программного конвейера цикла выполняются дополнительными командами, закодированными в самом теле цикла, что при определенных обстоятельствах может привести к росту времени выполнения цикла. Замедление исполнения цикла происходит в силу двух причин: во-первых, увеличивается количество операций в теле цикла и для выполнения каждой стадии программного конвейера требуется больше машинных тактов; во-вторых, растет число стадий конвейера, необходимых для выполнения одной итерации цикла. Особенно сильно это замедление может проявиться для циклов с малым количеством операций и большим числом повторений.

По технической сущности наиболее близким к заявляемому изобретению является система управления конвейеризованным циклом процессора широкого командного слова (ARCHITECTURAL SUPPORT FOR EXECUTION CONTROL OF PROLOGUE AND EPILOGUE PERIODS OF LOOPS IN A VLIW PROCESSOR), содержащая КЭШ память широких команд, блок регистров общего назначения, дешифратор широких команд, устройство управления, блок выдачи адреса перехода, как минимум одно устройство считывания из оперативной памяти, как минимум одно устройство записи в оперативную память, при этом информационный вход КЭШ памяти команд, первые входы-выходы устройств считывания и выходы устройств записи подключены к шине оперативной памяти, информационный выход КЭШ памяти - к информационному входу дешифратора широких команд, блок регистров связан двунаправленной шиной данных с информационным входом-выходом устройства управления, со вторыми информационными входами-выходами устройств считывания и с информационными входами-выходами устройств записи (см. патент США 5794029, кл. G 06 F 9/445 от 18 октября 1996 г.).

Данная система рассчитана на применение в процессоре с аппаратной поддержкой предикатных вычислений и позволяет исключить из цикла операции, связанные с разгоном и остановкой программного конвейера.

Однако данная система имеет ограниченные функциональные возможности при конвейеризации цикла со сложной структурой управления, поскольку рассчитана на выполнение лишь одной команды перехода в теле цикла. Для расширения функциональных возможностей данной системы применительно ко всем циклам потребуется значительное усложнение устройства управления и, как следствие, понижение тактовой частоты, что приведет к ограничению быстродействия процессора.

Техническим результатом изобретения является расширение функциональных возможностей системы управления конвейеризованным циклом процессора широкого командного слова при сохранении высокой тактовой частоты.

Для этого в системе управления конвейеризованным циклом процессора широкого командного слова, содержащей КЭШ память широких команд, блок регистров, дешифратор широких команд, устройство управления, блок выдачи адреса перехода, как минимум одно устройство считывания из оперативной памяти, как минимум одно устройство записи в оперативную память, причем информационный вход КЭШ памяти команд, первый вход-выход устройств считывания из оперативной памяти и выход устройств записи в оперативную память подключены к шине оперативной памяти, информационный выход КЭШ памяти команд подключен к информационному входу дешифратора широких команд, управляющий вход которого подключен к выходу блока выдачи адреса перехода, блок регистров связан двунаправленной шиной данных с информационным входом-выходом устройства управления, со вторым информационным входом-выходом устройств считывания из оперативной памяти и с информационным входом-выходом устройств записи в оперативную память, согласно изобретению введено устройство управления прологом и эпилогом конвейеризованного цикла, подключенное управляющим входом к выходной шине дешифратора широких команд, информационным входом - к двунаправленной шине данных блока регистров, а устройства считывания из оперативной памяти, записи в оперативную память и блок выдачи адреса перехода подключены управляющим входом к выходной шине устройства управления прологом и эпилогом конвейеризованного цикла.

При этом устройство управления прологом и эпилогом конвейеризованного цикла содержит блок фиксации периода эпилога конвейеризованного цикла, блок фиксации момента окончания эпилога конвейеризованного цикла, блок фиксации периода пролога конвейеризованного цикла и блок задания режимов работы, причем первые управляющие входы блока фиксации периода эпилога конвейеризованного цикла, блока фиксации момента окончания эпилога конвейеризованного цикла и блока фиксации периода пролога конвейеризованного цикла подключены к управляющему входу устройства, второй управляющий и информационный входы блока фиксации периода эпилога конвейеризованного цикла, блока фиксации момента окончания эпилога конвейеризованного цикла, блока фиксации периода пролога конвейеризованного цикла, информационный и управляющий входы блока задания режимов работы подключены к информационному входу устройства, первый управляющий выход блока фиксации периода эпилога конвейеризованного цикла, управляющий выход блока фиксации момента окончания эпилога конвейеризованного цикла и управляющий выход блока фиксации периода пролога конвейеризованного цикла подключены к выходной шине устройства управления прологом и эпилогом конвейеризованного цикла, второй управляющий выход блока фиксации периода эпилога конвейеризованного цикла подключен к третьему управляющему входу блока фиксации момента окончания эпилога конвейеризованного цикла, первый и второй управляющие выходы блока задания режимов работы подключены к третьему управляющему входу блока фиксации периода эпилога конвейеризованного цикла и блока фиксации периода пролога конвейеризованного цикла соответственно.

Кроме того, блок фиксации периода эпилога конвейеризованного цикла содержит мультиплексор, регистр, сумматор, компаратор и элемент И, причем к первому управляющему входу блока подключены первый и второй управляющие входы сумматора и элемента И, управляющий вход мультиплексора является вторым управляющим входом блока, третий управляющий вход элемента И и его выход являются соответственно третьим управляющим входом и первым управляющим выходом блока, второй управляющий выход которого подключен к выходу компаратора и четвертому управляющему входу элемента И, первый информационный вход мультиплексора является информационным входом блока, информационный выход мультиплексора подключен к информационному входу регистра, информационный выход которого подключен к информационному входу сумматора, информационный выход которого подключен к информационному входу компаратора и второму информационному входу мультиплексора.

Кроме того, блок фиксации момента окончания эпилога конвейеризованного цикла содержит мультиплексор, регистр, сумматор, компаратор и элемент И, причем к первому управляющему входу блока подключены первый и второй управляющие входы сумматора и элемента И, выход которого является управляющим выходом блока, ко второму управляющему и информационному входам которого подключены соответственно управляющий и первый информационный входы мультиплексора, выход которого подключен к информационному входу регистра, информационный выход которого подключен к информационному входу сумматора, информационный выход которого подключен к информационному входу компаратора и второму информационному входу мультиплексора, третий управляющий вход сумматора является третьим управляющим входом блока, выход компаратора подключен к третьему управляющему входу элемента И.

Кроме того, блок фиксации периода пролога конвейеризованного цикла содержит первый и второй мультиплексоры, сдвиговый регистр, триггер и элемент И, причем к первому управляющему входу блока подключены первый и второй управляющие входы сдвигового регистра и элемента И, ко второму управляющему входу блока подключены управляющие входы первого и второго мультиплексоров, к информационному входу блока подключены первые информационные входы первого и второго мультиплексоров, вторые информационные входы которых подключены соответственно к первому и второму информационным выходам сдвигового регистра, информационный вход которого соединен с выходом первого мультиплексора, третий управляющий вход и выход элемента И являются соответственно третьим управляющим входом и выходом блока, а выход второго мультиплексора подключен ко входу триггера, выход которого подключен к четвертому управляющему входу элемента И.

Кроме того, блок задания режима работы содержит первый и второй регистры, причем информационный вход первого и второго регистров подключен к информационному входу блока, управляющий вход первого и второго регистров подключен к управляющему входу блока, первым и вторым управляющими выходами которого являются выход второго и выход первого регистров соответственно.

Сущность изобретения заключается в том, что введение устройства управления прологом и эпилогом конвейеризованного цикла и соответствующее его подключение позволяют при организации конвейеризованного цикла получить без усложнения устройства управления и при сохранении высокого быстродействия процессора длительность одной стадии конвейера, равную одному машинному такту, в то время как в прототипе такой же цикл имел бы размер стадии не менее двух машинных тактов.

Сравнение с ближайшим аналогом позволяет утверждать о выполнении критерия "новизна", а отсутствие в аналогах отличительных признаков заявляемой системы позволяет говорить о выполнении критерия "изобретательский уровень". Предварительные испытания подтверждают возможность широкого промышленного использования изобретения.

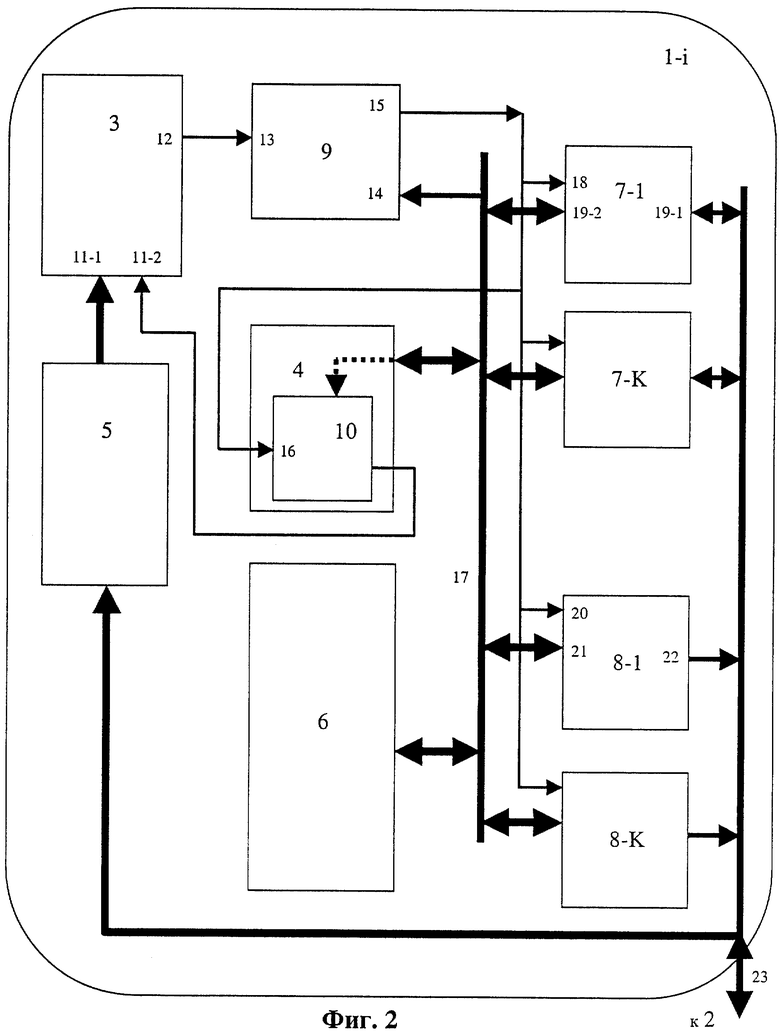

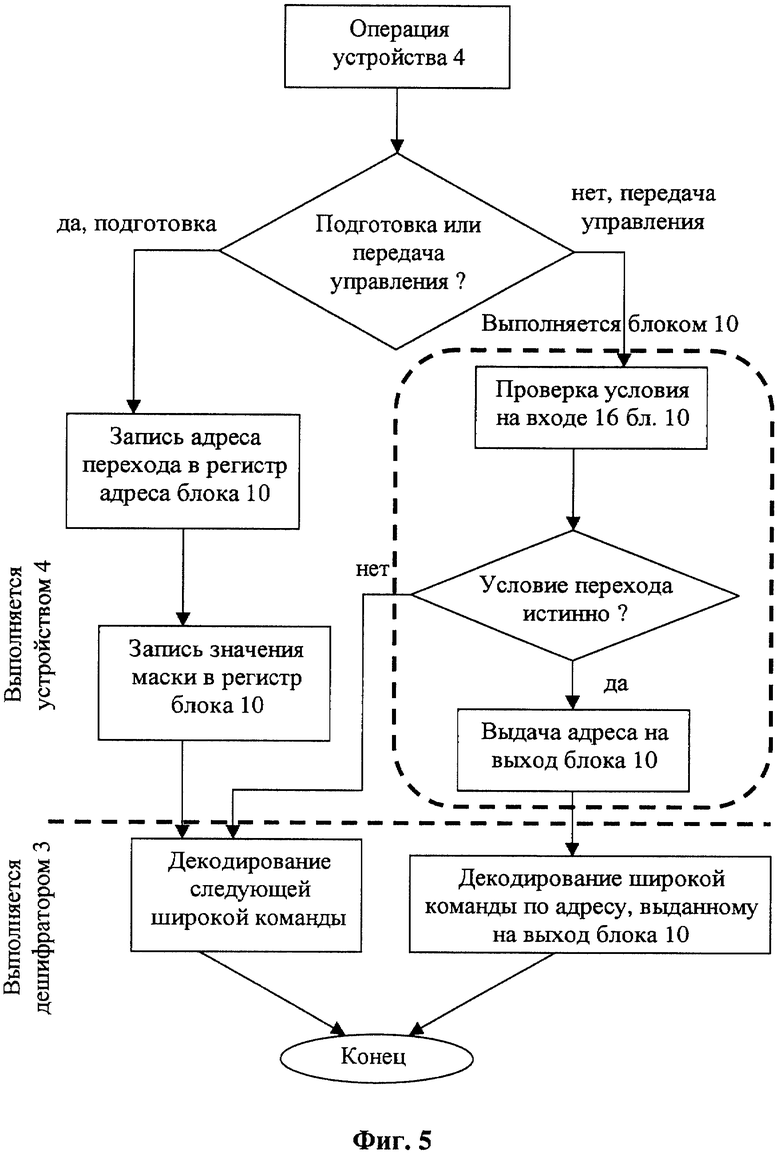

На Фиг.1 представлена блок-схема многопроцессорной вычислительной системы, на Фиг.2 представлена система управления конвейеризованным циклом процессора широкого командного слова, на Фиг.3 представлено устройство управления прологом и эпилогом конвейеризованного цикла, на Фиг.4 приведены пример реализации конвейеризованного цикла и сравнение с неоптимизированным случаем, на Фиг.5 представлена блок-схема алгоритма работы устройства 4 и дешифратора 3 при выполнении команд передачи управления.

Система управления конвейеризованным циклом процессора широкого командного слова является составной частью многопроцессорной вычислительной системы, которая включает процессоры 1-1...1-N широкого командного слова и оперативную память 2. Система содержит дешифратор 3 широких команд, устройство 4 управления, КЭШ память 5 широких команд, блок 6 регистров, устройства 7-1. . . 7-К считывания из оперативной памяти, устройства 8-1...8-К записи в оперативную память, устройство 9 управления прологом и эпилогом конвейеризованного цикла, блок 10 выдачи адреса перехода. Дешифратор 3 широких команд содержит информационный вход 11-1, управляющий вход 11-2 и выходную шину 12. Устройство 9 управления прологом и эпилогом конвейеризованного цикла содержит управляющий вход 13, информационный вход 14 и выходную шину 15. Блок 10 выдачи адреса перехода содержит управляющий вход 16 и управляющий выход, подключенный к управляющему входу 11-2 дешифратора 3.

Кроме того, система содержит двунаправленную шину 17 данных, обеспечивающую связь информационного входа-выхода блока 6 с устройством 4 через его информационный вход-выход и с устройством 9 через его информационный вход 14. Каждое из устройств 7-i содержит управляющий вход 18 и первый и второй информационные входы-выходы 19-1 и 19-2 соответственно. Каждое из устройств 8-i содержит управляющий вход 20, информационный вход-выход 21 и информационный выход 22. К шине 23 связи с оперативной памятью 2 подключены первые информационные входы-выходы 19-1 устройств 7-i, информационные выходы 22 устройств 8-i и информационный вход КЭШ памяти 5, информационный выход которой подключен к информационному входу 11-1 дешифратора 3, выходная шина 12 которого подключена к управляющему входу 13 устройства 9. Выходная шина 15 последнего подключена к управляющим входам 18 и 20 устройств 7-i и 8-i соответственно и к управляющему входу 16 блока 10. Двунаправленная шина 17 также обеспечивает связь информационных входов-выходов 19-2 и 21 устройств 7-i и 8-i соответственно с информационным входом-выходом блока 6.

Дешифратор 3, устройство 4, КЭШ память 5, блок 6, устройства 7-i и 8-i могут быть выполнены аналогично соответствующим блокам процессора прототипа (Фиг.2 и 4 патента США 5794029). Дешифратор 3 представляет собой стандартный дешифратор, предназначенный для распаковки (декодирования) всех операций, входящих в состав текущей широкой команды, поступающей на его информационный вход, и выработки (формирования) сигналов запуска исполнительных устройств процессора, в том числе устройств 7-i и 8-i. КЭШ память 5 может быть выполнена как стандартное ассоциативное запоминающее устройство, предназначенное в данном случае для выборки и хранения широких команд. Блок 6 регистров может содержать как минимум 2•М регистров (М - число исполнительных устройств процессора) с объединенными управляющими и информационными входами, которые предназначены для хранения промежуточных результатов вычислений.

Устройство 4 управления также может быть выполнено как устройство управления 2 согласно патенту СССР 1804645 (Фиг.2) и обеспечивает передачу управления (переход) с текущей широкой команды на широкую команду по произвольному адресу.

Блок 10 может быть выполнен как в прототипе и может содержать как минимум один регистр адреса назначения, регистр маски условия (регистр, определяющий условие перехода), а также логическую схему (компаратор) проверки истинности условия перехода, причем первый вход компаратора является входом 16 блока 10, его второй вход соединен с выходом регистра маски условия, а выход компаратора соединен с управляющим входом каждого регистра адреса назначения, информационный выход которых подключен к выходу блока 10. Регистр маски может быть выполнен в виде стандартного регистра, в который по шине 17 из блока 6 через информационный вход-выход устройства 4 производится запись "0" или "1" для задания условия перехода. Информационные входы регистров адреса назначения аналогично подключены к шине 17 для занесения и хранения соответствующей адресной информации о переходе. Устройства 7-i могут содержать двунаправленный шинный формирователь, подключенный первым входом-выходом к входу-выходу 19-1, а вторым - к входу-выходу 19-2 устройства 7-i, два порта адреса (выполненные, например, как регистры), подключенные информационными входами к входу-выходу 19-2, а также сумматор адреса, подключенный входами к информационным входам портов адреса, а выходом - к входу-выходу 19-1 устройства 7-i соответственно. Двунаправленный шинный формирователь может быть выполнен в виде двух инверторов, включенных встречно-параллельно, с объединенными прямым и инверсным входами управления для обеспечения прохождения импульсов в прямом или обратном направлении. Устройства 8-i могут быть построены аналогично устройствам 7-i, за исключением шинного формирователя, который может не иметь функции двунаправленности и подключен своим информационным входом к входу-выходу 21, а информационным выходом к выходу 22 устройства 8-i соответственно.

Устройство 9 управления прологом и эпилогом конвейеризованного цикла содержит блок 24 фиксации периода эпилога конвейеризованного цикла, блок 25 фиксации момента окончания эпилога конвейеризованного цикла, блок 26 фиксации периода пролога конвейеризованного цикла, блок 27 задания режимов работы устройства. Блок 24 содержит первый, второй и третий управляющие входы 45-1, 45-2 и 45-3 соответственно, информационный вход 46, первый и второй управляющие выходы 47-1 и 47-2 соответственно. Блок 25 содержит первый, второй и третий управляющие входы 48-1, 48-2 и 49 соответственно, информационный вход 50 и управляющий выход 51. Блок 26 содержит первый, второй и третий управляющие входы 52-1, 52-2 и 52-3 соответственно, информационный вход 53 и управляющий выход 54. Блок 27 содержит информационный вход 55, управляющий вход 56 и первый и второй управляющие выходы 57-1 и 57-2 соответственно.

К управляющему входу 13 устройства 9 подключены первые управляющие входы 45-1, 48-1 и 52-1 блоков 24, 25 и 26 соответственно. К информационному входу 14 устройства 9 подключены информационные входы 46, 50, 53 и 55 блоков 24, 25, 26 и 27 соответственно, вторые управляющие входы 45-2, 48-2 и 52-2 блоков 24, 25 и 26 соответственно, а также управляющий вход 56 блока 27. К выходной шине 15 устройства 9 подключены первый управляющий выход 47-1 блока 24, а также управляющие выходы 51 и 54 блоков 25 и 26 соответственно. Второй управляющий выход 47-2 блока 24 соединен с третьим управляющим входом 49 блока 25, первый управляющий выход блока 27 соединен с третьим управляющим входом 45-3 блока 24, второй управляющий выход 57-2 блока 27 соединен с третьим управляющим входом 52-3 блока 26.

Блок 24 фиксации периода эпилога конвейеризованного цикла содержит мультиплексор 28, регистр 29, сумматор 30, компаратор 31 и элемент И 32. Мультиплексор 28 имеет первый и второй информационные входы 58-1 и 58-2, а также управляющий вход 58-3 соответственно. Сумматор 30 имеет первый и второй управляющие входы 59-1 и 59-2, а также информационный вход 59-3 соответственно. Элемент И 32 имеет первый, второй, третий и четвертый управляющие входы 60-1, 60-2, 60-3 и 60-4 соответственно.

К первому управляющему входу 45-1 блока 24 подключены первый и второй управляющие входы 59-1 и 59-2 сумматора 30 и первый и второй управляющие входы 60-1 и 60-2 элемента И 32, управляющий вход 58-3 мультиплексора 28 является вторым управляющим входом 45-2 блока 24, третий управляющий вход 60-3 элемента И 32 и его выход являются соответственно третьим управляющим входом 45-3 и первым управляющим выходом 47-1 блока 24, второй управляющий выход 47-2 которого подключен к выходу компаратора 31 и четвертому управляющему входу 60-4 элемента И 32, первый информационный вход 58-1 мультиплексора 28 является информационным входом 46 блока 24, информационный выход мультиплексора 28 подключен к информационному входу регистра 29, информационный выход которого подключен к информационному входу 59-3 сумматора 30, информационный выход которого подключен к информационному входу компаратора 31 и второму информационному входу 58-2 мультиплексора 28.

Блок 25 фиксации момента окончания эпилога конвейеризованного цикла содержит мультиплексор 33, регистр 34, сумматор 35, компаратор 36 и элемент И 37. Мультиплексор 33 имеет первый и второй информационные входы 61-1 и 61-2, а также управляющий вход 61-3 соответственно. Сумматор 35 имеет первый, второй и третий управляющие входы 62-1, 62-2 и 62-3, а также информационный вход 62-4 соответственно. Элемент И 37 имеет первый, второй и третий управляющие входы 60-1, 60-2 и 60-3 соответственно.

К первому управляющему входу 48-1 блока 25 подключены первый и второй управляющие входы 62-1 и 62-2 сумматора и первый и второй управляющие входы 63-1 и 63-2 элемента И 37, выход которого является управляющим выходом 51 блока 25, ко второму управляющему 48-2 и информационному 50 входам которого подключены соответственно управляющий 61-3 и первый информационный 61-1 входы мультиплексора 33, выход которого подключен к информационному входу регистра 34, информационный выход которого подключен к информационному входу сумматора 35, информационный выход которого подключен к информационному входу компаратора 36 и второму информационному входу 61-2 мультиплексора 33, третий управляющий вход 62-3 сумматора 35 является третьим управляющим входом 49 блока 25, выход компаратора 36 подключен к третьему управляющему входу 63-3 элемента И 37.

Блок 26 фиксации периода пролога конвейеризованного цикла содержит первый и второй мультиплексоры 38 и 41 соответственно, сдвиговый регистр 39, триггер 42 и элемент И 40. Первый мультиплексор 38 имеет первый и второй информационные входы 64-1 и 64-2 и управляющий вход 64-3 соответственно. Сдвиговый регистр 39 имеет первый и второй управляющие входы 65-1 и 65-2 и информационный вход 65-3 соответственно, а также имеет первый и второй информационные выходы 66-1 и 66-2 соответственно. Элемент И 40 имеет первый, второй, третий и четвертый управляющие входы 67-1, 67-2, 67-3 и 67-4 соответственно. Второй мультиплексор 41 имеет первый и второй информационные входы 68-1 и 68-2 и управляющий вход 68-3 соответственно.

К первому управляющему входу 52-1 блока 26 подключены первый и второй управляющие входы 65-1 и 65-2 сдвигового регистра 39 и первый и второй управляющие входы 67-1 и 67-2 элемента И 40 соответственно. Ко второму управляющему входу 52-2 блока 26 подключены управляющие входы 64-3 и 68-3 первого и второго мультиплексоров 38 и 41 соответственно, к информационному входу 53 блока 26 подключены первые информационные входы 64-1 и 68-1 первого и второго мультиплексоров 38 и 41, вторые информационные входы 64-2 и 68-2 которых подключены соответственно к первому и второму информационным выходам 66-1 и 66-2 сдвигового регистра 39. Информационный вход последнего соединен с выходом первого мультиплексора 38, третий управляющий вход 67-3 и выход элемента И 40 являются соответственно третьим управляющим входом 52-3 и выходом 54 блока 26, а выход второго мультиплексора 41 подключен ко входу триггера 42, выход которого подключен к четвертому управляющему входу 67-4 элемента И 40.

Блок 27 задания режима работы содержит первый и второй регистры 43 и 44 соответственно. Информационные входы 69-1 и 70-1 регистров 43 и 44 подключены к информационному входу 55 блока 27, управляющие входы 69-2 и 70-2 регистров 43 и 44 подключены к управляющему входу 56 блока 27. Первым управляющим выходом 57-1 блока 27 является выход второго регистра 44, вторым управляющим выходом 57-2 блока 27 является выход первого регистра 43.

Синхронизация всех устройств и блоков системы осуществляется от однофазного генератора тактовой частоты, который, как и цепи синхронизации, не показан на чертежах.

Работа системы

В исходном состоянии код программы, содержащий конвейеризованный цикл, находится в оперативной памяти 2 многопроцессорной вычислительной системы. Исполнение программы начинается с загрузки широких команд из оперативной памяти 2 по шине 23 связи с оперативной памятью в один из процессоров 1-i широкого командного слова. Считанные из оперативной памяти 2 широкие команды заносятся в КЭШ память 5 широких команд. Выдача команд из КЭШ памяти 5 на информационный вход 11-1 дешифратора 3 широких команд осуществляется в порядке возрастания адресов команд. Дешифратор 3 осуществляет распаковку операций, закодированных в текущей широкой команде, в частности операций считывания и записи в память, а также операций перехода. При этом на выходной шине 12 дешифратора 3 вырабатываются высокие уровни сигналов запуска устройств 7-i считывания из оперативной памяти 2, устройств 8-i записи в оперативную память 2 и блока 10 выдачи адреса перехода соответственно, которые поступают на управляющий вход 13 устройства 9.

Если текущая широкая команда не относится к телу конвейеризованного цикла, сигналы запуска устройств 7-i, 8-i и блока 10 не блокируются устройством 9 и появляются на его выходной шине 15, разрешая выполнение соответствующих операций. В частности, при выполнении операции считывания из оперативной памяти 2 запускается одно из устройств 7-i. Высокий уровень сигнала на управляющем входе 18 данного устройства разрешает считывание адресных операндов из входных портов адреса, суммирование их в адресном сумматоре и выдачу адреса с его выхода через информационный вход-выход 19-1 устройства 7-i на шину 23. В момент поступления данных, считанных по указанному адресу из оперативной памяти 2, двунаправленный шинный формирователь переключается на прием и осуществляет передачу данных с входа-выхода 19-1 на вход-выход 19-2 устройства 7-i и последующую запись их в блок 6 для дальнейшей обработки.

При выполнении операции записи в оперативную память 2 запускается одно из устройств 8-i. Высокий уровень сигнала на управляющем входе 20 данного устройства разрешает считывание адресных операндов из входных портов адреса, суммирование их в адресном сумматоре и выдачу адреса с его выхода через информационный выход 22 устройства 8-i на шину 23. Одновременно с суммированием адреса шинный формирователь получает на свой вход из блока 6 через информационный вход-выход 21 устройства данные на запись, которые с его выхода поступают на шину 23 через информационный выход 22 устройства 8-i вслед за адресом.

Работа устройства 4 возможна в двух режимах (см. Фиг.5) в зависимости от кода операции: подготовка передачи управления или собственно передача управления. При подготовке передачи управления устройство 4 обеспечивает запись адреса перехода и маски условия, поступающих в устройство 4 с шины 17, в соответствующие регистры блока 10. При этом дальнейшее выполнение программы продолжится с декодирования следующей широкой команды в дешифраторе 3.

При выполнении операции передачи управления (перехода) устройство 4 разрешает работу блока 10. Высокий уровень сигнала на управляющем входе 16 сравнивается компаратором блока 10 со значением, находящимся в регистре маски условия. Совпадение логических уровней на входе компаратора означает истинность условия перехода. Компаратор разрешает выдачу адреса перехода с одного из регистров адресов назначения блока 10 на его выход, связанный с управляющим входом 11-2 дешифратора 3. При этом на дешифрацию поступит широкая команда по указанному адресу назначения, а дальнейшее исполнение команд пойдет в порядке возрастания адресов до следующей команды перехода.

Перед началом выполнения тела конвейеризованного цикла устройство 9 находится в следующем состоянии. В регистр 29 записано число повторений N исходного цикла по алгоритму программы. В регистр 34 записано число стадий конвейера цикла без единицы (S-1). В сдвиговом регистре 39 находится число следующего вида: бит с номером, соответствующим числу стадий S конвейера цикла, равен "1", остальные биты равны "0". Однобитовые регистры 43 и 44 содержат "1". Запись в регистры 29, 34, 39, 43 и 44 осуществляется при наличии данных на информационном входе 14 устройства 9 и высокого уровня сигнала на управляющих входах 45-2, 48-2, 52-2 и 56. Указанные регистры являются программно доступными и при помощи команд записи в регистры процессора должны быть проинициализированы в ходе работы программы до начала конвейеризованного цикла. Сигналы ЗС (запрет считываний) на выходе 47-1, КЦ (конец цикла) на выходе 51 и РЗ (разрешение записей) на выходе 54 устройства 9 до начала работы цикла имеют низкий уровень.

Широкие команды тела цикла поступают для исполнения из КЭШ памяти 5 в дешифратор 3 в порядке возрастания адресов команд. Естественный порядок исполнения команд изменяется в случае срабатывания блока 10, выдающего адрес команды, на которую выполняется передача управления (переход). В частности, в последней команде тела цикла содержится переход на первую команду тела цикла.

При декодировании команд тела цикла дешифратор 3 вырабатывает высокий уровень сигнала РЦ (режим цикла), поступающий на входы 59-1, 62-1 и 65-1 сумматоров 30, 35 и сдвигового регистра 39 соответственно. По сигналу КС (конец стадии), вырабатываемому дешифратором 3 при обнаружении команды перехода в конце тела цикла и поступающему на входы 59-2, 62-2 и 65-2 сумматоров 30, 35 и сдвигового регистра 39 соответственно, сумматоры 30 и 35 вычитают "1" из величины, находящейся в регистрах 29 и 34 соответственно, а значение в сдвиговом регистре 39 сдвигается на один бит вправо. При этом старший бит регистра 39 принимает значение "0".

По мере выполнения стадий конвейеризованнного цикла единица, записанная в исходном состоянии в разряде S сдвигового регистра 39, перемещается к младшему значащему разряду. По истечении S-1 периодов сигнала КС младший разряд сдвигового регистра 39 принимает значение "1", что соответствует окончанию периода пролога конвейеризованного цикла. В этот момент триггер 42 переключается и элемент И 40 вырабатывает на выходе 54 высокий уровень сигнала РЗ (разрешение записей). Сигнал с выхода 54 по выходной шине 15 устройства 9 поступает на управляющий вход устройств 8-i, разрешая их работу в обычном режиме по истечении периода пролога конвейеризованного цикла.

По истечении N периодов сигнала КС значение на выходе сумматора 30 становится равным "0". В этот момент, соответствующий началу периода эпилога конвейеризованного цикла, срабатывает компаратор 31 и элемент И 32 выдает высокий уровень сигнала ЗС на выходе 47-1, который с выхода 47-1 по выходной шине 15 устройства 9 поступает на управляющий вход устройств 7-i, запрещая их работу на период эпилога конвейеризованного цикла.

После срабатывания компаратора 31 начинает работать сумматор 35, который отсчитывает стадии эпилога конвейеризованного цикла. По истечении еще S-1 периодов сигнала КС значение на информационном входе компаратора 36 становится равным "0" и он срабатывает. Элемент И 37 при этом вырабатывает высокий уровень сигнала КЦ, поступающий с выхода 51 по выходной шине 15 устройства 9 на вход блока 10, который не выдает в данном случае адрес первой команды тела цикла и управление передается на команду, следующую за телом цикла. Выполнение конвейеризованного цикла заканчивается.

Таким образом, расширение функциональных возможностей системы управления конвейеризованным циклом, например, для нескольких переходов в теле цикла или нескольких параллельно работающих устройств записи и считывания оперативной памяти позволяет сохранить высокое быстродействие, так как не требует использования дополнительных критических цепей в устройстве управления, определяющих тактовую частоту процессора в составе многопроцессорной вычислительной системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФИЛЬТРАЦИИ МЕЖПРОЦЕССОРНЫХ ЗАПРОСОВ В МНОГОПРОЦЕССОРНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМАХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2189630C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для обработки адресной информации | 1977 |

|

SU744585A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для адресации буферной памяти | 1978 |

|

SU717771A1 |

| СПОСОБ И СИСТЕМА ДЛЯ АСИНХРОННОЙ ЗАГРУЗКИ МАССИВОВ ДАННЫХ | 2000 |

|

RU2166791C1 |

| Устройство для коррекции базовых регистров при стековом распределении памяти | 1976 |

|

SU557364A1 |

| Устройство для коррекции базовых регистров | 1976 |

|

SU557365A1 |

Изобретение относится к области вычислительной техники. Техническим результатом является расширение функциональных возможностей системы управления конвейеризованным циклом процессора широкого командного слова при сохранении высокой тактовой частоты. Для этого система содержит устройство управления прологом и эпилогом конвейеризованного цикла, дешифратор широких команд, блок регистров, устройства считывания из оперативной памяти, записи в оперативную память и блок выдачи адреса перехода. 4 з.п.ф-лы, 5 ил.

| US 5794029 А, 11.08.1998 | |||

| УСТРОЙСТВО И СПОСОБ ОБРАБОТКИ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НАБОРОВ КОМАНД | 1995 |

|

RU2137183C1 |

| СПОСОБ И СИСТЕМА ДЛЯ АСИНХРОННОЙ ЗАГРУЗКИ МАССИВОВ ДАННЫХ | 2000 |

|

RU2166791C1 |

| US 5950012 А, 07.09.1999 | |||

| US 5561775 A, 01.10.1996 | |||

| US 5418975 А, 23.05.1995 | |||

| US 5404472 А, 04.04.1995. | |||

Авторы

Даты

2002-06-27—Публикация

2001-06-04—Подача