ших разрядов счетчика соединены со ответственно с первым и вторым входами селектора знака, первая группа выходов которого соединена с соответствующими управляющими входами первого и второго коммутаторов, а вторая групПЙ выходов селектора знака соединена с соответствукяцнми управляющими входами третьего коммутатора, группа входов задания весовых коэффициентов преобразователя соединена с., нервой группой информационных входов третьего коммутатора и через первый блок инвертирования с его второй группой информационных входов, выходы третьего кo ф yтaтopa соединены с соответствующими аналоговыми входами первого блока цифроаналогового преобразования, выходы которого соединены с первой группой входов второго блока суммирования, выходы первого блока cy fr иpoвaния через второй блок инвертирования соединены с второй группой информационных входов первого коммутатора, выходы которого соединены с соответствующими аналоговыми входами второго блока цифроаналогового преобразования, выходы которого соединены с второй группой входов второго блока суммирования и первой группой входов третьего блока суммирования, выходы второго блока суммирования соединены с первой группой информационных входов второго коммутатора и через третий блок инвертирования - с второй группой его информационных входов, выходы второго коммутатора соединены с соответствующими аналоговыми входами третьего блока цифроаналогового преобразования, выходы которого соединены с второй группой входов третьего блока суммирования, выходы которого являются-выходами устройства.

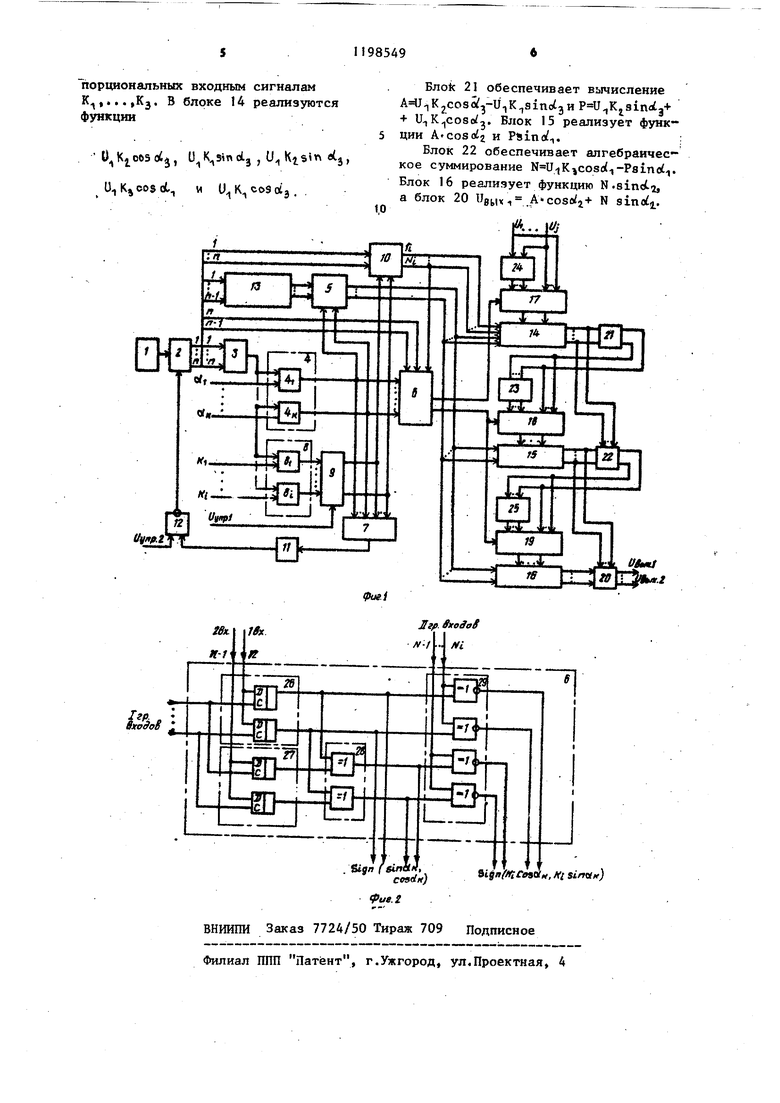

2, Преобразователь по п.1, о т - личающееся тем, что селек тор знака содержит две группыD-триггеров, группу элементов ИСКЛЮЧАКЯЦЕЕ ИЛИ и блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, при зтом входы первой группы селрктора соединены с входами синхронизации соответствующих)-триггеров первой и второй групп, информационные входы D -триггеров первой группы подключены к первому входу селектора, а информационные входы Втриггеров второй группы - к второму входу селектора, выходы каждого из 1 триггеров первой группы и соответствующего ему по номеру D-триггера второй группы соединены с входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, причем выходыD-триггеров первой группы и выходы элемен- тов ИСКЛЮЧАЮЩЕЕ ИЛИ образуют первую группу выходов селектора, каждый из входов второй группы селектора соединен с первыми входами двух соответствующих групп элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией блока, вторые входы одной из групп подключены к выходам соответствующих) -триггеров первой группы, вторые входы другой группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией подключены к выходам соответствующих элементов ИСКЛЮЧМЩЕЕ ИЛИ, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией являются второй группой выха дов селектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1312737A1 |

| Устройство для синусно-косинусного цифроаналогового преобразования | 1983 |

|

SU1278897A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

| Преобразователь угла поворота вала с контролем выходного кода | 1986 |

|

SU1334373A2 |

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

| Преобразователь угла поворота вала в код | 1990 |

|

SU1751850A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1280698A1 |

| Функциональный преобразователь угла поворота вала в код | 1978 |

|

SU748480A1 |

| Многоканальный преобразователь угла поворота вала в код | 1983 |

|

SU1120383A1 |

1. МНОГОКАНАЛЬНЫЙ НЕЛИНЕЙНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий генератор импульсов, выход которого соединен с информационным входом п- разрядного счетчика, выход которого через цифроаналоговый преобразователь соединен с первыми входами компараторов первой группы, вторые входы которых подключены к шинам задания аргументов функции преобразователя, а выходы соединены с входаьш управления записью соответствующих регистров первой группы, элемент И, элемент задержки, первый и второй коммутаторы и первый блок цифроаналогового преобразования, выходы которого соединены с входами первого блока суммирования, выходы которого соединены с первой группой информационных входов первого коммутатора отличающийся тем, что, с целью повышения быстродействия, преобразователь содержит цифровой синусно-косинусный преобразователь, вторую группу регистров, селектор знака, блок элементов Ш1И-НЕ,.элемент РЬНЕ, три блока инвертирования, третий коммутатор, второй и третий блоки суммирования, вторую группу компараторов, второй и третий блоки цифроаналогового преобразования, при этом выход цифроаналогового преобразователя соединен с первыми входами компараторов второй группы, вторые входы которых подключены к шинам задания коэффициентов преобразователя, выходы компараторов первой группы соединены с первой группой входов блока элементов Ии селектора знака, выходы компараторов второй группы соединены с первыми входами элементов ИЛИ-НЕ блока, вторые входы которых соединены с шиной задания режима преобразования преобразователя, а выходы - с второй группой входов блоS ка элементов И и входами управления записью соответствуняцих регистров (Л второй группы, выход блока элементов И через элемент задержки соединен с первым входом элемента И-НЕ, второй вход которого соединен с шиной пуска преобразователя, а выход - с входом запуска счетчика, выходы (п-1) разрядов которого подключены к входу со цифрового синусно-косинусного преобСХ) разователя, выходы которого соединеСП 4 UD ны с информационными входами регистров первой группы, которых соединены с первой группой цифровых входов первого блока цифроаналогового преобразования и соответствующими цифровыми входами второго и третьего блоков цифроаналогового преобразования, выходы регистров второй группы соединены с второй группой входов первого бло.ка цифроаналогового преобразования, выходы старших разрядов регистров второй группы соединены с второй группой входов селектора знака, выходы двух стар-

1

Изобретение относится к вычислительной технике и может быть использовано для реализации нелинейных зависимостей в управляющих системах, например манипуляционньгх роботов.

Цель изобретения - повьшение быстродействия.

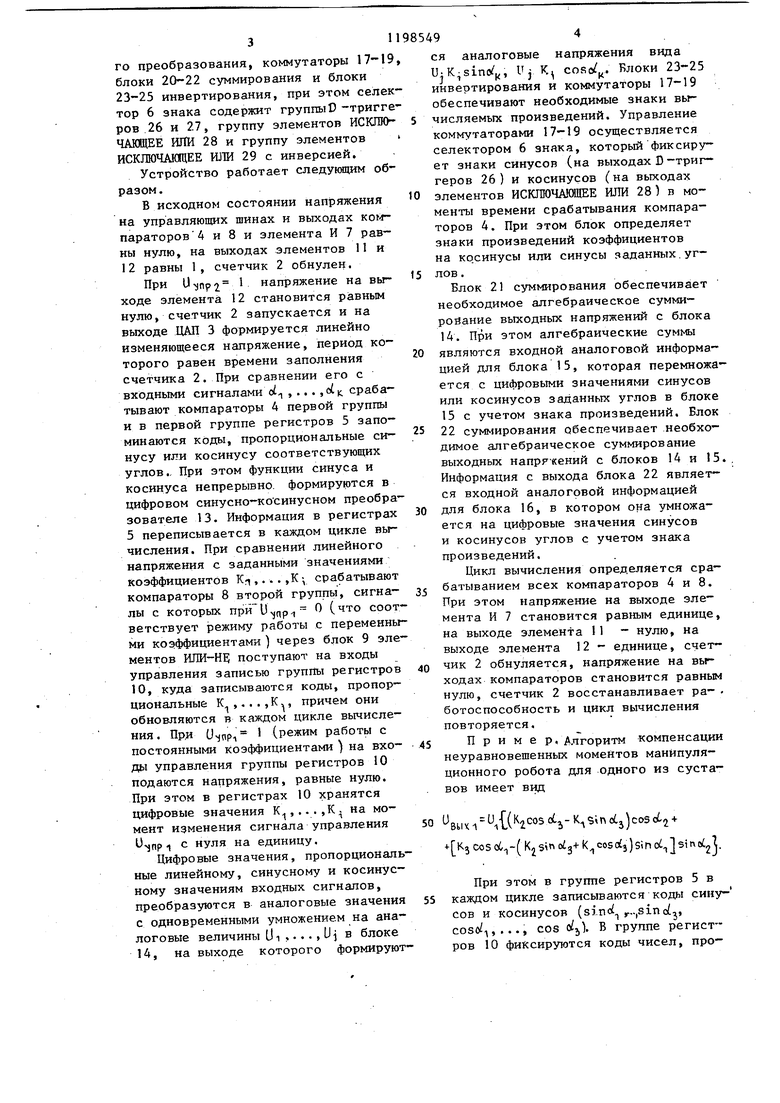

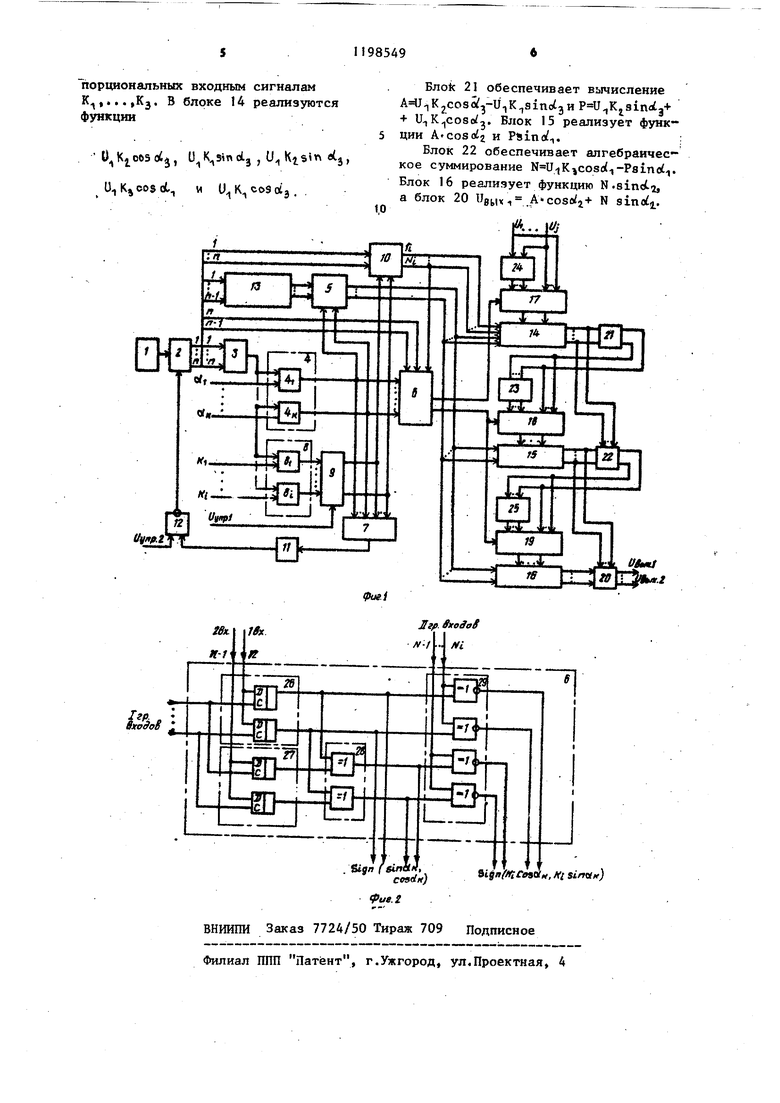

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - схема селектора знака.

Устройство содержит генератор 1 импульсов, счетчик 2, цифроаналоговый преобразователь {11АП) 3, группу компараторов 4, группу регистров 5, селектор 6 знака, элемент И 7, группу компараторов 8, блок 9.элементов ШШ-НЕ, группу регистров 10, элемент 11 задержки, элемент И-НЕ 12, цифровой синусно-косинусный преобразователь 13, блоки 14-16 цифроаналогово3го преобразования, коммутаторы 17-1 блоки суммирования и блоки 23-25 инвертирования, при этом селе тор 6 знака содержит группыD -тригг ров .26 и 27, группу элементов ИСКЛЮ ЧАЮЩЕЕ ИЛИ 28 и группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 29 с инверсией. Устройство работает следуняцим об разом. В исходном состоянии Напряжения на управляющих шинах и выходах Kotfпараторов4 и 8 и элемента И 7 равны нулю, на выходах элементов 11 и 12 равны 1, счетчик 2 обнулен. При U)np2 напряжение на выходе элемента 12 становится р;авным нулю, счетчик 2 запускается и на выходе ДАЛ 3 формируется линейно изменяющееся напряжение, период которого равен времени заполнения счетчика 2. При сравнении его с входными сигналами d ,.,.,d срабатывают компараторы 4 первой группы и в первой группе регистров 5 запоминаются коды, пропорциональные синусу или косинусу соответствующих углов.. При этом функции синуса и косинуса непрерывно, формируются в цифровом синусно-косинусном преобра зователе 13. Информация в регистрах 5 переписывается в каждом цикле вычисления. При сравнении линейного напряжения с заданными значениями коэффициентов К ,.. . ,К -, срабатывают компараторы 8 второй группы, сигналы с которых при и ,(,р -I О ( что соот ветствует режиму работы с переменны ми коэффициентами ) через блок 9 эле ментов ИЛИ-НЕ поступают на входы управления записью группы регистров 10, куда записываются коды, пропорциональные К ,...,К,, причем они обновляются в каждом цикле вычисления . ПРИ (Jvjnpi 1 (режим работы с постоянными коэффициентами ) на входы управления группы регистров 10 подаются напряжения, равные нулю. При этом в регистрах 10 хранятся цифровые значения К,...,К. на момент изменения сигнала управления U,jnp с нуля на единицу. Цифровые значения, пропорциональ ные линейному, синусному и косинусному значениям входных сигналов, преобразуются в аналоговые значения с одновременными умножением на аналоговые величины Ui,..., Ui в блоке 14, на выходе которого формируют 9 напряжения вида аналоговые cose.,. Блоки 23-25 и.: К sinW. , j г.1 v,vjo№,. инвертирования и коммутаторы 17-19 обеспечивают необходимые знаки вычисляемых произведений. Управление коммутаторами 17-19 осуществляется селектором 6 знака, который фиксирует знаки синусов (на выходах D-триггеров 26) и косинусов (на выходах элементов ИСКЛЮЧАЩЕЕ ИЛИ 28) в моменты времени срабатывания компараторов 4. При этом блок определяет знаки произведений коэффициентов на ко.синусы или синусы заданных, углов . Блок 21 суммирования обеспечивает необходимое алгебраическое сумми- ройание выходных напряжений с блока 14. При этом алгебраические суммы являются входной аналоговой информацией для блока 15, которая перемножается с цифровыми значениями синусов или косинусов заданных углов в блоке 15 с учетом знака произведений. Блок 22 суммирования обеспечивает необходимое алгебраическое суммирование выходных Hanpj-кений с блоков 14 и 15.. Информация с выхода блока 22 является входной аналоговой информацией для блока 16, в котором она умножается на цифровые значения синусов и косинусов углов с учетом знака произведений. Цикл вычисления определяется срабатыванием всех компараторов 4 и 8. При этом Напряжение на выходе элемента И 7 становится равным единице, на выходе элемента 11 - нулю, на выходе элемента 12 - единице, счетчик 2 обнуляется, напряжение на выходах компараторов становится равным нулю, счетчик 2 восстанавливает ра- ботоспособность и цикл вычисления повторяется. Приме р. Алгоритм компенсации неуравновешенных моментов манипуляционного робота для одного из суставов имеет вид () CX3S о(,-( з)Sf При этом в группе регистров 5 в каждом цикле записываются коды синусов и косинусов (sinoi ,...,sinci,, coso/д,,.., cos o/j). В группе регистров 10 фиксируются коды чисел, про- порциональных входным сигналам К,...,Кз блоке 14 реализуются функции , O Kj oOSoCj, U K sindj , U KtsSn АЗ, U KjOOSd, и U K cosotj. 5 1,0 Блой 21 обеспечивает вычисление .cosai - i K sind viP V Kj aind - + Блок 15 реализует функЦии А cos и Psino T.; Блок 22 обеспечивает апгебраичес суммирование N UiK cosot -Pstnodv Блок 16 реализует функцию N.sinciT а блок 20 1выч1 N .

| Цифроаналоговый микропроцессор | 1980 |

|

SU881760A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный аналого-цифровой процессор | 1983 |

|

SU1120375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1984-05-21—Подача