разует второй вход измерителя, цифровой выход АЦП образует второй выход-измерителя, аналоговый выход АЦП - четвертый выход измерителя.

3. Датчик по пп. 1 и Zj о т л и - ч а ю щ и и с я тем, что формирователь знака выполнен в виде формирователя импульсов знака, вход которо- го образует первый вход формирователя знака, а выход подключен к входу пятого детектора и шестого детектора, выход которого через третий аналоговый инвертор подключен к первому входу первого элемента И, вы- :ход пятого детектора подключен к первому входу второго элемента И, вторые входы первого и второго элементов И объединены и образуют второй вход формирователя знака, а выходы подключены соответственно к входу установки в О и к входу установки в 1 промежуточного триггера знака, прямой выход которого соединен с первым входом третьего элемента И, а инверсньм выход - с первым входом четвертого элемента И вторые входы третьего и четвертого элементов И объединены и образуют третий вход формирователя знака, выходы подключены соответственно к входу установки в 1 и к входу установки в О триггера знака.

Изобретение относится к электроизмерительной технике.

Цель изобретения - повышение точности и быстродействия датчика.

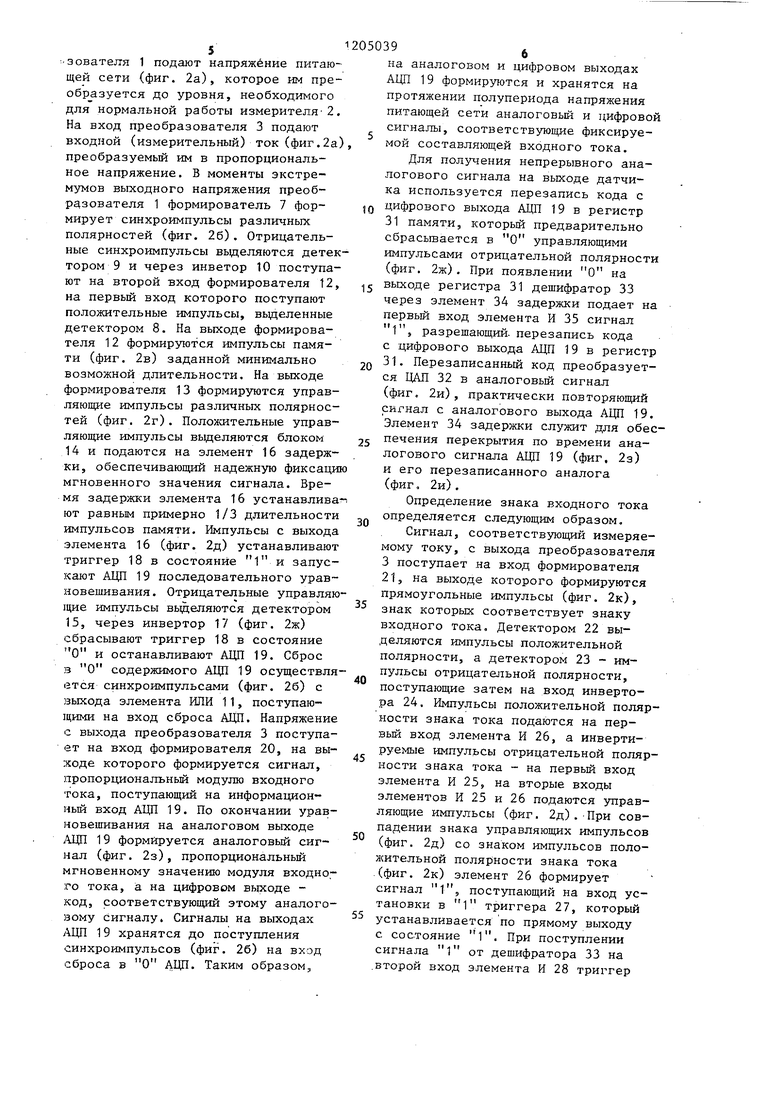

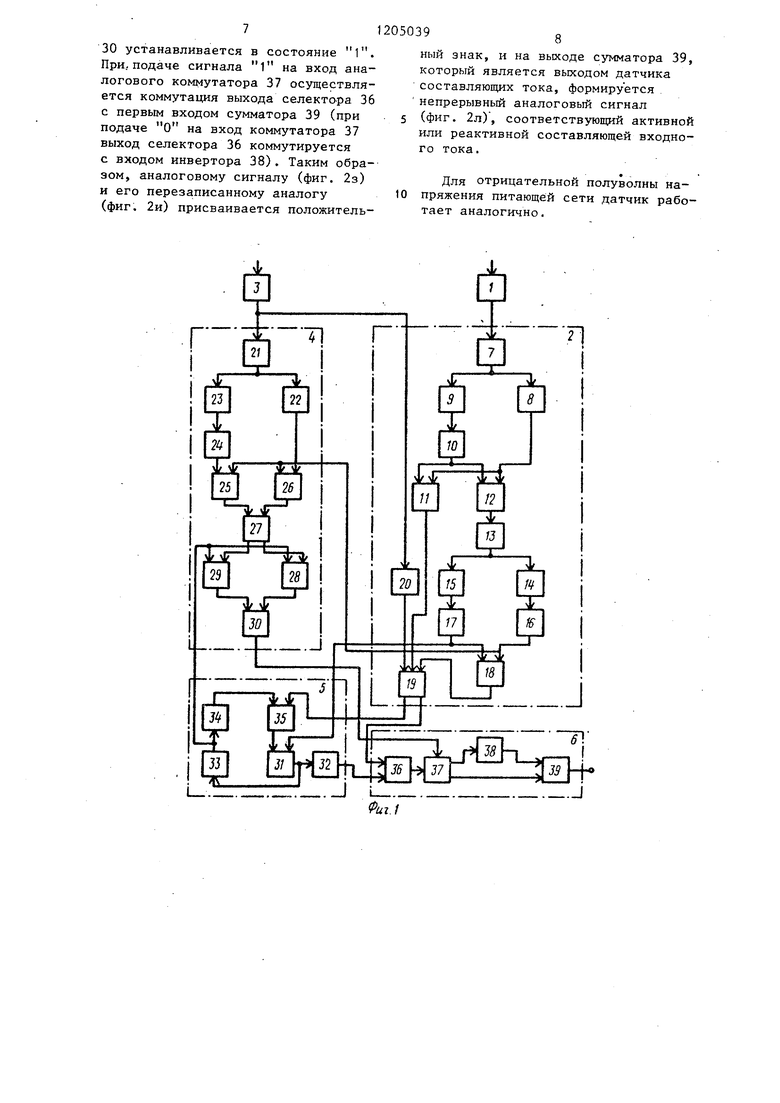

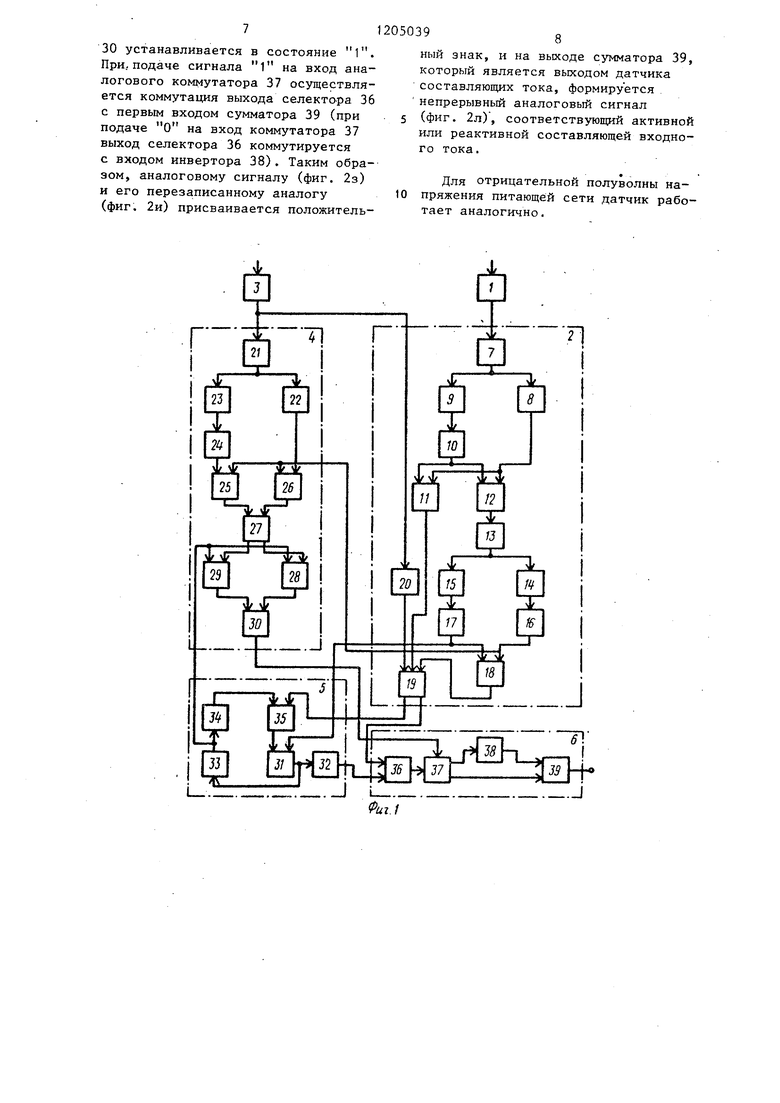

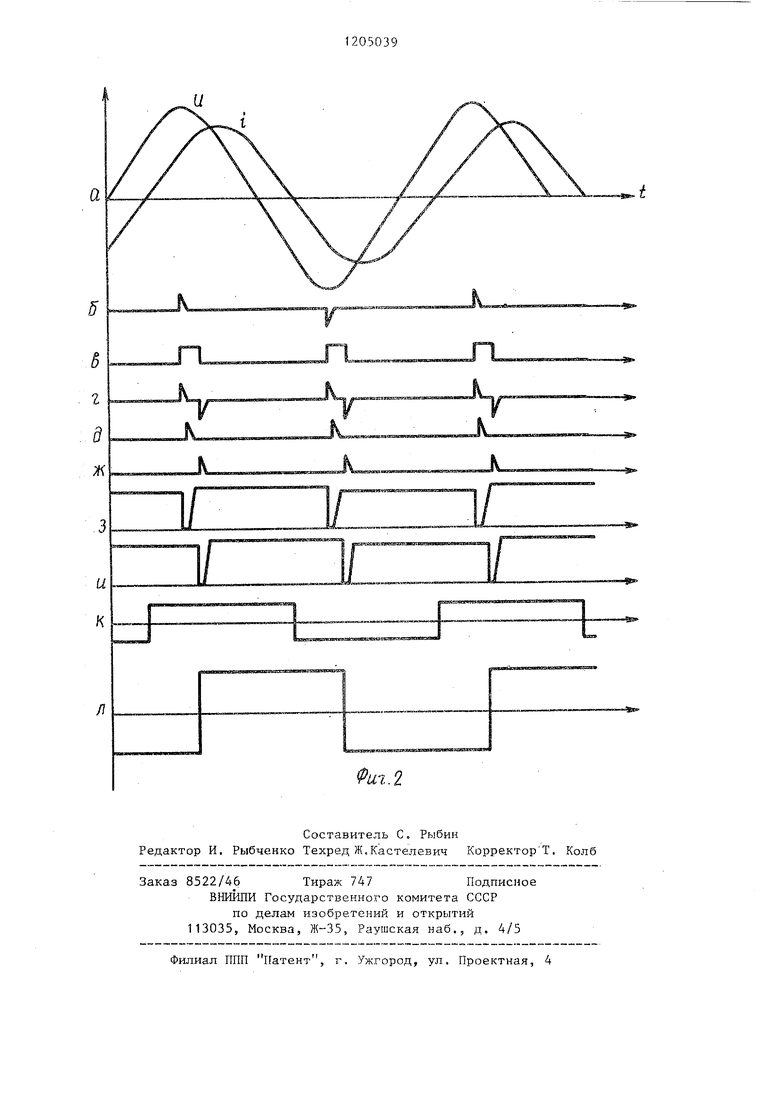

На фиг. 1 приведена блок-схема датчика; на фиг. 2 - временные диаграммы, поясняющие его работу.

Быстродействуюпгий датчик составляющих тока содержит преобразователь 1 напряжения, вход которого подключен к первому входу датчика, а выход - к первому входу «измерителя 2 мгновенного значения напряжения, второй вход которого подключен к выходу преобразователя 3 тока в напряжение и к первому входу формирователя 4 знака; вход .преобразователя 3 подвыход которого образует выход формирователя знака.

4.Датчик по пп. 1-3, отличающийся тем, что блок перезаписи кода выполнен в виде регистра памяти, первый вход которого образует второй вход блока, а выход подключен к входу цифроаналогового преобразователя (ЦАП) и к входу дешифратора, выход которого подключен к входу второго элемента задержки и образует первый выход блока, выход второго элемента задержки подключен к первому входу пятого элемента И, второй вход которого образует первый вход блока, а выход подключен к второму входу регистра, выход ЦАП образует второй выходблока

5,Датчик по пп. 1-4, о т л и - чающийся тем, что выходной блок выполнен в виде амплитудного селектора, первьш и второй входы которого образуют соответственно первый и второй входы блока, а выход подключен к входу коммутатора, управляющий вход коммутатора образует третий вход блока, первый выход коммутатора через четвертый аналоговый инвертор подключен к первому входу сумматора, к второму входу которого подключен второй выход коммутатора, выход сумматора образует выход блока.

ключен к второму входу датчика, к второму входу формирователя 4 подключен первый выход измерителя 2, а к третьему входу - первьш выход блока 5 перезаписи кода, к первому входу которого подключен второй выход измерителя 2, к второму входу - третий выход измерителя 2, а к второму выходу - первый вход выходного

блока 6j к второму входу которого подкхдачен четвертый выход измерителя 2, а к третьему входу - выход формирователя 4; выход блока 6 образует выход датчика.

Измеритель 2 мгновенного значения напряжения состоит из формирователя 7 синхронизирующих импульсов.

вход которого образует первый вход измерителя 2, а выходы подключены к входам первого 8 и второго 9 детекторов; выход детектора 9 через.-первый аналоговый инвертор 10 подклю- чен к вторым входам элемента ИЛИ 11 и формирователя 12 импульсов памяти первые входы которых подключены к выходу детектора 8, вьтход формирователя 12 через формирователь 13 управляющих импульсов подключен к входу третьего и четвертого детекторов 14 и 15, вьгходы которых подключены соответственно к входам первого элемента 16 задержки и второго аналогового инвертора 17, выход элемента 16 подключен к входу установки в 1 первого триггера 18 и образует первый выход измерителя 2, выход инвертора 17 подключен к входу установки в О триггера 18 и образует третий выход измерителя 2, выход триггера 18 подключен к тактовому входу аналого-цифрового преобразователя (АЦП) 19 последовательного уравновешивания, вход сброса которого подключен к выходу элемента ИЛИ 1 а информационньм вход - к выходу формирователя 20 модуля, вход которого образует второй вход измерителя 2, цифровой выход АЦП 19 образует второй выход измерителя 2, аналоговый выход АЦП 19 образует четвертый измерителя 2.

Формирователь 4 знака состоит из формирователя 21 импульсов знака, вход которого образует первый вход формирователя 4, а выход подключен к входу пятого детектора 22 и шестого детектора 23, выход которого чере третий аналоговый инвертор 24 подключен к первому входу первого элемента И 25, выход детектора 22 подключен к первому входу второго элемента И 26, вторые входы элементов И 25 и 26 объединены и образуют второй вход формирователя 4, выходы элементов И 25 к 26 подключены соответственно к входам установки в О и установки в 1 промежуточного триггера 27 знака, прямой выход которого подключен к первому входу третьего элемента И 28, инверсный выход - к первому входу четвертого элемента И 29; вторые входы элементов И 28 и 29 объединены и образуют третий вход формирователя 4, а выходы подключены соответственно к вхдам установки в 1 и установки в

15

20

25

с Q

50 55

205039 О

30

35

40

45

триггера 30 знака, выход которого образует выход формирователя 4 .

Блок 5 перезаписи кода состоит из регистра 31 памяти, первый вход которого образует второй вход блока 5, а выход подключен к входам цифроаналогового преобразователя (ЦАП) 32 и дешифратора 33, выход которого подключен к входу элемента 34 задержки и образует первый выход блока 5, выход элемента 34 подключен к первому входу седьмого элемента И 35, второй вход которого образует первый вход блока 5, а выход подключен к второму входу регистра 31; выход ЦАП 32 образует второй выход блока 5.

Выходной блок 6 состоит из амплитудного селектора 36, первый и второй входы которого образуют соответственно первый и второй входы блока 6, а выход подключен к входу аналогового коммутатора 37, управляю щий вход коммутатора 37 образует третий вход блока 6, первый выход коммутатора 37 через четвертый ана- логовый инвертор 38 подключен к первому входу сумматора 39, к второму входу которого подключен второй выход коммутатора 37; выход сумматора 39 образует выход блока 6.

Преобразователь 1 напряжения представляет собой трансформатор напряжения, выход которого подключен к входу двухкаскадного интегратора. Каждый из каскадов интегратора осуществляет сдвиг сигнала по фазе на 45. При фиксации активной составляющей тока интегратор отключен (сдвиг по фазе между выходным и входным напряжениями равен нулю), при фиксации реактивной составляющей интегратор включен (сдвиг по фазе .между вькодным и входным напряжениями равен 90° ) .

Преобразователь 3 тока в напряжение представляет собой трансфор- матор тока, нагруженньй на измерительный шунт.

Датчик работает следующим образом.

Предварительно, в зависимости от того, какую из составляющих тока необходимо фиксировать: активную или реактивную, соответственно от- ключают или подключают двухкаскад- ный интегратор преобразователя 1 напряжения. Зат ём на вход преобразователя 1 подают напряжение питающей сети (фиг. 2а), которое им преобразуется до уровня, необходимого для нормальной работы измерителя-2. На вход преобразователя 3 подают входной (измерительный) ток (фиг.2а), преобразуемый им в пропорциональное напряжение. В моменты экстремумов выходного напряжения преоб- рдзователя 1 формирователь 7 формирует синхроимпульсы различных полярностей (фиг. 26), Отрицательные синхроимпульсы вьщеляются детектором 9 и через инветор 10 поступают на второй вход формирователя 12, на первый вход которого поступают положительные импульсы, выделенные детектором 8. На выходе формирователя 12 формир5тотся импульсы памяти (фиг. 2в) заданной минимально возможной длительности. На выходе формирователя 13 формируются управляющие импульсы различных полярностей (фиг. 2г). Полояштельные управляющие импульсы вьщеляются блоком 14 и подаются на элемент 16 задержки, обеспечивающий надежную фиксацию мгновенного значения сигнала. Время задержки элемента 16 устанавливав ют равным примерно 1/3 длительности импульсов памяти. Импульсы с выхода элемента 16 (фиг. 2д) устанавливают триггер 18 в состояние 1 и запускают АЦП 19 последовательного уравновешивания. Отрицательные управляющие импульсы выделяются детектором 15, через инвертор 17 (фиг. 2ж) сбрасывают триггер 18 в состояние О и останавливают АЦП 19. Сброс 3 О содержимого АЦП 19 осуществляется синхроимпульсами (фиг. 26) с выхода элемента ИЛИ 11, поступающими на вход сброса АЦП. Напряжение с выхода преобразователя 3 поступает на вход формирователя 20, на выходе которого формируется сигнал, пропорциональньй модулю входного тока, поступающий на информацион- иьй вход АЦП 19. По окончании уравновешивания на аналоговом выходе /Щ1 19 формируется аналоговый сигнал (фиг. 2з), пропорциональный мгновенному значению модуля входного тока, а на цифровом выходе - код, соответствующий этому аналоговому сигналу. Сигналы на выходах АЦП 19 хранятся до поступления синхроимпульсов (фиг. 26) на вход сброса в О АЦП. Таким образом,

0

5

на аналоговом и цифровом выходах АЦП 19 формируются и хранятся на протяжении полупериода напряжения питающей сети аналоговый и цифровой сигналы, соответствующие фиксируемой составляющей входного тока.

Для получения непрерывного аналогового сигнала на выходе датчика используется перезапись кода с цифрового выхода АЦП 19 в регистр 31 памяти, который предварительно сбрасьтается в О управляющими импульсами отрицательной полярности (фиг. 2ж). При появлении О на 5 выходе регистра 31 дешифратор 33 через элемент 34 задержки подает на первьй вход элемента И 35 сигнал 1, разрешающий, перезапись кода с цифрового выхода АЦП 19 в регистр 31. Перезаписанный код преобразуется ЦАП 32 в аналоговый сигнал (фиг. 2и), практически повторяющий сигнал с аналогового выхода АЦП 19. Элемент 34 задержки служит для обеспечения перекрытия по времени аналогового сигнала АЦП 19 (фиг, 2з) и его перезаписанного аналога (фиг, 2и).

Определение знака входного тока определяется следующим образом.

Сигнал, соответств5тощий измеряемому току, с выхода преобразователя 3 поступает на вход формирователя 21, на выходе которого формируются прямоугольные импульсы (фиг. 2к), знак которых соответствует знаку входного тока. Детектором 22 выделяются импульсы положительной полярности, а детектором 23 - импульсы отрицательной полярности, поступающие затем на вход инвертора 24. Импульсы положительной полярности знака тока подаются на первый вход элемента И 26, а инвертируемые импульсы отрицательной полярности знака тока - на первый вход элемента И 25, на вторые входы элементов И 25 к 26 подаются управляющие импульсы (фиг. 2д).При совпадении знака управляющих импульсов (фиг. 2д) со знаком импульсов положительной полярности знака тока (фиг. 2к) элемент 26 формирует сигнал 1, поступающий на вход установки в 1 триггера 27, который устанавливается по прямому выходу с состояние 1. При поступлении сигнала 1 от дешифратора 33 на .второй вход элемента И 28 триггер

0

5

0

5

0

5

30 устанавливается в состояние 1. При, подаче сигнала 1 на вход аналогового коммутатора 37 осуществляется коммутация выхода селектора 36 с первым входом сумматора 39 (при подаче О на вход коммутатора 37 выход селектора 36 коммутируется с входом инвертора 38). Таким образом, аналоговому сигналу (фиг. 2з) и его перезаписанному аналогу (фиг. 2и) присваивается положитель

8

ный знак, и на выходе сумматора 39, который является выходом датчика составляющих тока, формируется непрерывный аналоговый сигнал (фиг. 2л), соответствующий активной или реактивной составляющей входного тока,

Для отрицательной полуволны на- пряжения питающей сети датчик работает аналогично.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Цифровой измеритель электрической энергии | 1990 |

|

SU1749842A1 |

| Устройство для анализа ритма сердца | 1986 |

|

SU1553049A1 |

| Устройство для симметрирования токов трехфазных четырехпроводных сетей | 1990 |

|

SU1758773A1 |

| Устройство для считывания информации с магнитного носителя | 1990 |

|

SU1739385A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭРЦИТИВНОЙ СИЛЫ МАГНИТНЫХ МАТЕРИАЛОВ | 2001 |

|

RU2186381C1 |

| Устройство для распознавания образов | 1986 |

|

SU1361589A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

Л

г

д ж

А.

и

к

Составитель С. Рыбин Редактор И. Рыбченко Техред Ж.Кастелевич Корректор .

Заказ 8522/4() Тираж 747Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| Датчик составляющих синусоидальной электрической величины | 1980 |

|

SU868604A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Потаповский И.Б | |||

| и др | |||

| Датчик составляющих синусоидального тока | |||

| - Промьшшенная энергетика, 1978, № 10, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-01-15—Публикация

1983-07-19—Подача