ходом третьего регистра аргументов, второй информационный вход второго сумматора-вычитателя соединен с выходом четвертого сумматора-вычитаИзобретение относится к вычислительной технике и предназначено для построения на его основе специализированных ЦВМ.

Цель изобретения - расширение функциональных возможностей за счет вычисления модуля трехмерного вьпсо- да за один цикл работы устройства, что приводит к повьшению быстродействия вычислений.

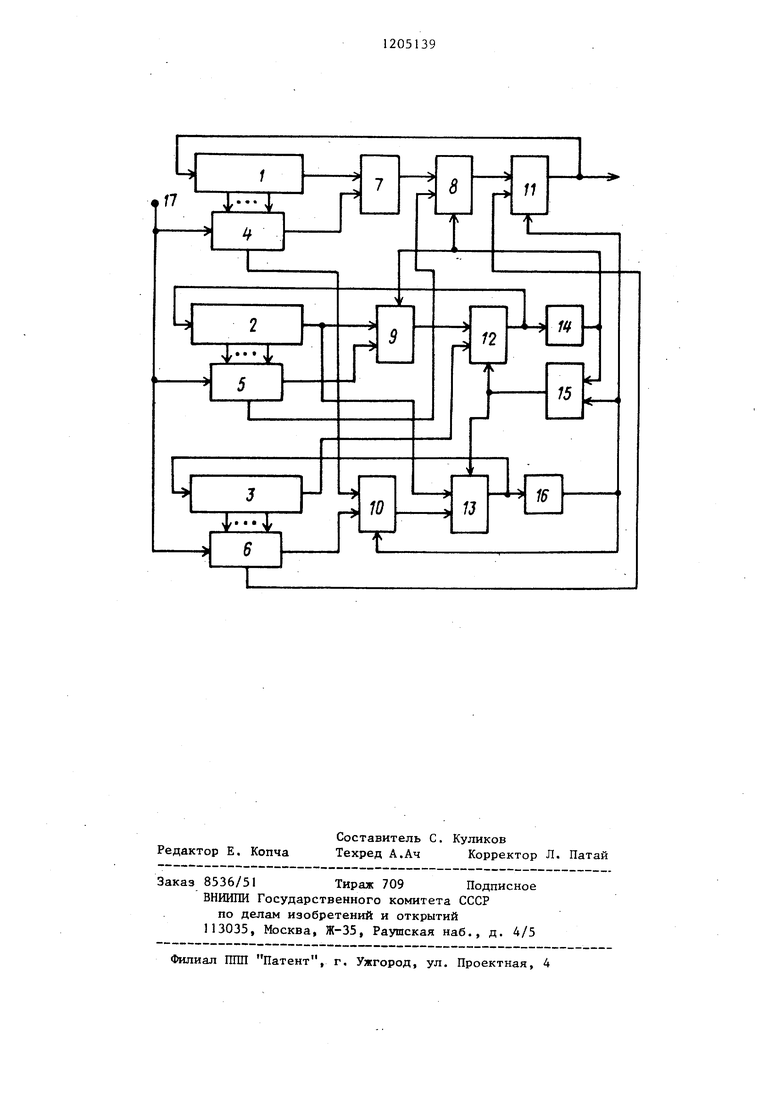

На чертеже изображена схема устройства.

Устройство содержит регистры 1-3 аргументов, сдвигатели 4-6, вычита- тель 7, сумматоры-вычитатели 8-13, дешифраторы 14-16 знака операнда и вход 17 номера итерации устройства

С первого выхода сдвигателей получается число, сдвинутое на () разрядов, а с второго выхода - на i разрядов.

Работу устройства можно описать следующими выражениями:

X;,,x;(u2-2-,y.2-i.,,.2- y; У;„ 12- -у;2-2 --. Z,,,Xi2-Vry, У;, .

Перед началом итерационного процесса значения координат X, y,Z находятся в регистрах 1-3 соответственно. С началом очередной итерации

теля, управляющий вход которого соединен с управляющим входом шестого сумматора-вычитателя и выходом треть его дешифратора знаков операндов.

5

0

5

на вход 17 устройства подается сигнал, соответствующий ее номеру, по которому .сдвигатели 4-6 настраиваются таким образом, чтобы с их первого выхода снималось число (х, у или Z), сдвинутое на (2i+1 ) разря- дов, а с второго - на i разрядов. При этом с выхода вычитател я 7 получается значение Л; (1 - 2 ), с выхода сумматора-вычитателя 8 - значение х j (1 - 2 ) + Lj; 2 , а с выхода сумматора-вычитателя 11 получится значение х ;, , которое записывается в регистр 1 вместо числа х, , Аналогичным образом с выходов сумма- торов-вычитателей 12 и 13 получаются значения у; , , которые записываются в регистры 2 и 3, а также анализируются дешифраторами 14 и 16. Дешифратор 15 служит для определения значений - jf I , , по которым в следующей итерации сумматоры-вычитатели 12 и 13 настраиваются на выполнение сложения или вычитания. После выполнения п итераций (где п - разрядность операндов) исходный вектор совпадет с осью X, и в регистре 1 записывается значение

30

7

где (1+2)- деформация модуля.

Редактор Е. Копча

Составитель С. Куликов

Техред А.Ач Корректор Л. Патай

Заказ 8536/51 Тираж 709 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| МАТРИЧНЫЙ СПЕЦПРОЦЕССОР | 1994 |

|

RU2079879C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ M-МЕРНОГО ВЕКТОРА | 1992 |

|

RU2029356C1 |

| Устройство для определения модуля трехмерного вектора | 1986 |

|

SU1388854A2 |

| Устройство для определения модуля трехмерного вектора | 1983 |

|

SU1142830A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ M-МЕРНОГО ВЕКТОРА | 1995 |

|

RU2080650C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1397904A1 |

Авторы

Даты

1986-01-15—Публикация

1984-06-07—Подача