Изобретение относится к вычислительной технике, а именно к устройствам нахождения функций путем вычислений, и может быть использовано в специализированных вычислителях для решения задач, содержащих координатные преобразования в пространстве.

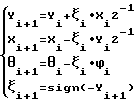

Известно арифметическое устройство, работающее по алгоритму Волдера [1] состоящее из трех буферных регистров, двух счетчиков, трех арифметических узлов и умножителя: (1) где Xi, Yi, θi значение координат и угла на i-й итерации;

(1) где Xi, Yi, θi значение координат и угла на i-й итерации;

ζi оператор направления вращения;

i=1,2,n.

Результатом вычисления является значение

R=K (2) где k коэффициент деформации модуля.

(2) где k коэффициент деформации модуля.

Недостатком данного устройства является увеличение времени вычислений модуля трехмерного вектора, который может быть определен за две операции типа (2):

R=  (3) что ведет к уменьшению области применения указанного устройства в вычислительных системах, работающих в режиме реального времени. Наиболее близким к изобретению является устройство для определения трехмерного вектора [2] Оно содержит три регистра, три коммутатора, блок изменения знака, дешифратор и три арифметических блока, каждый из которых содержит два вычитателя и два сумматора-вычитателя.

(3) что ведет к уменьшению области применения указанного устройства в вычислительных системах, работающих в режиме реального времени. Наиболее близким к изобретению является устройство для определения трехмерного вектора [2] Оно содержит три регистра, три коммутатора, блок изменения знака, дешифратор и три арифметических блока, каждый из которых содержит два вычитателя и два сумматора-вычитателя.

Данное устройство позволяет вычислить модуль трехмерного вектора (3) в виде одной макрооперации (при вычислении на устройстве не требуется определения и задания операций низкого уровня, например сложений и сдвига).

Недостатком данного устройства для определения трехмерного вектора является отсутствие возможности вычислить направляющие косинусы вектора в рамках единого неразрывного вычислительного процесса, что ограничивает функциональные возможности данного устройства, и реализация указанной операции ведет к увеличению времени расчета.

Техническим результатом заявленного устройства является расширение функциональных возможностей при решении задач, содержащих большое количество координатных преобразований, а именно дополнительная возможность вычисления направляющих косинусов вектора, которое выполняется в виде одной макрооперации, причем результат не нуждается в коррекции за счет введения узла оперативной памяти узла постоянной памяти, двух коммутаторов и блока управления. Тем самым разработана система управления, реализующая новый алгоритм работы устройства определения модуля трехмерного вектора. Это позволяет повысить производительность при вычислении координатных преобразований и упрощает управление самим устройством, повышает удобство и надежность его программирования при незначительном увеличении объема оборудования.

Сущность изобретения заключается в том, что в устройство для определения модуля трехмерного вектора, содержащее три регистра, три коммутатора, блок изменения знака, дешифратор и три арифметических блока, каждый из которых содержит два вычитателя и два сумматора-вычитателя, причем первый и второй входы первого вычитателя i-го арифметического блока (i=1,3) являются первым и вторым информационными входами i-го арифметического блока, выход первого сумматора-вычитателя i-го арифметического блока соединен с первым входом второго сумматора-вычитателя блока, выход которого является выходом i-го арифметического блока, пятый информационный вход которого соединен с вторым входом второго сумматора-вычитателя блока, управляющие входы первого и второго сумматоров-вычитателей блока являются первым и вторым знаковыми входами i-го арифметического блока, первый выход первого регистра соединен с первым информационным входом первого арифметического блока, второй и пятый информационные входы которого соединены соответственно с первым выходом первого коммутатора и первым выходом третьего коммутатора, выход первого арифметического блока соединен с первым информационным входом первого регистра, вторые выходы первого, второго и третьего регистров соединены соответственно с информационными входами первого, второго и третьего коммутаторов, выход второго арифметического блока соединен с информационным входом блока изменения знака, первый выход третьего коммутатора соединен с вторым информационным входом третьего арифметического блока, введены блок памяти констант, четвертый и пятый коммутаторы, блок управления и блок памяти, причем третий и четвертый информационные входы i-го арифметического блока соединены с первым и вторым входами второго вычитателя блока, выходы первого и второго вычитателей которого соединены с первым и вторым входами первого сумматора-вычитателя блока, первый выход первого коммутатора соединен с пятым информационным входом третьего арифметического блока, с первым информационным входом второго арифметического блока, второй и третий информационные входы которого соединены соответственно с вторым выходом первого коммутатора и первым выходом третьего регистра, управляющий вход которого соединен с управляющими входами первого и второго регистров и первым выходом блока управления, второй выход которого соединен с управляющими входами блока памяти, четвертого и пятого коммутаторов, первый информационный вход четвертого коммутатора соединен с выходом блока изменения знака и информационным входом второго регистров, первый выход которого соединен с третьим информационным входом третьего арифметического блока, первый информационный вход которого соединен с вторым выходом третьего коммутатора, первый выход которого соединен с четвертым информационным входом второго арифметического блока, пятый информационный вход которого соединен с четвертым информационным входом первого арифметического блока, четвертым информационным входом третьего арифметического блока и первым выходом второго коммутатора, второй выход которого соединен с третьим информационным входом первого арифметического блока, второй знаковый вход которого соединен с выходом пятого коммутатора, первым знаковым входом второго арифметического блока, вторым знаковым входом третьего арифметического блока, вторым информационным входом блока памяти и вторым входом дешифратора, выход которого соединен с первым знаковым входом третьего арифметического блока, выход которого соединен с информационным входом третьего регистра и первым информационным входом пятого коммутатора, второй информационный вход которого соединен с первым выходом блока памяти, второй выход которого соединен с вторым информационным входом четвертого коммутатора, выход которого соединен с первым знаковым входом первого арифметического блока, управляющим входом блока изменения знака, вторым знаковым входом второго арифметического блока, первым входом дешифратора и первым информационным входом блока памяти, вход номера итерации которого соединен с управляющими входами первого, второго и третьего коммутаторов и третьим выходом блока управления, вход которого соединен с входом режима работы устройства, выход блока памяти констант соединен с вторым информационным входом первого регистра.

На фиг. 1 представлена функциональная схема устройства; на фиг.2 схема арифметического узла; на фиг.3 схема блока управления.

Устройство для определения модуля трехмерного вектора (фиг.1) содержит блок 1 памяти констант, первый регистр 2 и коммутатор 3, вторые регистр 4 и коммутатор 5, третьи регистр 6 и коммутатор 7, блок 8 управления, с первого по третий арифметические блоки 9-11, блок 12 памяти, блок 13 изменения знака, четвертый коммутатор 14, дешифратор 15 и пятый коммутатор 16, а также вход 17 режима устройства.

Арифметический блок (фиг.2) содержит два вычитателя 18 и 19 и два сумматора-вычитателя 20 и 21.

Первый выход первого регистра 2 соединен с первым информационным входом первого арифметического блока 9, второй и пятый информационные входы которого соединены соответственно с первым выходом первого коммутатора 3 и первым выходом третьего коммутатора 7, а выход соединен с первым информационным входом первого регистра 2. Вторые выходы первого 2, второго 4 и третьего 6 регистров соединены соответственно с информационными входами первого 3, второго 5 и третьего 7 коммутаторов. Выход второго арифметического блока 10 соединен с информационным входом блока 13 изменения знака. Первый выход третьего коммутатора 7 соединен с вторым информационным входом третьего арифметического блока 11, первый выход первого коммутатора 3 соединен с пятым информационным входом третьего арифметического блока 11, с первым информационным входом второго арифметического блока 10, второй и третий информационные входы которого соединены соответственно с вторым выходом первого коммутатора 3 и первым выходом третьего регистра 6. Управляющий вход регистра 6 соединен с управляющими входами первого 2 и второго 4 регистров и первым выходом блока 8 управления, второй выход которого соединен с управляющими входами блока 12 памяти, четвертого 14 и пятого 16 коммутаторов. Первый информационный вход четвертого коммутатора 14 соединен с выходом блока 13 изменения знака и информационным входом второго регистра 4, первый выход которого соединен с третьим информационным входом третьего арифметического блока 11. Первый информационный вход последнего соединен с вторым выходом третьего коммутатора 7, первый выход которого соединен с четвертым информационным входом второго арифметического блока 10. Пятый информационный вход блока 10 соединен с четвертым информационным входом первого арифметического блока 9, четвертым информационным входом третьего арифметического блока 11 и первым выходом второго коммутатора 5, второй выход которого соединен с третьим информационным входом первого арифметического блока 9. Второй знаковый вход блока 9 соединен с выходом пятого коммутатора 16, первым знаковым входом второго арифметического блока 10, вторым знаковым входом третьего арифметического блока 11, вторым информационным входом блока 12 памяти и вторым входом дешифратора 15, выход которого соединен с первым знаковым входом третьего арифметического блока 11. Выход блока 11 соединен с информационным входом третьего регистра 6 и первым информационным входом пятого коммутатора 16, второй информационный вход которого соединен с первым выходом блока 12 памяти. Второй выход последнего соединен с вторым информационным входом четвертого коммутатора 14, выход которого соединен с первым знаковым входом первого арифметического блока 8, управляющим входом блока 13 изменения знака, вторым знаковым входом второго арифметического блока 10, первым входом дешифратора 15 и первым информационным входом блока 12 памяти. Вход номера итерации блока 12 соединен с управляющими входами первого 3, второго 5 и третьего 7 коммутаторов и третьим выходом блока 8 управления, вход которого соединен с входом 17 режима работы устройства. Выход блока 1 памяти констант соединен с вторым информационным входом первого регистра 2.

Первый и второй входы первого вычитателя 18 i-го арифметического блока (i= 1,3) являются первым 22 и вторым 23 информационными входами i-го арифметического блока. Выход первого сумматора-вычитателя 20 i-го арифметического блока соединен с первым входом второго сумматора-вычитателя 21 блока, выход которого является выходом 29 i-го арифметического блока. Пятый информационный вход 26 последнего соединен с вторым входом второго сумматора-вычитателя 21 блока. Управляющие входы первого 20 и второго 21 сумматоров-вычитателей блока являются первым 27 и вторым 28 знаковыми входами i-го арифметического блока. Третий 24 и четвертый 25 информационные входы i-го арифметического блока соединены с первым и вторым входами второго вычитателя 19 блока, выходы первого 18 и второго 19 вычитателей которого соединены с первым и вторым входами первого сумматора-вычитателя 20 блока.

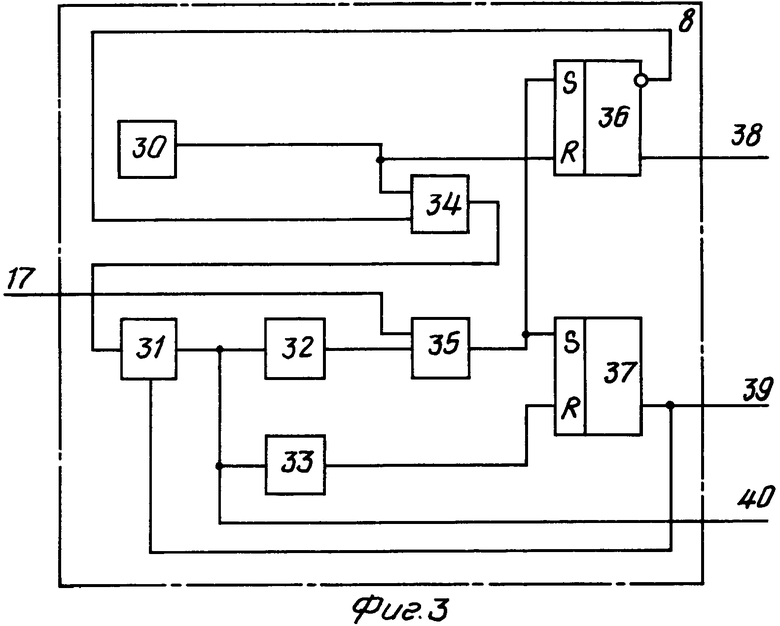

Блок 8 управления (фиг.3) состоит из генератора 30 импульсов, счетчика 31, двух дешифраторов 32 и 33, двух схем И 34 и 35, двух триггеров 36 и 37. Кроме того, имеются первый 38 и второй 39 управляющие выходы блока управления, выход 40 номера итерации и вход 17 режима.

Выход генератора 30 импульсов соединен с входом сброса первого триггера 36 и первым входом первой схемы И 34, выход которой соединен со счетным входом счетчика 31, выход которого соединен с входами первого 32 и второго 33 дешифраторов и с выходом 40 номера итерации. Выход первого дешифратора 32 соединен с вторым входом второй схемы И 35, выход которой соединен с входами установки первого 36 и второго 37 триггеров. Выход второго дешифратора 33 соединен с входом сброса второго триггера 37. Прямой выход первого триггера 36 соединен с первым управляющим входом 38 блока 8 управления, инверсный выход первого триггера 36 соединен с вторым входом схемы И 34. Выход второго триггера 37 соединен с управляющим входом счетчика 31 и вторым управляющим выходом 39. Вход 17 режима соединен с первым входом второй схемы И 35.

Устройство функционирует следующим образом.

Работа устройства выражается зависимостями (4) где i 1.n;

(4) где i 1.n;

μi sign Yi;

εi sign Zi;

X1 X, Y1 Y, Z1 Z,

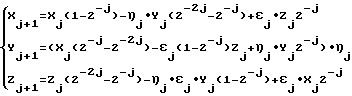

и (5) где j n.1;

(5) где j n.1;

ηj μj;

εj εj;

X1 1/k, Y1 0, Z1 0,

k  (1-2-1+2-2i) коэффициент деформации.

(1-2-1+2-2i) коэффициент деформации.

Система управления реализует вычисление двух функций.

Вычисление функции определения модуля вектора происходит по зависимости (4). Вычисление направляющих косинусов производится последовательно по зависимостям (4) и (5).

Начальными значениями координат зависимости (4) являются координаты конца заданного вектора. При расчете по зависимости (5) используются значения ε и μ полученные при расчете по зависимости (4). Значение 1/k рассчитывается заранее и хранится в блоке 1 памяти констант.

Режим работы устройства определяется наличием или отсутствием потенциала (сигнала) на входе 17. Если на нем нет сигнала, то блок 8 настраивается на расчет модуля трехмерного вектора, а при наличии сигнала на расчет направляющих косинусов трехмерного вектора.

Перед началом итерационного процесса в регистры 2, 4 и 6 соответственно заносятся значения координат конца трехмерного вектора X, Y и Z. С началом очередной итерации с выхода номера итерации блока 8 управления подается сигнал на управляющие входы коммутаторов 3, 5 и 7, настраивая их таким образом, чтобы с их первого входа снималось число (Х, Y и Z соответственно), сдвинутые на i разрядов в сторону младших разрядов, а с второго на 2i разрядов в сторону младших разрядов. Таким образом, на входы с первого по пятый аргументов арифметического блока 9 подаются Xi, Xi2-i, Yi2-2i, Yi2-i и Zi2-i, а с выхода получается значение Xi+1. Аналогично с выхода арифметического блока 11 получается значение Zi+1. С выхода арифметического блока 10 получается значение Yi+1 без учета знака μi Поэтому получаемое значение подается на информационный вход блока 13 изменения знака (на управляющий вход которого подается значение μi ), в котором происходит учет знака μiи с выхода которого получается результат Yi+1. Значения Xi+1, Yi+1 и Zi+1 записываются в регистры 2, 4 и 6 соответственно вместо значений Xi, Yi и Zi. Коммутаторы 14 и 16 передают соответственно значения знаков Zi+1 и Zi+1 на свои выходы, с которых получаются соответственно значения μi и εi Дешифратор 15 служит для получения значения μi. εi Сигнал с выхода номера итерации блока 8 управления подается также на вход номера итерации блока 12 памяти, в котором запоминаются соответствующие номеру итерации значения μi и εi подаваемые на соответствующие информационные входы этого блока. Сигнал с второго управляющего выхода блока управления настраивает блок 12 памяти на запись значений μi и εi

После выполнения n итераций (n разрядность операндов) исходный вектор совпадает с осью ОХ и в регистр 2 записывается значение

Xn=k

Если на вход 17 режима устройства подается "0", то счет на этом заканчивается. Если на вход режима подается "1", то блок 8 управления начинает обеспечивать работу устройства согласно зависимости (5). На первом управляющем выходе блока управления вырабатывается сигнал, подаваемый на управляющие входы регистров 2, 4 и 6, под воздействием которого в регистр 2 записывается значение 1/k из блока 1 памяти констант, а в регистры 4 и 6 записывается "0". Дальнейшее функционирование регистров 2, 4 и 6, коммутаторов 3, 5 и 7, арифметических блоков 9, 10 и 11, блока 13 изменения знака, дешифратора 15 соответствует описанию счета по зависимости (4). Сигнал с второго управляющего выхода блока 8 управления переключает блок 12 памяти в режим чтения записанных ранее значений μi и εi для всех номеров итераций. Этот же сигнал переключает коммутаторы 14 и 16 таким образом, что считываются инвертированные значения μi и εi с соответствующих инверсных выходов блока 12 памяти и выдаются эти значения на свои выходы в виде значений ηi и εi Номера итераций теперь уменьшаются от n до 1.

После выполнения n итераций (номер итерации равен "1") по зависимости (5) вектор единичной длины (координаты которого записаны в соответствующих регистрах 2, 4 и 6) коллереарен исходному. Таким образом, в регистре 2 записано значение X/R=cosα где R= , в регистре 4 Y/R=cosβ а в регистре 6 Z/R= cosγ т. е. в регистрах 2, 4 и 6 записаны соответствующие значения направляющих косинусов исходного вектора. Значения направляющих косинусов вектора имеют истинное значение и в дальнейшей коррекции не нуждаются.

, в регистре 4 Y/R=cosβ а в регистре 6 Z/R= cosγ т. е. в регистрах 2, 4 и 6 записаны соответствующие значения направляющих косинусов исходного вектора. Значения направляющих косинусов вектора имеют истинное значение и в дальнейшей коррекции не нуждаются.

Арифметические блоки 9, 10 и 11 функционирует следующим образом (фиг.2).

Арифметический блок обеспечивает вычисление в соответствии со следующей формулой:

Q= t1-t2-e1(t3-t4)+e2t5 (6) где t1, t2, t3, t4, t5 с первого по пятый входы аргументов арифметического блока;

Q значение результата, подаваемое на выход арифметического блока;

е1 и е2 значения, подаваемые на знаковые входы и влияющие на выполнение операций сложения-вычитания.

Сигнал на знаковом входе 27 устанавливает сумматор-вычитатель 20 в режим сложения, а сигнал на знаковом входе 28 устанавливает сумматор-вычитатель 21 в режим вычитания. На входы первого 22, второго 23, третьего 24, четвертого 25 и пятого 26 аргументов подаются соответствующие значения. Таким образом, на входы первого и второго операндов первого вычитателя 18 подаются значения первого t1 и второго t2 аргументов, а с выхода снимается значение t1-t2, которое подается на вход первого операнда сумматора-вычитателя 20. Аналогично с входа второго вычитателя 19 снимается значение t3-t4, подаваемое на вход второго операнда сумматора-вычитателя 20, с выхода которого снимается значение t1-t2-e1(t3-t4), которое подается на вход первого операнда второго сумматора-вычитателя 21. На вход второго операнда сумматора-вычитателя 21 подается значение пятого аргумента t5, а с выхода снимется значение (t1-t2)-e1(t3-t4)+e2t5, которое подается на выход 29 арифметического блока, реализуя тем самым вычисление по формуле (6).

Блок 8 управления функционирует следующим образом (фиг.3).

В начале счета триггеры 36 и 37 и счетчик 31 находятся в сброшенном состоянии. На инверсном выходе триггера 36 вырабатывается сигнал "1", который открывает схему И 34 для нахождения тактовых импульсов, вырабатываемых генератором 30 импульсов. С выхода схемы И 34 тактовые импульсы поступают на счетный вход счетчика 31, увеличивая его содержимое на "+1". Содержимое счетчика представляет собой номер итерации, выдается на вход 40 номера итерации и анализируется в дешифраторах 32 и 33. Первый дешифратор 32 проверяет равенство <<Cч31>>=n и при совпадении вырабатывает сигнал, который при наличии сигнала на входе 17 режима (что соответствует режиму расчета направляющих косинусов вектора) посредством схемы И 35 подается на входы установки триггеров 36 и 37. В этом случае импульс на прямом выходе триггера 36 сбрасывает регистры 4 и 6 в "0" и обеспечивает запись в регистр 2 значения 1/k из блока 1 памяти констант. Сигнал на выходе триггера 37 (выход 39 блока 8 управления) устанавливает счетчик 31 в режим декрементации (с каждым импульсом из счетчика вычитается "1"), переключает коммутаторы 14 и 16 и блок 12 памяти на выдачу значений знаков, заполненных ранее. По достижении <<Cч31>>=0 на выходе дешифратора 33 вырабатывается сигнал, сбрасывающий триггер 37. Осуществляется расчет косинусов вектора. Если на вход 17 режима подается "0", то сигнал, вырабатываемый дешифратором 32 при <<Cч31>>=n, блокируется схемой И 35. Расчет модуля трехмерного вектора закончен.

Применение устройства для определения модуля трехмерного вектора для нахождения функций путем вычислений, а именно для использования в специализированных вычислителях для решения задач, содержащих большое количество координатных преобразований, позволяет существенно повысить производительность при вычислении координатных преобразований и упростить управление вычислительным процессом, повышает удобство и надежность программирования работы устройства при незначительном увеличении объема оборудования, что в итоге ведет к повышению эффективности применения устройства в составе специализированного вычислителя для решения задач координатных преобразований в режиме реального времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ МАТРИЦ | 2000 |

|

RU2168760C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

| Устройство для определения модуля трехмерного вектора | 1983 |

|

SU1142830A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Вычислительное устройство | 1988 |

|

SU1522196A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СПЕКТРА | 1998 |

|

RU2125291C1 |

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

Изобретение относится к вычислительной технике и может использоваться в специализированных вычислителях для решения задач, содержащих координатные преобразования в пространстве. Устройство для определения модуля трехмерного вектора содержит первые регистр 2 и коммутатор 3, вторые регистр 4 и коммутатор 5, третьи регистр 6 и коммутатор 7, дешифратор 15, а также блок 1 памяти констант, блок 8 управления, с первого по третий арифметические узлы 9 11, блок 12 памяти, блок 13 изменения знака, четвертый коммутатор 14 и пятый коммутатор 16, вход 17 режима. За счет введения узла оперативной памяти, узла постоянной памяти, двух коммутаторов и блока управления расширяются функциональные возможности при решении задач, содержащих большое количество координатных преобразований, а именно дополнительная возможность вычисления направляющих косинусов вектора, которая выполняется в виде одной макрооперации, причем результат не нуждается в коррекции. Тем самым разработана система управления, реализующая новый алгоритм работы устройства определения модуля трехмерного вектора. Это позволяет повысить производительность при вычислении координатных преобразований и упрощает управление самим устройством, повышает удобство и надежность его программирования при незначительном увеличении объема оборудования. 3 ил.

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА, содержащее три регистра, три коммутатора, блок изменения знака, дешифратор, три арифметических блока и два сумматора-вычитателя, причем первый и второй входы первого вычитателя i-го арифметического блока (i 1,3) являются первым и вторым информационными входами i-го арифметического блока, выход первого сумматора-вычитателя i-го арифметического блока соединен с первым входом второго сумматора-вычитателя блока, выход которого является выходом i-го арифметического блока, пятый информационный вход которого соединен с вторым входом второго сумматора-вычитателя блока, управляющие входы первого и второго сумматоров-вычитателей блока являются первым и вторым знаковыми входами i-го арифметического блока, первый выход первого регистра соединен с первым информационным входом первого арифметического блока, второй и пятый информационные входы которого соединены соответственно с первым выходом первого коммутатора и первым выходом третьего коммутатора, выход первого арифметического блока соединен с первым информационным входом первого регистра, вторые выходы первого, второго и третьего регистров соединены соответственно с информационными входами первого, второго и третьего коммутаторов, выход второго арифметического блока соединен с информационным входом блока изменения знака, первый выход третьего коммутатора соединен с вторым информационным входом третьего арифметического блока, отличающееся тем, что оно содержит блок памяти констант, четвертый и пятый коммутаторы, блок управления и блок памяти, причем третий и четвертый информационные входы i-го арифметического блока соединены с первым и вторым входами второго вычитателя блока, выходы первого и второго вычитателей которого соединены с первым и вторым входами первого сумматора-вычитателя блока, первый выход первого коммутатора соединен с пятым информационным входом третьего арифметического блока, первым информационным входом второго арифметического блока, второй и третий информационные входы которого соединены соответственно с вторым выходом первого коммутатора и первым выходом третьего регистра, управляющий вход которого соединен с управляющими входами первого и второго регистров и первым выходом блока управления, второй выход которого соединен с управляющими входами блока памяти, четвертого и пятого коммутаторов, первый информационный вход четвертого коммутатора соединен с выходом блока изменения знака и информационным входом второго регистра, первый выход которого соединен с третьим информационным входом третьего арифметического блока, первый информационный вход которого соединен с вторым выходом третьего коммутатора, первый выход которого соединен с четвертым информационным входом второго арифметического блока, пятый информационный вход которого соединен с четвертым информационным входом первого арифметического блока, четвертым информационным входом третьего арифметического блока и первым выходом второго коммутатора, второй выход которого соединен с третьим информационным входом первого арифметического блока, первый знаковый вход которого соединен с выходом пятого коммутатора, первым знаковым входом второго арифметического блока, вторым знаковым входом третьего арифметического блока, вторым информационным входом блока памяти и вторым входом дешифратора, выход которого соединен с первым знаковым входом третьего арифметического блока, выход которого соединен с информационным входом третьего регистра и первым информационным входом пятого коммутатора, второй информационный вход которого соединен с первым выходом блока памяти, второй выход которого соединен с вторым информационным входом четвертого коммутатора, выход которого соединен с вторым знаковым входом первого арифметического блока, управляющим входом блока изменения знака, вторым знаковым входом второго арифметического блока, первым входом дешифратора и первым информационным входом блока памяти, вход номера итерации которого соединен с управляющими входами первого, второго и третьего коммутаторов и третьим выходом блока управления, вход которого соединен с входом режима работы устройства, выход блока памяти констант соединен с вторым информационным входом первого регистра.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-07-20—Публикация

1993-02-01—Подача