Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислителей.

Целью изобретения является расширение класса решаемых, задач за счет возможности вычисления квадратного корня комплексного переменного.

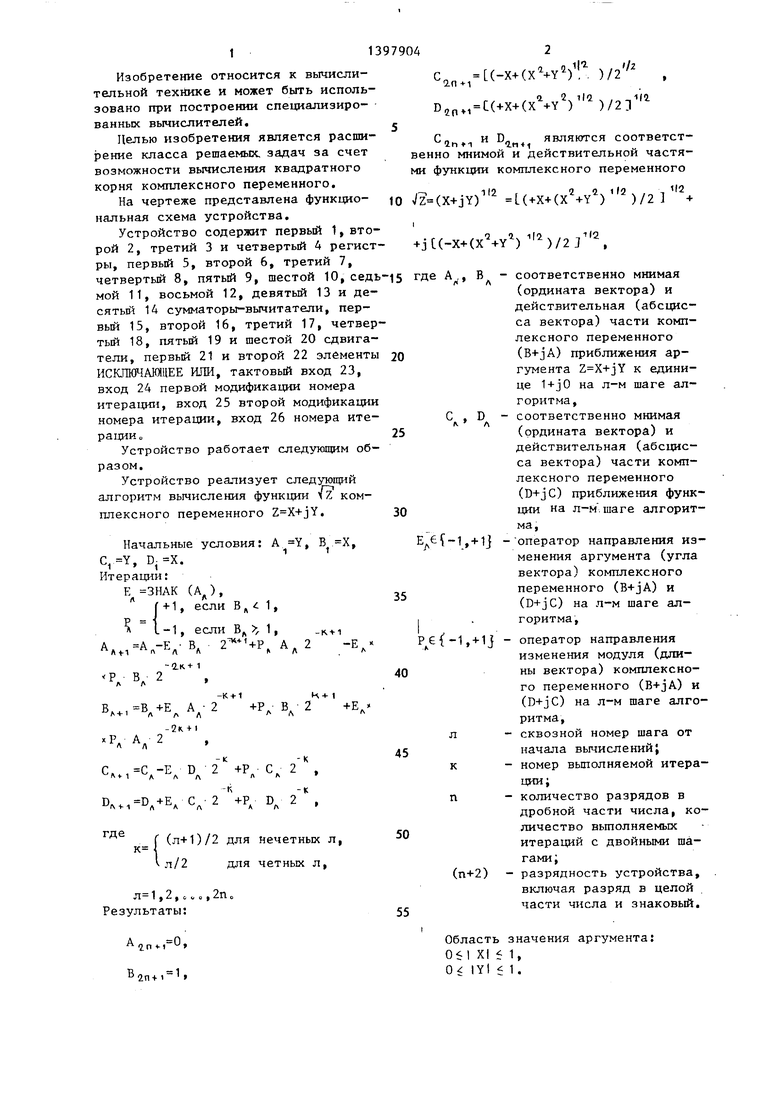

На чертеже представлена функциональная схема устройства.

Устройство содержит первый 1, второй 2, третий 3 и четвертый 4 регистры, первый 5, второй 6, третий 7, четвертый 8, пятый 9, шестой 10, сед мой 11, восьмой 12, девятый 13 и десятый 14 сумматоры-вычитатели, первый 15, второй 16, третий 17, четвертый 18, пятый 19 и шестой 20 сдвига- тали, первьй 21 и второй 22 элементы ИСКЛЮЧАМЦЕЕ ИЛИ, тактовый вход 23, вход 24 первой модификации номера итерации, вход 25 второй модификации номера итерации, вход 26 номера итерации.,

Устройство работает следующим образом.

Устройство реализует следующий алгоритм вычисления функции xZ комплексного переменного .

ап+1

(Х+(,.

)/2

/2

2, iia

C(+X+(X%Y ) )/2:i

,1(1

С... и П4,

являются соответственно мнимой и действительной частями функции комплексного переменного

10 Vz(X+jY)(.X(x4Y)/2r %

Д А,, В

.jt(-X4X%Y /2J %

Д А,, В

- соответственно мнимая (ордината вектора) и действительная (абсцисса вектора) части комплексного переменного (B+JA) приближения аргумента к единице 1+JO на л-м шаге алгоритма,

соответственно мнимая (ордината вектора) и действительная (абсцисса вектора) части комплексного переменного (D+JC) приближения функции на л-м.шаге алгорит

D

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ | 1987 |

|

SU1456954A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1987 |

|

SU1456952A1 |

| Устройство для вычисления логарифма | 1987 |

|

SU1432513A1 |

| Устройство для выполнения преобразования координат | 1987 |

|

SU1462299A1 |

| Устройство для определения модуля трехмерного вектора | 1986 |

|

SU1388854A2 |

| Вычислительное устройство | 1988 |

|

SU1508208A1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления квадратного корня комплексного переменного. Устройство содержит первый 1, второй 2, третий 3 и четвертый 4 регистры, сумматоры-вычитатели 5-14 с первого по десятый, сдвигатели 15-20 с первого по шестой, первый 21 и второй 22 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, тактовый вход 23, вход 24 первой модификации номера итерации, вход 25 второй модификации номера итерации, вход 26 номера итерации. 1 ил. (Л со :D со

Начальные условия: А Y , D-X.

Итерации:

Е ЗНАК (А),

f +1, если В -с 1,

1-1, если В , 1,

А. л л

-U.K+ 1

-К + 1

+Р. В.

АЛ,,А.-Е,- в.

Рл V 2

БЛ.

«РЛ АЛ 2

-2л + 1

D 2 +Р С

л п

-к

-к

D.,-ьE, С

2 +Р. D 2

-к

Г (л+1)/2 для нечетных л,

л/2

для четных л.

л-1,2,0 Результаты:

, ,2п,

Т-П

vrO,

2п +

1 t

, + 1J - оператор направления изменения аргумента (угла вектора) комплексного переменного (B+jA) и (D+JC) на л-м шаге алI . горитма,

P6{-1, + 1j - оператор направления

изменения модуля (длины вектора) комплексного переменного (B+jA) и (D+JC) на л-м шаге алгоритма,

л - сквозной номер шага от начала вычислений}

к - номер выполняемой итерации;

п - количество разрядов в

дробной части числа, количество вьтолняемьк итераций с двойными шагами i

(п+2) - разрядность устройства, включая разряд в целой части числа и знаковый.

Область значения аргумента: XI 1, 0 IYI 1.

Область значения функции: Oe/L (-X+(X%Y))/2 /i

/С(

0 / (-bX+(X%Y )

)/27

-JC(.

В исходном положении в регистрах находятся следующие данные: в перво регистре 1 - мнимая часть Y комплек ного аргумента Z; во втором регистр

2- действительная часть X комплексного аргумента Z; в третьем регистр

3- мнимая часть Y комплексного аргумента Z, в четвертом регистре 4 - действительная часть X комплексного аргумента Z.

Устройство работает циклически. На л-м шаге на тактовый вход 33 устройства подается синхросигнал, на вход 26 номера итерации - номер к выполняемой итерации, на вход 24 певой модификации номера итерации - код (к-1) первой модификации величи ны сдвига, на вход 25 второй модификации номера итерации - код (2к-1) второй модификации величины сдвига. При этом двум синхросигналам соотвествует одно значение номера к вьтол няемой итерации (кода величины сдвига), одно значение кода (к-1) перво модификации величины сдвига, одно значение кода (2к-1) второй модификации величины сдвига.

Значение оператора Е направления изменения аргумента комплексного пере менного снимается с выхода знакового разряда первого регистра 1, - Значение оператора Рд направлени изменения модуля комплексного переменного снимается с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21,

На выходе второго элемента ИС- КЛЮЧАКЩЕЕ ИЛИ 22 формируется сигнал

F Р -., л

В соответствии с кодом (к-1) пер- вой модификации величины сдвига в первом 15 и втором 16 сдвигателях выполняется сдвиг предьщущих значений соответственно мнимой Аи действительной В частей комплексного переменного на (к-1) разрядов вправо, т,е, на выходах первого 15 и второго 16 сдвигателей формируются вели

397904

чины

и

в f,

10

- 2

Соответственно А 2

В соответствии с кодом (2к-1) второй модификации величины сдвига в третьем 17 и четвертом 18 сдвигателях выполняется сдвиг предьщущих

значений соответственно мнимой А и

к

действительной В частей комплексного переменного на (2к-1) разрядов вправо, Тое, на выходах третьего 17 и четвертого 18 сдвигателей формируются величины соответственно А

- 5 к + 1

И в. 2

-7к-( 1

2

А В

В соответствии с кодом к величины сдвига (номером выполняемой итерации) в пятом 19 и шестом 20 сдвигателях вьтолняется сдвиг предьщущих значений соответственно мнимой С.р и действительной D частей комплексного переменного (D+jC) на к разрядов вправо, т,ео на выходах пятого 19 и шестого 20 сдвигателей формируются величины соответственно С 2 и D.

5

А В

, -к

Предьиущее значение мнимой части

приращения

А л

В,

.-IK+I

А В

поступают соответственно из первого регистра 1, первого 15, четвертого 18 и второго 16 сдвигателей в цепь, состоящую из пятого 9, третьего 7 и первого 5 сумматоров-вычи- тателей, в результате в первом сумма- торе-вычитателе 5 формируется новое значение мнимой части А , комплексно-- го переменного, которое фиксируется , в первом регистре 1„

0

5

Предьщущее значение действительной части В, приращения В 2 ,

д д 2 поступают соответственно из второго регистра 2,

второго 16, третьего 17 и первого 15 сдвигателей в цепь, состоящзто из шестого 10, четвертого 8 и второго 6 сумматоров-вычитателей, в результате во втором сумматоре-вычитателе 6 формируется новое значение действительной части В , которое фиксируется во втором регистре 2„

Предьдущее значение мнимой части

-к

-к

С, приращения С 2 , D / поступают соответственно из третьего ре«гистра 3, пятого 19 и шестого 20 сдвигателей в цепь, состоящую из седьмого 1 1 и девятого 13 сумматоров-вы читателей, в результате в девятом сумматоре-вычитателе 13 формируется новое значение мнимой части С,,

5

которое фиксируется в третьем регисре 3.

Предьщущее значение действительной части D, приращения D 2, С «2 поступают соответственно из чевертого регистра 4, шестого 20 и пятого 19 сдвигателей в цепь, состоящую из восьмого 12 и десятого 14 су маторов-вычитателей, в результате в десятом сумматоре-вычитателе 14 формируется новое значение действи

15

тельной части Сд,, которое фиксируется в четвертом регистре 4.

Все итерационные шаги выполняются в устройстве аналогично.

После вьтолнения п итераций с двойными шагами в регистрах зафиксированы следующие результаты: в первом регистре 1 A,j,0, во втором регистре 20 2 В2п-и 1. 1 третьем регистре 3 С- СС-Х+СХЧУ) - )/2Г1 , в четве ом регистре 4 П„ C(+X+(x +Y ) )/

.

Формула изобретения

Устройство для вычисления квадратного корня, содержащее два регистра, два сумматора-вычитателя, два сдвига теля, причем выходы информационных разрядов первого и второго регистров соединены с входами операндов соот- - ветственно первого и второго сдвигателей, выходы второго и первого сдвигателей соединены с входами первых операндов соответственно первого и второго сумматоров-вычитателей, выходы которых соединены с информационными входами соответственно первого и второго регистров, тактовый вход устройства соединен с синхронизирующими входами первого и второго регистров, вход первой модификации номера итерации устройства соединен с входами величины сдвига первого и второго сдвигателей, выход знакового разряда первого регистра соединен с входами выбора кода операции первого и второго сумматоров-вычитателей, отличающееся тем, что, с целью расширения класса решаемых задач за счет возможности вычисления квадратного корня комплексного переменного, в него введены третий и четвертый регистры, сумматоры-вычитате- ли с третьего по десятый, сдвигатели с третьего по шестой, первый и второ элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вхо

5

0

ды вторых операндов первого и второго сумматоров-вычитателей соединены с выходами соответственно третьего и четвертого сумматоров вычитателей, входы первых операндов которых соединены с выходами соответственно пятого и шестого сумматоров-вычитате- лей, входы вторых операндов четвертого и третьего сумматоров-вычитателей соединены с выходами соответственно третьего и четвертого сдвигателей, входы первых операндов пятого и шестого сумматоров-вычитателей соединены с выходами информационных разрядов соответственно первого и второго регистров, входы вторых операндов пятого и шестого сумматоров- вычитателей соединены С выходами соответственно первого и второго сдвигателей, выходы информационных разрядов первого и второго регистров соединены с входами операндов соответственно третьего и четвертого сдви5

5

0

5

0

рых объединены и соединены с входом второй модификации номера итерации устройства, тактовый вход устройства соединен с синхронизируюпр ми входами третьего и четвертого регистров, выходы которых соединены с входами первых операндов соответственно седьмого и восьмого сумматоров-вычитателей, выходы которых соединены с входами первых операндов соответственно девятого и десятого сумматоров-вьиита- телей, выходы которых соединены с информационными входами соответственно третьего и четвертого регистров, выходы которых соединены с входами операндов соответственно пятого и шестого сдвигателей, входы величины сдвига которых объединены и соединены с входом номера итерации устройства, выход пятого сдвигателя соединен с входами вторых операндов седьмого и десятого сумматоров-вычитателей, выход шестого сдвигателя соединен с входами вторых операндов восьмого и девятого сумматоров-вычитателей, выходы знакового и старшего информационного разрядов второго регистра соединены соответственно с первым и вторым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которо- 5 го соединен со входами выбора кода операции пятого, шестого, седьмого и восьмого сумматоров-вычитателей и с первым входом второго элемента

713979048

ИСКЛЮЧАЮЩЕЕ ИЛИ, выход знакового раз-вторым входом второго элемента ИСКЛЮ- ряда первого регистра соединен с вхо-ЧАЮЩЕЕ РШИ, выход ксторого соединен с входами выбора операции девятого и де-дами выбора кодл операции третьего и чет- сятого сумматоров-вычитателей и с свертого сумматоров- иыч татепей

| Устройство для вычисления квадратного корня | 1981 |

|

SU1007103A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Рабинович ЗсЛ., Раманаускас В.А | |||

| Типовые операции в вычислительных машинах | |||

| - К.: Техника, 1980, с.236, рис.51. | |||

Авторы

Даты

1988-05-23—Публикация

1986-11-10—Подача