входами четвертого, пятого, шестого и седьмого коммутаторов, выход первого элемента 2-2И-ИЛИ соединен с управлякяцими входами первого, второго и третьего сумматоров-вычнтателей, еди-, ничный выход третьего триггера соединен с управляющим входом четвертого сумматора-вычитателя, первый вход дешифратора соединен с выходом второго сумматора-вычитателя, второй вход дешифратора соединен с выходом третьего сумматора-вычитателя, третий вход дешифратора соединен с выходом вычитателя, разрядные выходы двоичного счетчика соединены с уиравляющими входами первого, второго и третьего коммутаторов, третий и четвертый входы второго элемента 2-2И-ИЛИ соединены с управляющими входами устройства, причем разрядные выходы четвертого сдвигового регистра соединены с информационным входом третьего коммутатора, выход которого соединен со входом элемента задержки И первым информационным входом седьмого коммутатора, выход которого соединен с первым входом операнда четвертого сутчматора-

вычитателя, выход которого соединен с первым ин(|х:1рмацион11ьгм входом шестого коммутатора и первым входом операнда вы.читателя, второй вход операнда которого соединен с выходом младшего разряда пятого сдвигового регистра и его информационным входом выход шестого коммутатора соединен с информационньм входом четвертого сдвигового регистра, выход младшего разряда которого соединен со вторым информационным входом шестого коммутатора и вторым входом операнда четвертого сумматора-вычитателя, второй информационный вход седьмого коммутатора соединен с выходом элемента задержки, выходы первого и второго коммутаторов соединены соответственно с первыми информационными входами четвертого, пятого коммутаторов и вторыми информационными входами четвертого и пятого коммутаторов , выходы четвертого и пятого коммутаторов соединены со вторыми входами операндов соответственно первого и вторрго сумматоров - вычитателей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1140117A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый, второй и третий сдвиговьге регистры, первый, второй и третий сумматоры-вычислители, первый и второй коммутаторы, причем выходы младших разрядов первого, второго и третьего сдвиговых регистров соединены с первыми входами операндов соответственно первого, второго и третьего сумматоров-вычитателей, выходы первого, второго и третьего сумматоров-вычитателей соединены с информационными входами соответственно первого, второго и третьего сдвиговых регистров, разрядные выходы первого и второго.сдвиговых регистров соединены с входами соответственно первого и второго коммутаторов, второй вход операндов третьего сумматора-вычитателя соединен с информационным входом устройства, выход первого сумматора-вычитателя соединен с информационным выходом устройства, отличающееся тем, что., с целью расширения функцирнальных возможностей устройства за счет умножения и деления координат вектора на константу, устройство содержит четвертый и пятьй сдвиговые регистры, -коммутаторы с третьего по седьмой, четвертый сумматор-вычитатель, вычитатель, элемент задеряаси и блок управления, содержащий дешифратор, первый, второй и третий триггеры, генератор тактовых импульсов, двоичный счетчик, первый и второй элементы 2-2И-ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вьгход которого соединен с нулевым входом первого триггера, единичный вход которого соединен с выходом генератора тактовых импульсов и тактовым входом двоичного счетчика, счетный вход которого соединен с еди(Л ничным выходом первого триггера, сине хронизирующим входом второго триггера и первым входом первогр элемента 2-2И-ИЛИ, второй вход которого соединен с выходом второго элемента 2-2И-ИЛИ, первьп вход которого соединен с первым выходом дешифратора, второй выход которого соединен со ьтоо: рым входом второго элемента 2-2И-ИЛИ, нулевой выход первого триггера соедио нен с третьим входом первого элемента 2-2И-ИЛИ и с синхронизирующим входом третьего триггера, единичный вход которого соединен .с третьим выходом дешифратора и с единичным входом второго триггера, единичный выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с единичным выходом третьего триггера и с четвертым входом первого элемента 2-2И-ИЛИ, причем первый единичный выход первого триггера соединен с управляющими

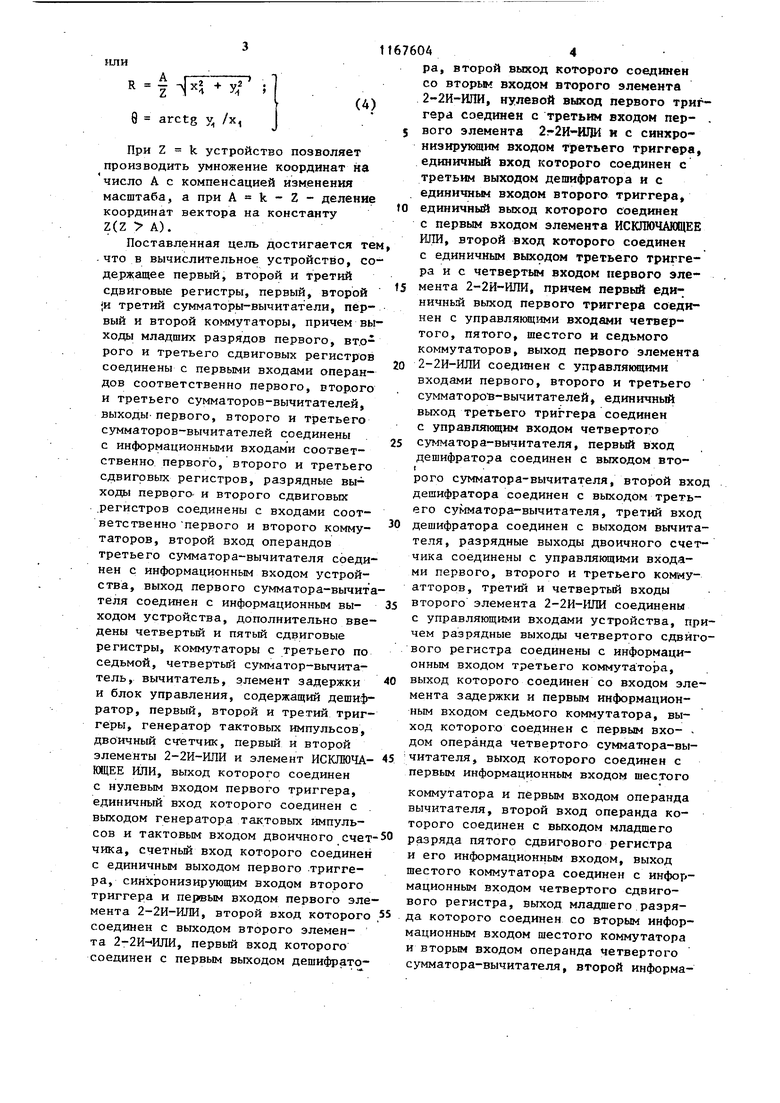

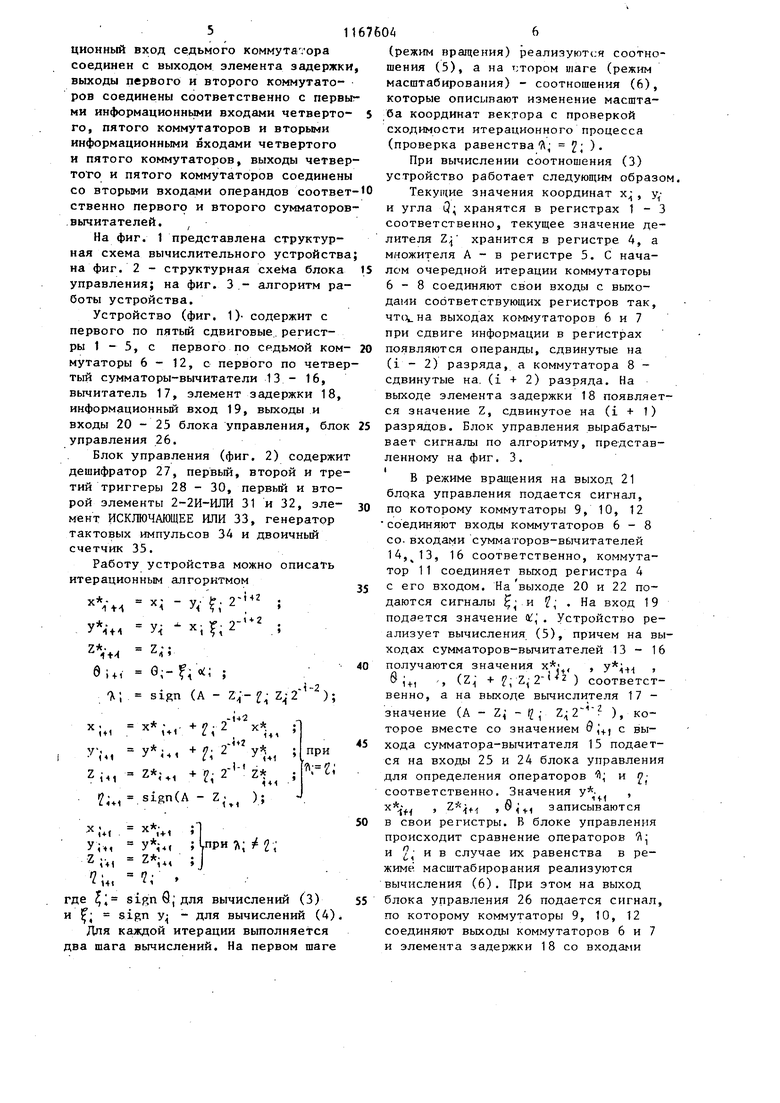

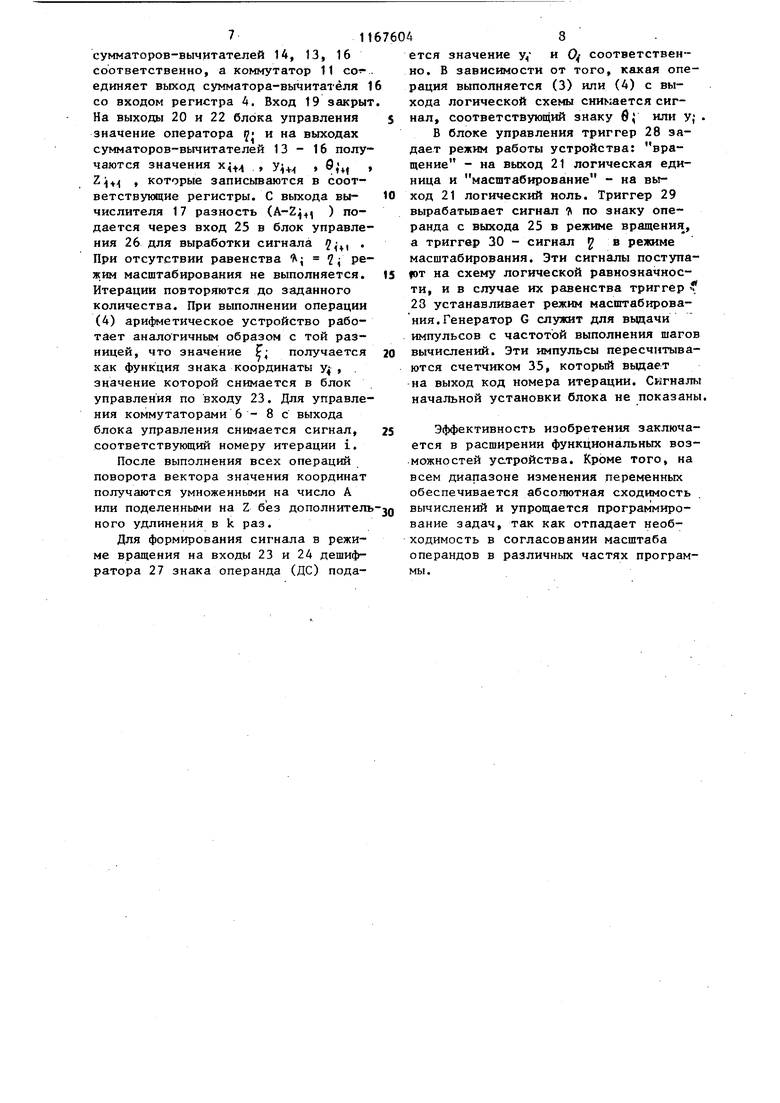

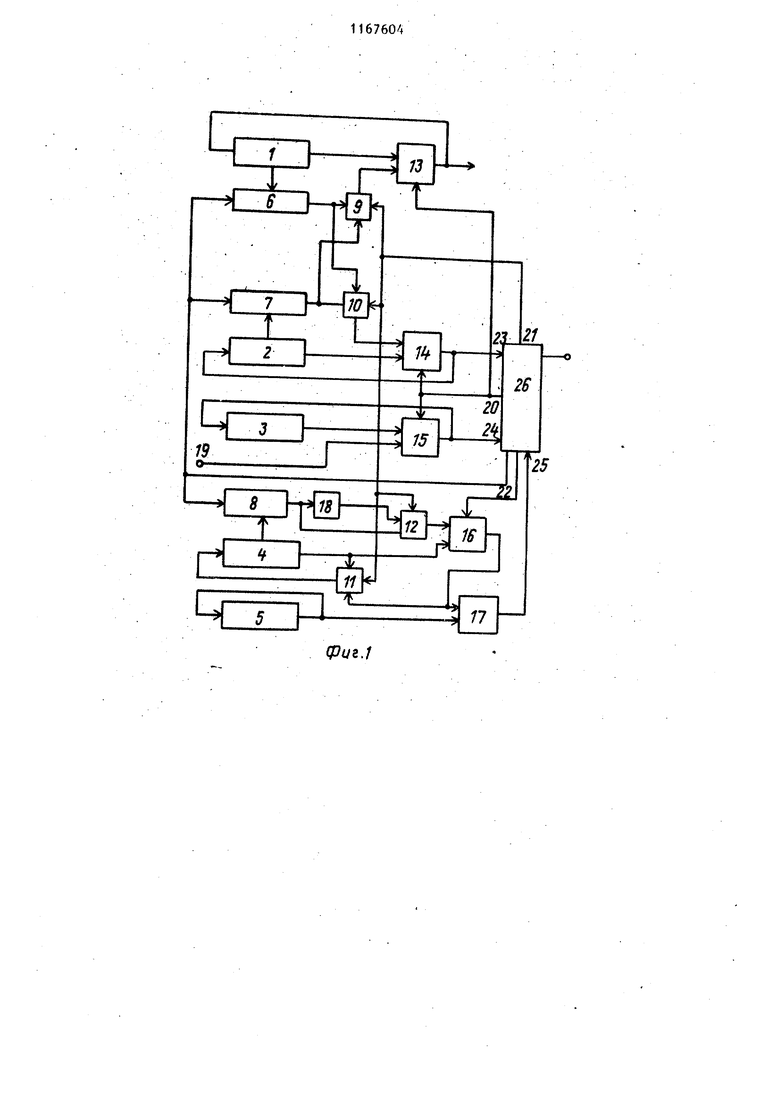

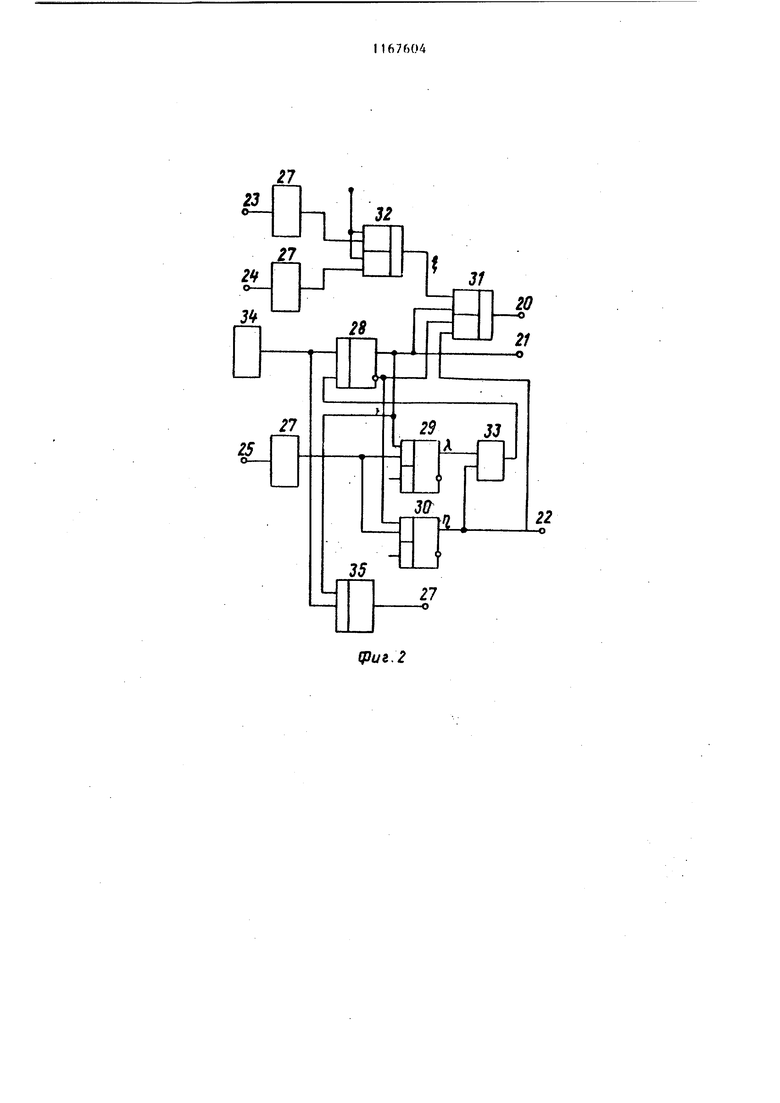

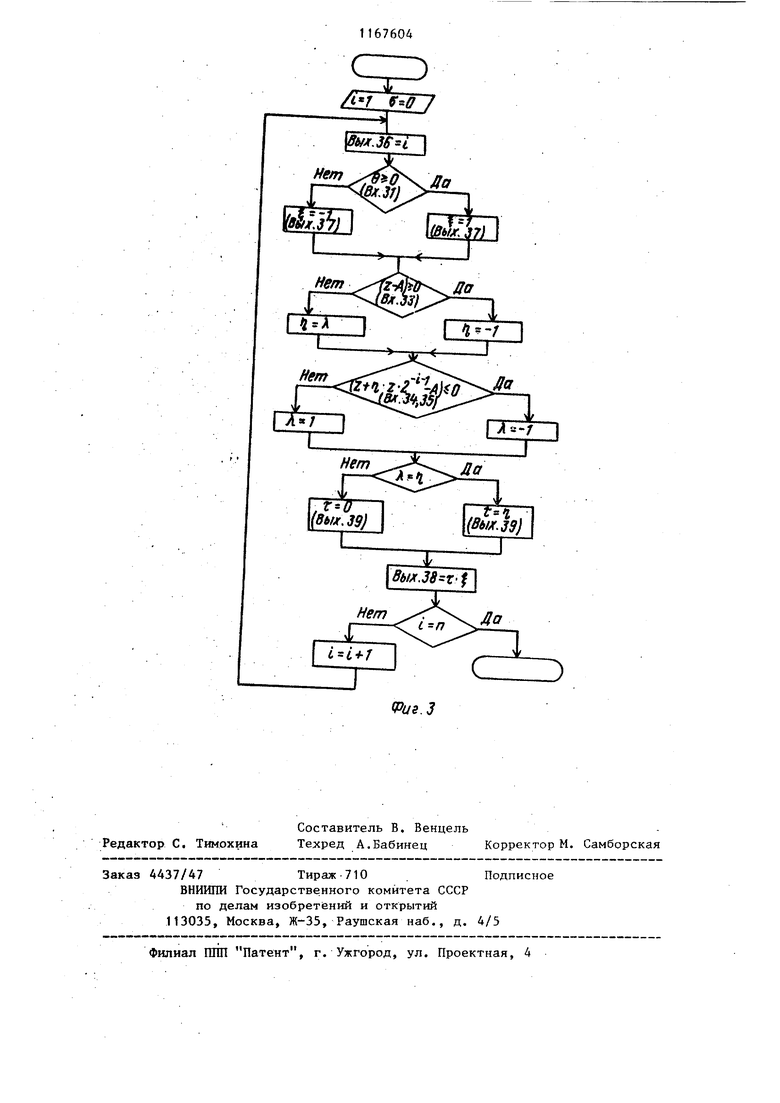

Изобретение относится к вычислительной технике и предназначено для построения на его основе специализит рованных ЦВМ. Известно арифмитическое устройств работающее с информацией, представле ной в виде векторов, предназначенное для решения задач, содержащих большо количество тригонометрических функций 01. Наиболее близким к предлагаемому по технической сущности является устройство 2, работающее по алгоритму Волдера , Уи, У; 2-;; ; х,ч, X. - ;у ;1 (1) QU, ® - ;«с; . J . где ; sign 0; для вычисления значенийу k(xj cos ) т f 2 X k(к cos kp - у sin If ) J или - sign для соотношений R - +y ; a arctg .y /x, где X; , Xj - координаты вектора, повернутые на угол Qi/i ; aCi arctg константы (i 2,3,...п). Недостатком известных устройств является изменение масштаба представления переменных (коэффициент k 1), что приводит к усложнению программирования. Целью изобретения является расширение функциональных возможностей устройства за счет вычисления выражеНИИ вида А/. , у у(у cos If + x, ); X COBS- у sin If ) J R f УQ arctg y /X, При Z k устройство позволяет производить умножение координат на число А с компенсацией изменения масштаба, а при А k - Z - деление координат вектора на константу Z(Z А). Поставленная цель достигается те .что в вычислительное устройство, со держащее первый, второй и третий сдвиговые регистры, первый, второй и третий сумматоры-вычитатели, первый и второй коммутаторы, причем вы ходы младших разрядов первого, вт.орого и третьего сдвиговых регистров соединены с первыми входами операндов соответственно первого, второго и третьего сумматоров-вычитателей, выходы- первого, второго и третьего сумматоров-вычитателей соединены с информационньми входами соответственно первого, второго и третьего сдвиговых регистров, разрядные выходы первого- и второго сдвиговых .регистров соединены с входами соответственно первого и второго коммутаторов, второй вход операндов третьего сумматора-вычитателя соеди нен с информационным входом устройства, выход первого сумматора-вычит тбля соединен с информационным выходом устройства, дополнительно вве дены четвертьй и пятый сдвиговые регистры, коммутаторы с третьего по седьмой, четверТый сумматор-вьтитатель, вычитатель, элемент задержки и блок управления, содержащий дешиф ратор, первый, второй и третий триг геры, генератор тактовых импульсов, двоичный счетчик, первый и второй элементы 2-2И-ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с нулевым входом первого триггера, единичный вход которого соединен с выходом генератора тактовых импульсов и тактовым входом двоичного сче чика, счетньй вход которого соединен с единичным выходом первого .триггера, синхронизирующим входом второго триггера и первым входом первого эле мента 2-2И-ИЛИ, второй вход которого соединен с выходом второго элемента 2-2И- ШШ, первый вход которого соединен с первым выходом дешифратоpa, второй выход которого соединен со вторым входом второго элемента 2-2И-И11И, нулевой выход первого триггера соединен с третьим входом пер- , вого элемента 2г2И-ИЛИ и с синхронизирующим входом третьего триггера, единичный вход которого соединен с третьим выходом дешифратора и с единичным входом второго триггера, единичный выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с единичным выходом третьего триггера и с четвертым входом первого элемента 2-2И-ИЛИ, причем первый единичньй выход первого триггера соединен с управляющими входами четвертого, пятого, шестого и седьмого коммутаторов, выход первого элемента 2-2И-ИЛИ соединен с управляющими входами первого, второго и третьего сумматорой-вычитателей, единичный выход третьего триггера соединен с управляющим входом четвертого сумматора-вычитателя, первый вход дешифратора соединен с выходом второго сумматора-вычитателя, второй вход дешифратора соединен с выходом третьего сумматора-вычитателя, третий вход дешифратора соединен с выходом вычитателя, разрядные выходы двоичного счетчика соединены с управляющими входами первого, второго и третьего коммуатторов, третий и четвертый входы второго элемента 2-2И-ИЛИ соединены с управляющими входами устройства, причем разрядные выходы четвертого сдвигового регистра соединены с информационным входом третьего коммутатора, выход которого соединен со входом элемента задержки и первым информационным входом седьмого коммутатора, выход которого соединен с первым вхо- дом операнда четвертого сумматора-вычитателя, выход которого соединен с первым информационным входом шестого коммутатора и первым входом операнда вычитателя, второй вход операнда которого соединен с выходом младшего разряда пятого сдвигового регистра и его информационным входом, выход шестого коммутатора соединен с информационным входом четвертого сдвигового регистра, выход младшего разряда которого соединен со вторым информационным входом шестого коммутатора и вторым входом операнда четвертого сумматора-вычитателя, второй информационный вход седьмого коммутатора соединен с выходом элемента задержк выходы первого и второго коммутаторов соединены соответственно с перв ми информационными входами четверто го, пятого коммутаторов и вторыми информационными входами четвертого и пятого коммутаторов, выходы четве того и пятого коммутаторов соединен со вторыми входами операндов соотве ственно первого и второго сумматоро вычитателей, , На фиг. 1 представлена структурная схема вычислительного устройств на фиг. 2 - структурная схеМа блока управления; на фиг. 3 - алгоритм ра боты устройства. Устройство (фиг. О- содержит с первого по пятый сдвиговые.регистры 1 - 5, с первого по СРДЬМОЙ ком мутаторы 6 - 12, с первого по четве тый сумматоры-вычитатели 13 - 16, вычитатель 17, элемент задержки 18, информационньй вход 19, выходы и входы 20 - 25 блока управления, бло управления 26. Блок управления (фиг. 2) содержи дешифратор 27, первый, второй и тре тий триггеры 28 - 30, первый и второй элементы 2-2И-ИЛИ 31 и 32, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 33, генератор тактовых импульсов 34 и двоичный счетчик 35. Работу устройства можно описать итерационным алгоритмом х- - V if. 2- У 1 , у, «- + г У - х,, 2 ; G;-f; ; ; -A; sign (A - ); ;LnpH ; 0 где sip;n Qj для вычислений (3) и j sign y - для вычислений (4), Для каждой итерации выполняется два шага вычислений. На первом шаге (режим вращения) реализуются соотношения (5), а на т;тором шаге (режим масштабирования) - соотношения (6), которые описывают изменение масштаба координат вектора с проверкой сходимости итерационного процесса (проверка равенстваД 2; ) При вычислении соотношения (3) устройство работает следующим образом. Текущие значения координат х , у,и угла Q; хранятся в регистрах 1 - 3 соответственно, текущее значение делителя хранится в регистре 4, а множителя А - в регистре 5. С началом очередной итерации коммутаторы 6-8 соединяют свои входы с выходами соответствующих регистров так, 4T(VHa выходах коммутаторов 6 и 7 при сдвиге информации в регистрах появляются операнды, сдвинутые на (i - 2) разряда, а коммутатора 8 сдвинутые на, (1+2) разряда. На выходе элемента задержки 18 появляется значение Z, сдвинутое на (i + 1) разрядов. Блок управления вырабатывает сигналы по алгоритму, представленному на фиг, 3. В режиме вращения на выход 21 блока управления подается сигнал, по которому коммутаторы 9, 10, 12 соединяют входы коммутаторов 6-8 со. входами сумматоров-вйчитателей 14,13, 16 соответственно, коммутатор 11 соединяет выход регистра 4 с его входом. На выходе 20 и 22 подаются сигналы , и Ч , На вход 19 подается значение . Устройство реализует вычисления (5), причем на выходах сумматоров-вычитателей 13 - 16 получаются значения , , у , S;+, , а , соответственно, а на выходе вычислителя 17 значение (А - Z, - Ч ( Z 2 ), которое вместе со значением 0,+) с выхода сумматора-вычитателя 15 подается на входы 25 и 24 блока управления для определения операторов ; и соответственно. Значения i i fi записываются в свои регистры. В блоке управления происходит сравнение операторов fl и 2, и в случае их равенства в режиме, масштабирования реализуются вычисления (6). При этом на выход блока управления 26 подается сигнал, по которому коммутаторы 9, 10, 12 соединяют выходы коммутаторов 6 и 7 и элемента задержки 18 со входами

сумматоров-вычитателей 14, 13, 16 соответственно, а коммутатор 11 соединяет выход сумматора-вьгчитатёля 1 со входом регистра А, Вход 19 закрыт На выходы 20 и 22 блока управления значение оператора f- и на выходах сумматоров-вычитателей 13 - 16 получаются значения х , , 9,, , t которые записьгоаются в соответствующие регистры. С выхода вычислителя 17 разность (А-2 ) подается через вход 25 в блок управления 26 для выработки сигнала ui При отсутствии равенства 1 режим масштабирования не выполняется. Итерации повторяются до заданного количества. При выполнении операции (4) арифметическое устройство работает аналогичным образом с той разницей, что значение Г получается как функция знака координаты у , значение которой снимается в блок управления по входу 23. Для управления коммутаторами 6 - 8 с выхода блока управления снимается сигнал, соответствующий номеру итерации i.

После выполнения всех операций поворота вектора значения координат получаются умноженными на число А или поделенными на Z без дополнитель него удлинения в k раз.

Для формирования сигнала в режиме вращения на входы 23 и 24 дешифратора 27 знака операнда (ДС) подается значение у,- и 0 соответственно. В зависимости от того, каисая операция выполняется (3) или (4) с выхода логической схемы снШ:ается сигнал, соответствующий знаку 6( или у,В блоке управления триггер 28 задает режим работы устройства: вращение - на выход 21 логическая единица и масштабирование - на выход 21 логический ноль. Триггер 29 вырабатьгоает сигнал Л по знаку операнда с выхода 25 в режиме вращения, а триггер 30 - сигнал в режиме масштабирования. Эти сигналы поступа|от на схему логической равнозначности, и в случае их равенства триггер 28 устанавливает режим масштабирования.Генератор G служит для вьщачи импульсов с частотой выполнения шагов вычислений. Эти импульсы пересчитываются счетчиком 35, который вьщает на выход код номера итерации. Сигналы начальной установки блока не показаны

Эффективность изобретения заключается в расширении функциональных возможностей устройства. Кроме того, на всем диапазоне изменения переменных обеспечивается абсолютная сходимость вычислений и упрощается программирование задач, так как отпадает необходимость в согласовании масштаба операндов в различных частях программы.

17

31

27

25

29 JJ

А

3lf

22

-о

27

-о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1973 |

|

SU445042A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Парини | |||

| Система ДИВИК для решения сложных навигационных задач,- Электроника, 1966, № 13, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1985-07-15—Публикация

1983-09-27—Подача