формационным входом первого дешифра тора знака операндов, выход которого соединен с управляющими входами второго, четвертого сумматоров-вы- читателей и первым информационным входом третьего дешифратора знака операндов, второй информационный вход которого соединен с управляющи ми входами второго и шестого сумматоров-вычитателей и с вьгходом второго дешифратора знака операндов.

управляющий вход третьего коммутатора соединен с входом номера итерации устройства, выход шестого сумматора-вычитателя соединен с входом ЕГторого операнда третьего сумматора-вычитателя, выход третьего дешифратора знака операндов соединен с управляющими входами третьего и пятого сумматоров-вычитателей, выход первого сумматора- вычитателя соединен с выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| Вычислительное устройство | 1988 |

|

SU1522196A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Устройство для определения модуля трехмерного вектора | 1986 |

|

SU1388854A2 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Вычислительное устройство | 1981 |

|

SU959071A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА, содержащее первый, второй и третий регист ры, первый, второй и третий сумматоры-вычитатели,, первый и второй коммутаторы, первый дешифратор знака операндов, причем информационные выходы первого, второго и третьего сут маторов-вычитателей соединены с информационными входами соответственно первого, второго и третьего регистров, управляющие входы первого, и второго коммутаторов соединены с.входом номера итерации устройства, отличающееся тем, что, с целью повышения быстродействия, устройство содержит третий коммутатор, с первого по шестой вычитатели, четвертый, пятый и шестой сумматоры-вычитатели, второй и третий дешифраторы знака операндов, причем первые группы разрядных выходов первого, второго и третьего регистров соединены с входами первого операнда соответственно, первого, третьего и пятого вьгчнтателеи, выходы которых соединены с входами первого операнда соответственно, четвертого, третьего и пятого сумматоров-вычитателей, пыходы которых соединены соответственно с входом первого операнда первого сумматора-вычитателя, с информационным входом второго дешифратора знака операндов и с входом первого операнда второго сумматора-вычитателя, вторые группы разрядных выходов первого, второго и третьего регистров соединены с информационными входами соответственно первого, второго и третьего коммутаторов, первые 3 выходы которых соединены с входами второго операнда соответственно пер(Л вого Бычитателя, третьего вычитателя и пятого вычитателя, вторые выходы первого, второго и третьего коммутаторов соединены с входами первого операнда соответственно второго, четвертого и шестого вычитателей, выходы которых соединены с входами второго операнда соответственно втою рого сумматора-вычитателя, четвер00 09 того сумматора-вычитателя и шестого сумматора-вычитателя, вход второго операнда пятого сумматора-вычитателя и вход первого операнда шестого сумматора-вычитателя соединены с первыми выходами соответственно второго и первого коммутаторов, первые выходы которых соединены с входами второго операнда соответственно четвертого и второго вычитателей, вход второго операнда шестого вычитателя соединен с первым выходом третьего коммутатора, выход второго сумматора-вычитателя соединен с ин

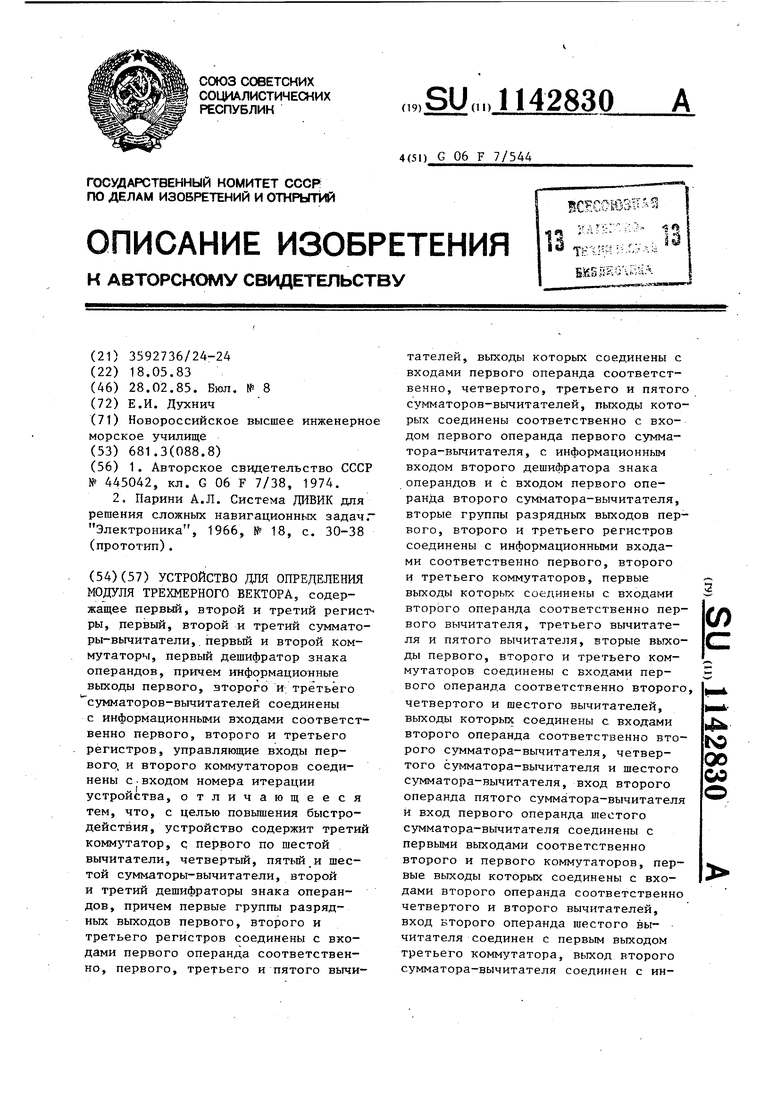

Изобретение относится к вычисл тельной технике и предназначено для построения на его основе спец лизированных ЦВМ. Известны арифметические устрой ва для обработки координат вектора, предназначенные для решения з дач, содержащих большое количеств координатных преобразований. Эти устройства позволяют .определить модуль вектора, заданного прямоугольными координатами (х, у) по формуле R где 1 - коэффициент деформации мо ля. Они содержат сдвигающие регистры коммутаторы, су {маторы-вычитатели и позволяют выполнять преобразова (1) в несколько раз быстрее, чем в традиционных арифметических устройствах t На практике часто необходимо определить модуль трехмерного век тора R. Преобразование (2) может быть выполнено с помощью указанных устройств за две операции типа (1). Однако такое время реализации не всегда допустимо. Наиболее близким по техническо сущности к изобретению является у ройство, работающее по алторитму Волдера .I. i-f. §U.i () где )fj , j , Sj - значения координсгУ и угла на i-и итерации-, оператор направления вращения ( i 1,2,..,,h ). Недостатком таких устройств является большое время реализации преобразования. Цель изобретения - повьшгение быстродействия путем сокращения времени преобразования в устройстве. Поставленная цель достигается тем, что в устройстве для определения трехмерного вектора, содержащее первый, второй и третий регистры, первый, второй и третий сумматоры-вычитатели, первый и второй коммутаторы, первьй дешифратор знака операндов, причем информационные выходы первого, второго и третьего .торов-вычитателей соединены с информационными входами соответственно первого, второго и третьего регистров, управляющие входы первого и второго коммутаторов соединены с входом номера итераций устройства, дополнительно введены третий коммутатор, с первого по шестой вычитателй, четвертый, пятый и шестой сумматоры-вычитатели, второй и третий дешифраторы знака операндов, причем первые группы разрядных выходов первого, второго и третьего регистров соединены с . входами первого операнда соответственно, первого, третьего и пятого вычитателей, выходы которых соединены с входами первого операнда , соответственно четвертого, третьего и пятого сумматоров-выгй1тателей, вы ходы которых соединены соответственно -с входом первого операнда пер вого сумматора-вычитателя, с информационным входом второго дешифратора знака операндов и входом первого операнда второго сумматора-вычитате ля, вторые группы разрядных выходов первого, второго и третьего регистр соединены с информационными входами соответственно первого, второго и третьего коммутаторов, первые выходы которых соединены с входами второго операнда соответственно пер вого вычитателя, третьего вычитател и пятого вычитателя, вторые выходы первого, второго и третьего коммутаторов соединены с входами первого операнда соответственно второго, четвертого и шестого вычитателей, выходы которых соединены с входами второго операнда соответственно второго сумматора-вычитателя, четвертого сзт матора-вычитателя и шестого сумматора-вычитателя, вход второго операнда пятого сумматоравычитателя и вход первого операнда шестого сумматора-вычитателя соединены с первыми выходами соответственно второго и первого коммутаторов, первые выходы которых соединены с входами второго операнда соответственно четвертого и второго вычитателей, вход второго.операнда шестого вычитателя соединен с первы ВЫХОДОМ третьего коммутатора, выход второго сумматора-вычитателя соедин с информационным входом первого дешифратора знака операндов, выход которого соединен с управляюш ши вх дами второго, четвертого сумматоров вычитателей и первым информационным входом третьего дешифратора знака операндов, второй информационный вход которого соединен с управляющими входами второго и третьего сумматоров-вычитателей и с выходом второго дешифратора знака операндов управляющий вход шестого коммута04тора соединен с входом fioMepa итерации устройства, выход шестого сумматора-вычитателя соединен с входом второго операнда третьего сумматоравычитателя, выход третьего дешифратора знака операндов соединен с управляющими входами третьего и пятого сумматоров-вычитателей, выход первого сумматора-вычитателя соединен с выходом устройства. На фиг. 1 представлена функциональная схема устройства-, на фиг, 2 функциональная схема (вариант) коммутаторов 4 - 6-, на фиг. 3 - микропрограмма работы блока управления. Устройство (фиг. 1) содержит регистры 1-3, коммутаторы , с первого по шестой вычитдтели 7-12, с первого по шестой с -мматоры-вычитатели 13-18, первой - третий дешифраторы знака операндов 19-21 и вход номера итерации устройства 22. Коммутаторы 4-6 (фиг. 2) со- держат дешифратор на m входов, на которые подается код номера итерации, и п выходов. Вре выходы дешифратора подключаются к входам первой группы из п конъюнкторов, а. первые п/2 выходов - к второй группе из п/2 конъюнкторов. Вторые входы конъюлкторов подключены к выходам регистра таким образом, чтобы с выхода 1 коммутатора получалось число, сдвин.тое на i разрядов, а с выхода-2 - на 2 разрядов. Работу устройства можно описать следующими вьфажениями: Xu. X.(-2-1....{2-V2 ).,.2-.. (2 -221-M,f,-(l-2-)z.; . {41 2н. 2.ГЧ2-).,х,2-Ц;Р,,0-2-1 причем ; . i Перед началом итерационного процесса (4) значения координат х , ч , Z находятся в регистрах 1-3 соответственно. С началом очередной итерации с выхода блока управления 22 стройства псдается сигнал, соответствующий ее номеру (например, от счетчика итерации), по которому 5 коммутаторы 4-6 настраиваются таким образом, чтобы с их первого выхода снималось число ( У или 2 ), сдвинутое на i разрядов, а с второго - на 2 разрядов. При этом с выхода вычитателя 7 получается значение X,. (1-2), с выхода сумматора-вычитателя 13 - значение у,- (1-2 + juvi ( ) , а с выхода сумматора-вычитателя 14 получается значение X - , которое записывается в ре гистр 1 вместо числа Xj , Аналогично с выходов сз мматоров-вьгчитателей 16 и 18 получаются значения v и , которые записываются в регистры 2 и 3, а также проанализируются дешифраторами 19 и 20. Дешифратор 21 служит для определения значений М; , по которым в следующей ите0рации сумматоры-нычитателн 15, 18 настраиваются на вьтолнение сложения или вычитания. После выполнения п итераций (где п - разрядность операндов) исходный вектор совпадает с осью х и в регистре 1 записывается значениеXn lX--t-vVz 1с П (1 - 2+ ) - деформация модуля. эффективность изобретения заключается в повышении быстродействия в два раза при увеличении объема оборудования примерно в полтора раза.

/77

22 о

Л/jr./

Вбм,2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1973 |

|

SU445042A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Система ДИВИК для регаения сложных навигационных задачг Электроника, 1966, № 18, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1985-02-28—Публикация

1983-05-18—Подача