элемента НЕ, третий выход дешифратора соединен с четвертым входом элемента 2-2И-ИЛИ-НЕ, четвертый выход дешифратора соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого элемента И, выход элемента НЕ соединен с BjiKOfiOM второго элемента И,; выход генератора тактовых импульсов соедине.н со счетным входом двоичного счетчика, первьй вход элемента 2-2И-ШШ соединен с информационным выходом третьего сумматора-вычитателя, второйвход элемента 2-2И-И11И соединен с информационным выходом седьмого сумматора-вычитатеЛя, первый вход дешифратора соединен с выходом четвертого, вычитателя, второй вход дешифратора соединен с выходом третьего вычитателя устройства, третий вход дешифратора соединен с выходом третьего сумматора, выходы разрядов двоичного счетчика соединены с управляющими входами первого, второго, третьего, четвертого и седьмого коммутаторов, четвертый выход.дешифратора Соединен с управляю1 сими входами третьего, четвертого и пятого сумматоров-вычитате- лей, выход второго элемента И соединен с управлякщими входами шестого и седьмого сумматоров-вычитателей, выход первого элемента И соединен с управлякщими входами первого и второго сумматоров-вычитателей и пятого и шестого коммутаторов, причем третий

вхрд и четвертый инверсный вход эле- дом.

мента 2-2И-ЙЛИ соединены с входами выбора операций устройства, причем выходы младших разрядов четвертого, пятого, и шестого сдвиговых регистров соединены соответственно с первым, вторым и третьим входами пятого коммутатора, разрядные выходы четвертого, пятого и шестого сдвиговых ре.гистров соединены соответственно с первым, вторым и третьим информационными входами шестого коммутатора, выход шестого коммутатора соединен с информационным входом седьмого коммутатора, выход которого соединен с входом элемента задержки, выход которого соединен с первыми входами операндов первого сумматора и первого вычитателя, выходы которых соединены с информационными.входами соответственно пятого и шестого сдвиговых регистров, информационный вход четвертого сдвигового регистра соединен с выходом пятого коммутатора, вторьми входами операндов первого и второго сумматоров и первого, второго и четвертого вычитателей, выход седьмого коммутатора соединен с первьми входами операндов второго сумматора и второго вычитателя, выходы которых соединены с первыми входами операндов третьего сумматора и третьего вычитателя, вторые входы операндов которого соединены с выходом младшего разряда седьмого сдвигового регистра и его информационным . вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1140117A1 |

| Устройство для преобразования координат вектора в трехмерном пространстве | 1986 |

|

SU1403062A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

| Устройство для определения модуля трехмерного вектора | 1983 |

|

SU1142830A1 |

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый. второй и третий сдвиговые регистры, первый, второй, третий и четвертый коммутаторы, семь сумматоров-вычитателей, причем выходы младших разрядов первого, второго и третьего сдвиговых регистров соединень с первыми входами операндов соответственно первого, второго и третьего сумматоров-вычи- тателей, вторые входы операндов которых соединены с выходами соответственно первого, третьего коммутаторов и входом угловьрс значений устройства, разрядные выходы первого и вто- рого сдвиговых регистров соединены с информационными входами соответственно первого, второго и третьего, четвертого коммутаторов, выходы первого и второго сумматоров-вычитателей соединены с первыми входами операндов соответственно четвертого и пятого сумматоров-вычитателей, вторые входы операндов которых соединены с вы:ходами соответственно третьего и первого коммутаторов, выходы четвертого и второго коммутаторов соединены с первыми входами операндов соответственно шестого и седьмого сумматоров-вычитателей, выходы которых соединены с информационными входами соответственно первого и второго сдвиговых регистров, выход третьего сумматора-вычитателя соединен с информационным входом третьего сдвигового регистра, выходы четвертого и пятого сумматоров-вычитателей соединены с вторыми входами операндов соответственно шестого и седьмого сумматоров-вычитателей, отличающееся тем, что, с целью расширения функциональных возможнос(Л тей за счет умножения и деления координат на произвольные коэффициенты, устройство содержит сдвиговые регистры с четвертого по седьмой, пятый, шестой и седьмой коммутаторы, первый, второй и третий .сумматоры, вычитатели с первого по четвертый, злемент задержки и блок управления, 9д 4 причем блок управления содержит дешифратор, генератор тактовых импульсов, двоичный счетчик, элемент 2-2ИЭд :о 9) -ШШ-НЕ, элемент 2-ЯИ-ИГШ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй элементы .И, элемент НЕ, причем первый выход деошфратора соединен с первым и вторым входами элемента 2-2И-ИЛИ-НЕ и с первыми входами первого элемента И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй выход дешифратора соединен с третьим входом элемента 2-2И-ИЛИ-НЕ, выход которого соединен с вторым входом элемента ИСКЛЮЧАЩЕЕ ИЛИ, которого соединен с вторым входом первого элемента И и входом

. : 1 , , .

Устройство относится к вычислительной технике, предназначено для . построения на его основе специализированных ЦВМ.

Известно арифметическое устройство, работающее с информацией, представленной в виде векторов, предназначенное для решения задач, содержащих большое количество тригонометрических функций l3«

Недостатком устройства является . представление результатов вычислейий в масштабе .

Известно арифметическое устройство 2j, работаняцее по усовершенствованному алгоритму Волдера:

Vw.y;-4;y,2;%f;.;245,,,,,2--

.t2 , -.q.y;2 ,(1)

где ; «sign для вычисления значений

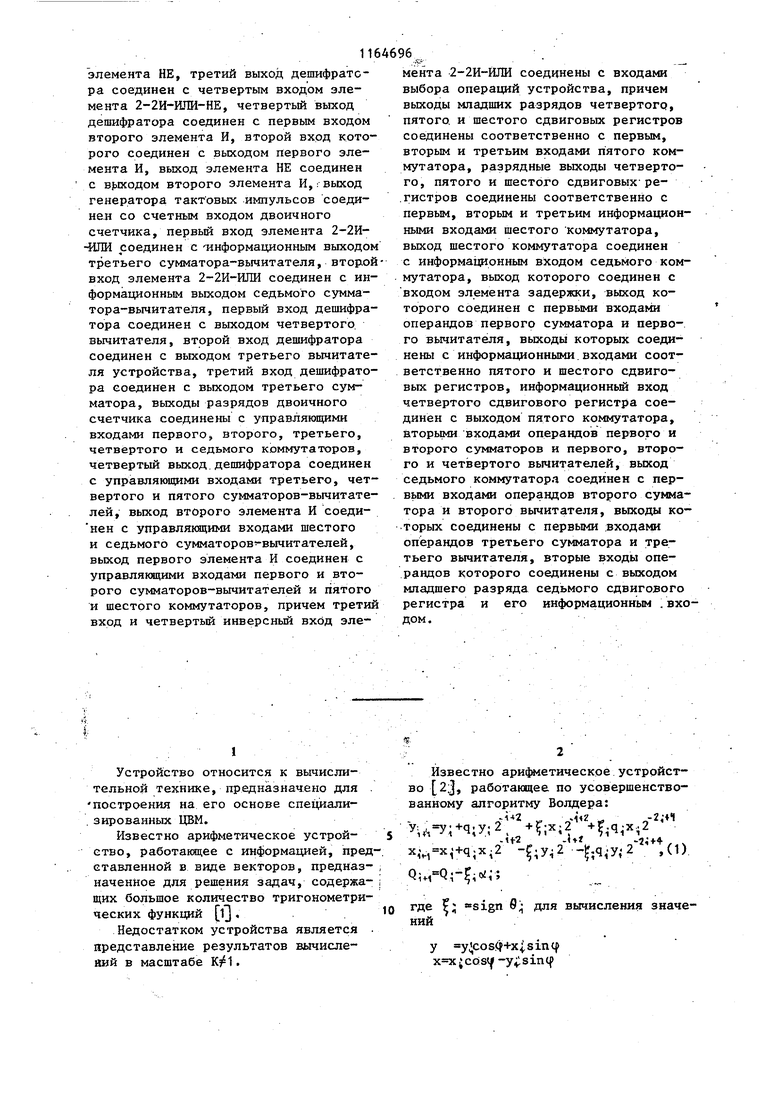

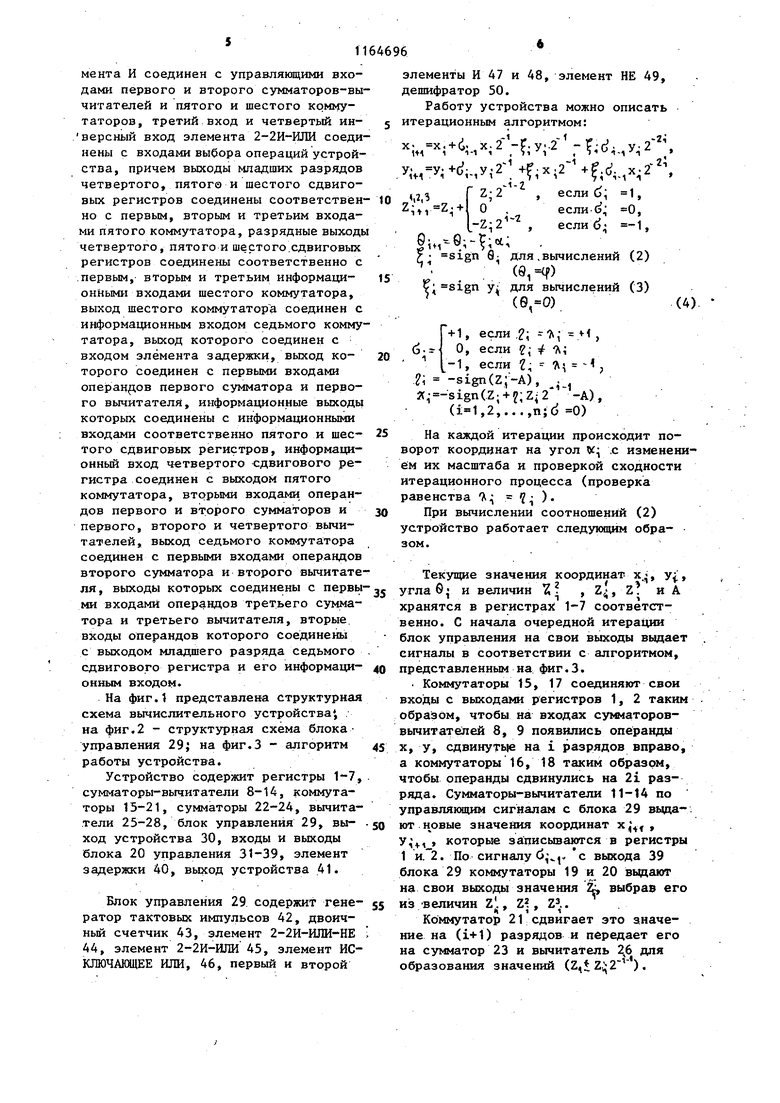

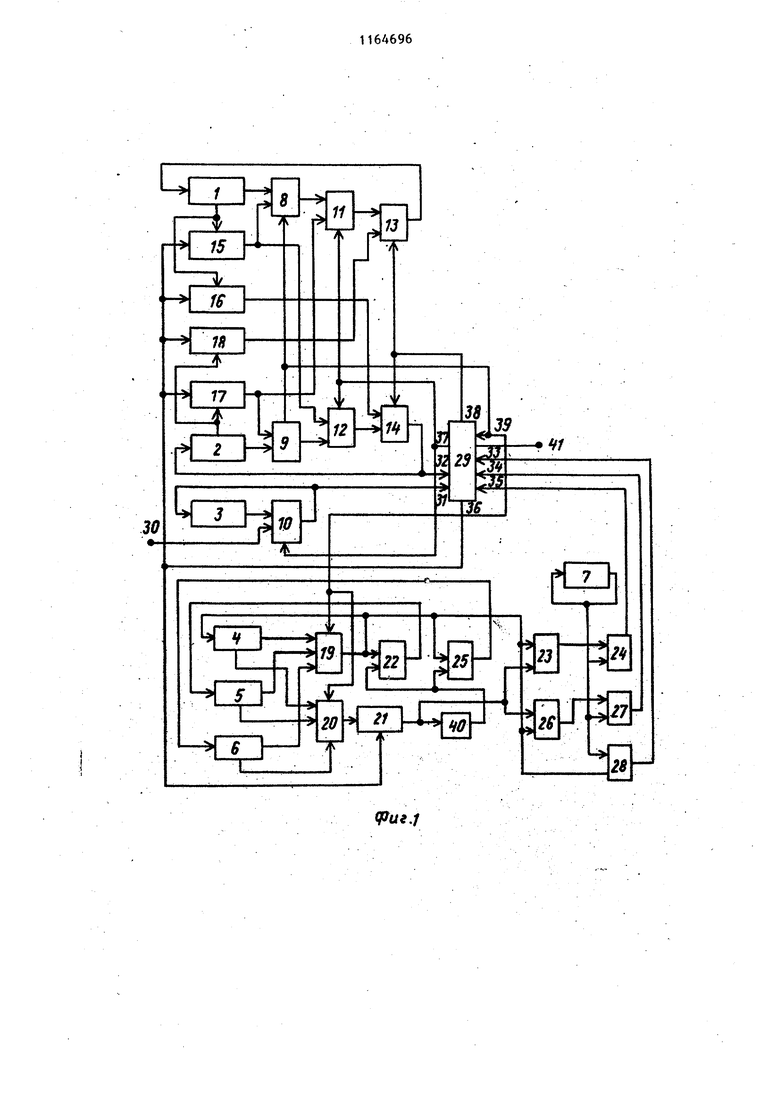

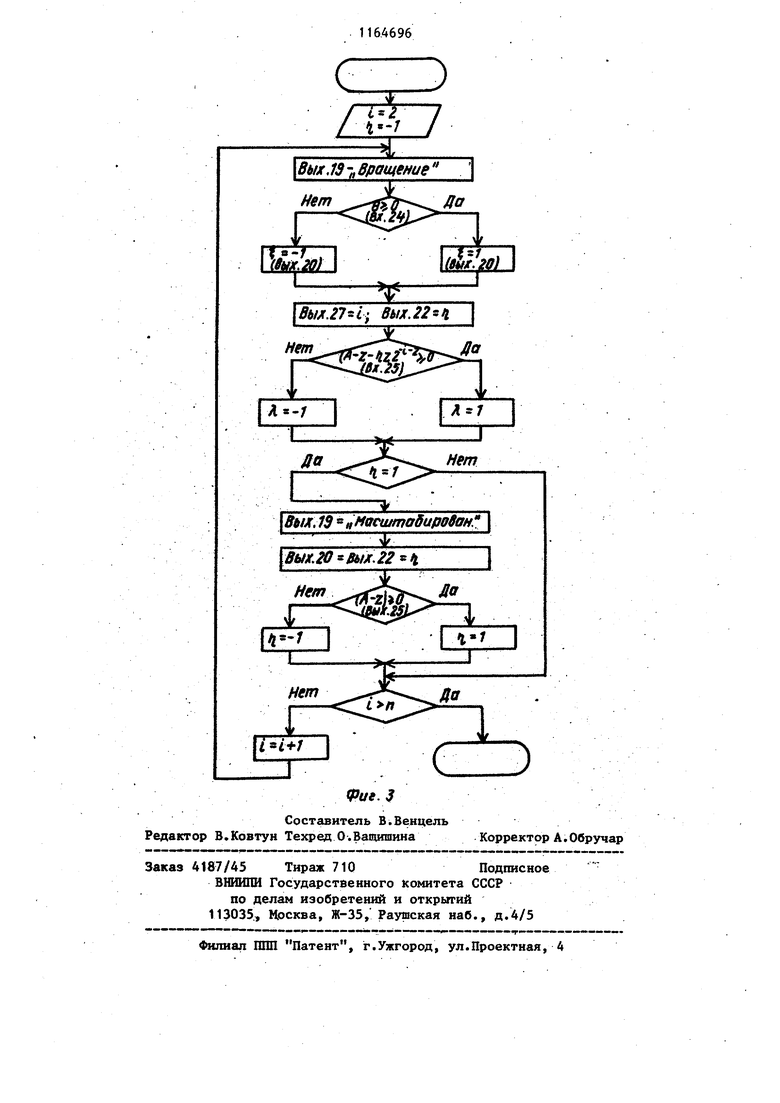

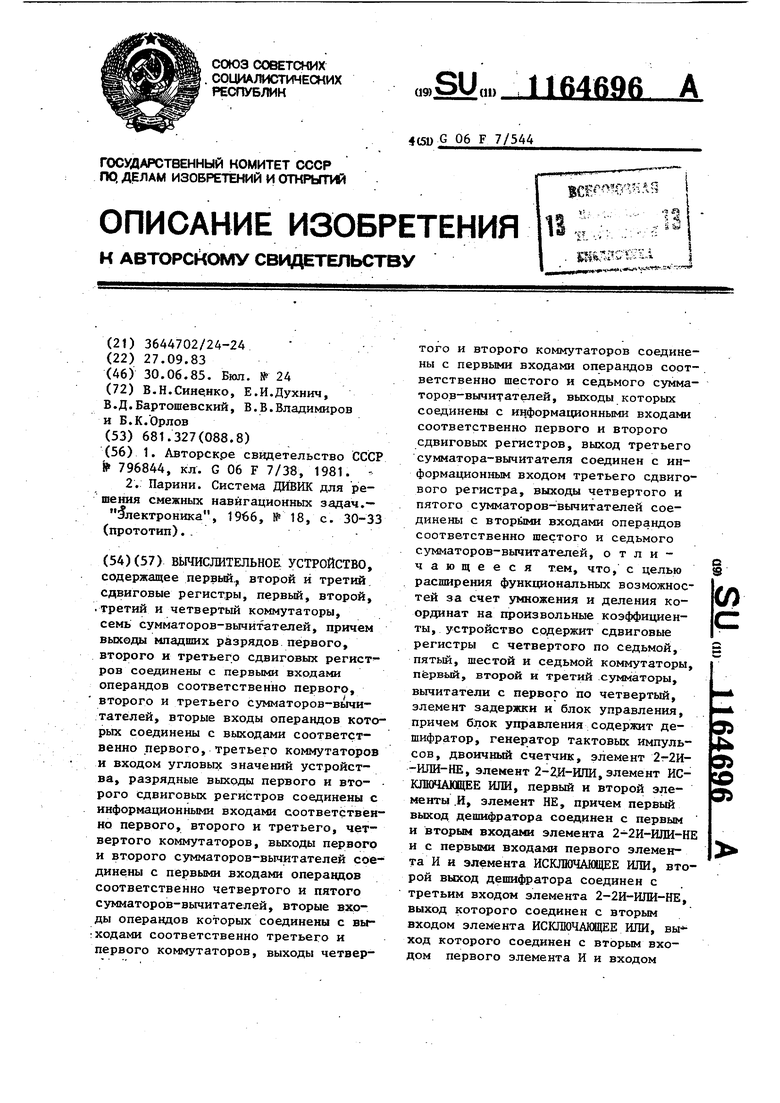

у sy cositf+x sincf -y;lsin(f Недостатком таких устройств явля ется отсутствие возможности умножени и/или деления координат на произволь ные коэффициенты. Цель изобретения - расширение фун кциональных возможностей устройства за счет вычисления выражений вида: У cos(p+x;sin f ) Л X (,-sintf) 0 arctg y, /X,. При устройство позволяет произ- водить умножение координат на число А с компенсацией изменения масштаба, а при - деление координат век тора на константу Z. Поставленная цель достигается тем, что.в вычислительное устройство, содержащее первый, второй « третий сдвиговые -регистры, первый, второй, третий и четвертый коммутаторы, семь сумматоров-вычитателей, причем выходы младших разрядов первого, второго и третьего сдвиговых регистров соединены с первыми входами операндов соответственно первого, второго и третьего сумматоров-вычитателей, вторые входы операндов которых соединены с выходами соответст венно первого, третьего коммутаторов и входом угловых значений устройства разрядные выходы первого и второго сдвиговых регистров соединены с информационными входами соответственно первого, второго, третьего и четвертого коммутаторов, выходы первого и второго сумматоров-вычитателей соеди нены с первыми входами операндов соответственно четвертого и пятого сумматоров-вычитателей, вторые входы операндов которых соединены с выхода ми соответственно третьего и первого коммутаторов, выходы четвертого и второго 1соммутаторов соединены с первыми входами операндов соответственно шестого и седьмого сумматороввычитаталей, выходы которых соединены с информационными входами соответ ственно первого и второго сдвиговых регистров, выход третьего сумматора- вычитателя соединен с информационным входом третьего сдвигового регистра. выходы четвертого и пятого сумматоров-вычитателей соединены с вторыми входами операндов соответственно шестого и седьмого сумматоров-вычитателей, дополнительно введены сдви-.говые регистры с четвертого по седьмой, пятый, шестой и седьмой коммутаторы, первьш, второй и третий сумматоры, вычитатели с первого по четвертьй, элемент задержки и блок уп- . равления, причем блок управления содержит дешифратор, генератор тактовых импульсов, двоичный счетчик, элемент 2-2И-ИЛИ-НЕ, элемент 2-2И-ИЛИ, элемент ИСКЛЮЧМШЩЕ ИЛИ, первый и второй элементы И, элемент НЕ, причем первый выход, дешифратора соединен с первым и вторым входами элемента 2-2И-Ш1И-НЕ и с первьп«ш входа.ми первого элемента И и элемента ИСКЛКЬ ЧАЩЕЕ ИЛК, второй выход дешифратора соединен с третьим входом элемента 2-2И-ИЛИ-НЕ, выход которого сое- . динен со вторьм входом элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход которого соединен с вторым входом .первого элемента И и входом элемента, НЕ, третий выход деншфратора соединен с четвертым входом элемента 2-2И-Ш1И-НЕ, четвертый выход дешифратора соединен с первым входом второго элемента И, . второй вход которого соединен с выходом первого элемента И, выход элемента НЕ соединен с выходом второго элемента И, выход генератора тактовых импульсов соединен со счетным входом двоичного счетчика, первый вход элемента 2-2И-ШШ соединен с информационным выходом третьего сумматора-вычитателя, второй вход элемента 2-2И-ИЛИ соединен с информационным выходом седьмого сумматора-вы-. читателя, первый вход дешифратора соединен с выходом четвертого вычита- теля, второй вход дешифратора соединен с выходом третьего вычитателя, третий вход дешифратора соединен с выходом третьего сумматора, выходы разрядов двоичного счетчика соединены с управлякицими входами первого, второго, третьего, четвертого и седьмого коммутаторов, четвертый выход дешифратора соединен с управляющими входами третьего, четвертого и пятого сумматоров-вычитателей, выход второго элемента И соединен с управлякмцими входами шестого и седьмого сумматоров-вычитателей, выход первого элемента И соединен с управляющими входами первого и второго сумматоров-вы читателей и пятого и шестого комму таторов, третий вход и четвертьй инверсный вход элемента 2-2И-ИЛИ соеди нены с входами выбора операций устройства, причем выходы младших разрядов четвертого, пятога и шестого сдвиговых регистров соединены соответствен но с первым, вторым и третьим входами пятого коммутатора, разрядные выход четвертого, пятого и шестого.сдвиговых регистров соединены соответственно с .первым, вторым и третьим информациоиными входами шестого коммутатора, выход шестого коммутатора соединен с информационным входом седьмого комму татора, выход которого соединен с входом элемента задержки, выход которого соединен с первьвми входами операн ;ов первого сумматора и первого вычитателя, информационные выходы которых соединены с информационными входами соответственно пятого и шеетого сдвиговых регистров, информационный вход ч-етвертого -сдвигового регистра соединен с выходом пятого коммутатора, вторыми входами операндов первого и второго сумматоров и первого, второго и четвертого вычитателей, выход седьмого коммутатора соединен с первыми входами операндов второго сумматора и второго вычитате ля, выходы которьк соединены с первы ми входами операндов третьего сумматора и третьего вычитателя, вторые входы операндов которого соединены с выходом младшего разряда седьмого сдвигового регистра и его информациоиным входом. На фигЛ представлена структурная схема вычислительного устройства, на фиг.2 - структурная схема блокауправления 29; на фиг.З - алгоритм работы устройства. Устройство содержит регистры , сумматоры-вычитатели 8-14, коммутаторы 15-21, сумматоры 22-24, вычитатели 25-28, блок управления 29, выход устройства 30, входы и выходы блока 20 управления 31-39, элемент задержки 40, вьрсод устройства 41. Блок управления 29 содержит генератор тактовых импульсов 42, двоичный счетчик 43, элемент 2-2И-ИЛИ-НЕ 44, элемент 2-2И-ШШ 45, элемент ИСКПЮЧАВДЕЕ ИЛИ, 46, первый и второй элементы И 47 и 48, элемент НЕ 49, дешифратор 50. Работу устройства можно описать итерационным алгоритмом: --i - --1 . -2i -ж-;Ч.,г у;-2 r., ,.x.2-.d,,,x.2,2.5 Г Z;2 , еслиб 1, если d 0, Z.-t- О I-Z-2 если d- -1, г- sign 9- для,вычислений (2) . (9,) ; sign у; для вычислений (3) (е,о) + 1, если .2 - Л,- , (5.I-. О, если е- -А; -1, если 2; - 7 -, i -sign(Z;-A), . J(- -sign(Z;-(- ;Zi2 -А), (,2,...,n;d 0) На каждой итерации происходит поворот координат на угол V: .с изменением их масштаба и проверкой сходности итерационного процесса (проверка равенства Z ). При вычислении соотношений (2) устройство работает следующим образом. Текущие значения координат x.,j, у, угла б и величин , Z, z и А хранятся в регистрах 1-7 соответственно. С начала очередной итерации блок управления на свои выходы выдает сигналы в соответствии с алгоритмом, представленным на фиг.3. . Коммутаторы 15, 17 соединяют свои входы с выходами регистров 1,2 таким образом, чтобы на входах сумматороввьгчитателей 8, 9 появились операнды X, у, сдвинуть|е на i разрядов вправо, а коммутаторы 16, 18 таким образом, чтобы операнды сдвинулись на 21 разряда. Су1«4аторы-вычнтатели 11-14 по управлякхцим сигналам с блока 29 вьщают значения координат х{ , у,, , которые записываются в регистры 1 и. 2. По сигналу (i,|Y с выхода 39 блока 29 коммутаторы 19 и 20 выдают на свои выходы значения Ц, выбрав его из /величин Z., Z, Z.. Коммутатор 21 сдвигает это значение на (1+1) разрядов и передает его на сумматор 23 и вычитатель для образования значений (Z, Z;;;2 ) . 7 Одновременно с выкода. элемента 40 получается значение , которое поступает на сумматор 22 и вычитател 25 для образования соответственно ве личин z- и Z , которые записыва ются в регистры 5 и 6. В регистре 4 остается значение Z, . На вход 30 устройства поступает величина е({ и сумматор-вычитатель 10.выдает значение 9; , которое запишется в регистр 3. Величина А поступает из регистра 7 на сумматор 24 и вычитатели 27 и 28 для вычисления соответственно величин (ZiZ 2-А) и (Z(-A), кото-. рые поступают в блок 29 по входам 35, 34, 33 для определения величины XJ и Z-. Необходимость определения трех значений Z- связана с. тем обстоятельством, что в текущей итерации величины (j. еще не известна и определяется в блоке 29 только пе- ред следующей итерацией. Реализация вычислений (3) происходит аналогичным образом, за исклкг чением того, что в блоке 29 величина определяется по знаку координат yj, снимается с входа 32. 1 После дополнения всех итерацииповорота выступа значения координат получаются умноженными на числа А ./ или поделенными на Z без дополнительного удлинения в k раз. Коммутаторы 15, 16 или 21 могут представлять собой, например, мультиплексоры, имеюпще управляющий вход для номера итерации, п информащюнных входов и один выход. Они соединяют один из входов с выходом. Так, по номеру итерации крммутатор 21 вы- 40 дает значе1ше , которое и по96.8 ступает на блок задержки 40, сумматор 23 и вычитатель 26 для сложения (вычитания) с величиной Z, . Коммутаторы 19 и 20. отличаются друг от друга тем, что первый получает на входах и выдает на выходе последовательные коды чисел , . а второй - параллельные. Схемная реализация коммутаторов зависит от способа кодирования величины С . Схема блока управления может быть синтезирована известными инженерными приемами как микропрограммный автомат по MHKponporpafoie, приведенной на фиг.З. На фиг.2 приведена схема блока управления, которая содержит дешифратор знака операнда, генератор, счетчик СТ2 и логические схемы. Элемент DC1 дешифратора 50 служит для определения величины по знаку операнда со входа 33, а элементы DC2 и DC3 дешифратора 50 - величины . Эти величины подаются на схему логической равнозначности, с выхода которой получается сигналс 0 . с. помощью коньюнктора определяется по знаку g . Сигнал d подается на выход 39. Элемент DC4 дешифратора 50 предназначен для определения величины F по знаку б или у, поступающим на входы 31 или 32. Элемент 48 предназначен для определения знака величины d , которая.вместе с сигналом Г 0 подается на выход 38. Генератор G служит для выдачи импульсов с частотой выполнения итерации. Эти импульсы пересчитываются счетчиком 43, который по выходу 36 вьщает код номера итерации. Сигналы начальной установки блока не показаны.

U9,J

Д-Л

33

35

Операция (3) или (t)

HI

2

«

V5

1

&

33

TTji

ч

- . ft9

81 B

38 -r-о

37 -о

фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1979 |

|

SU796844A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Парини | |||

| Система ДИВИК для решения смежных навйгационньпс задач,- Электроника, 1966, № 18, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1985-06-30—Публикация

1983-09-27—Подача