лителя, третьи входы являются третьими и четвертыми входами вычислителя соответственно, а выходы соединены соответственно с первыми и втоИзобретение относится к измерительной технике, в частности к устройствам для преобразования информации из аналогового вида в цифровую форму, и может быть использовано при построении измерительно- вычислительных комплексов.

Целью изобретения является повышение разрешающей способности и точности преобразования поддиапазонного аналого-цифрового преобразователя.

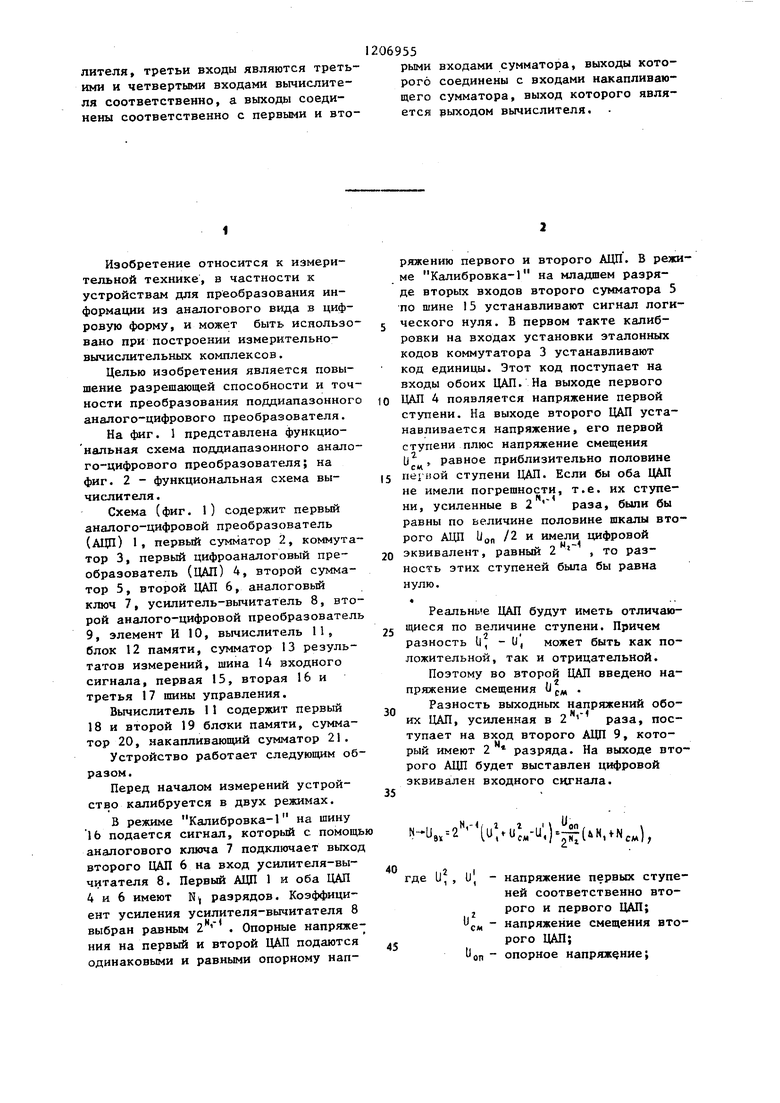

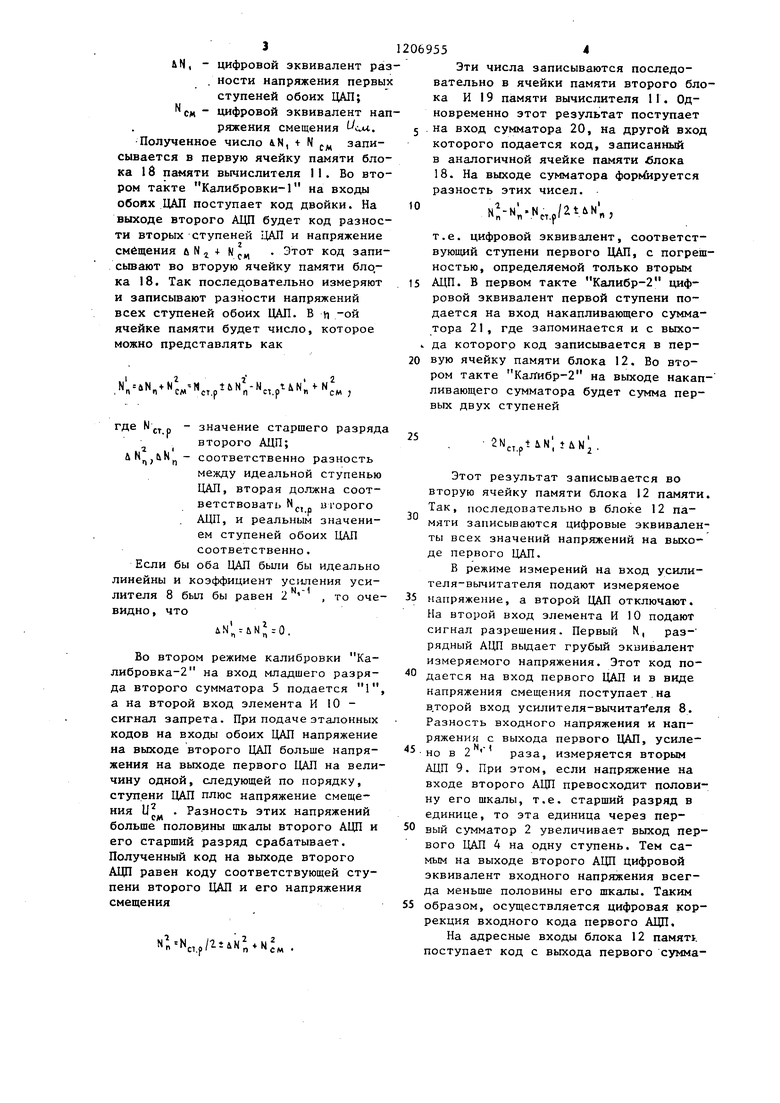

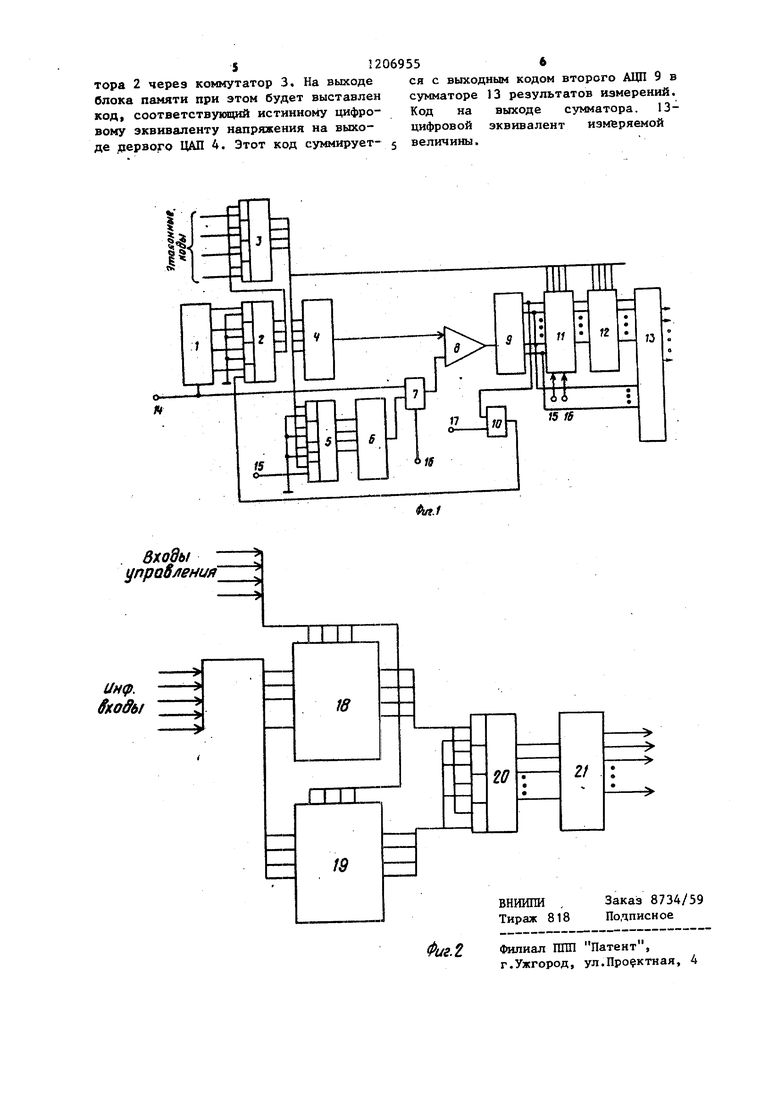

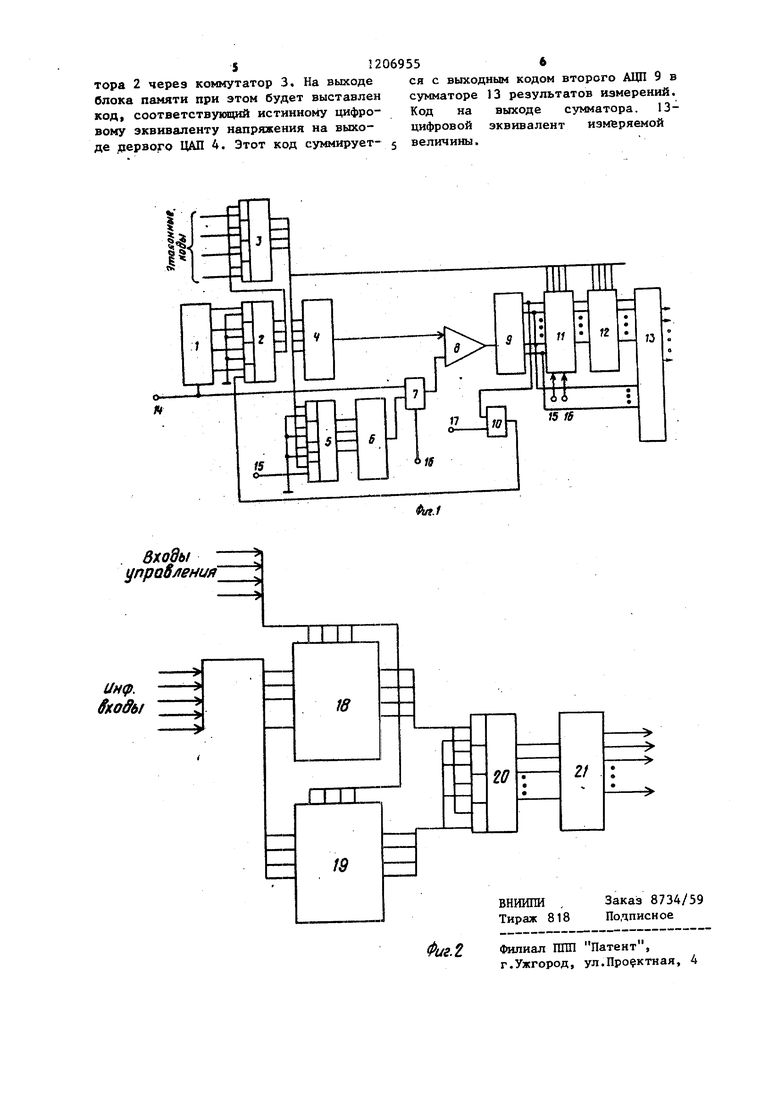

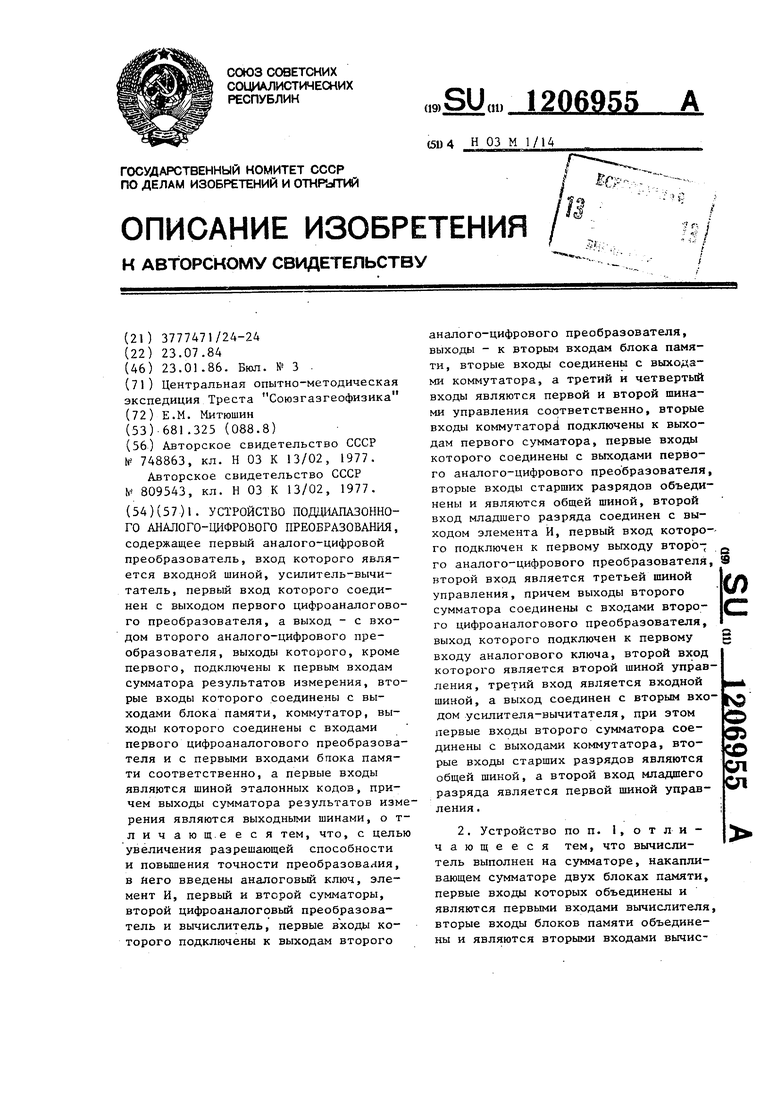

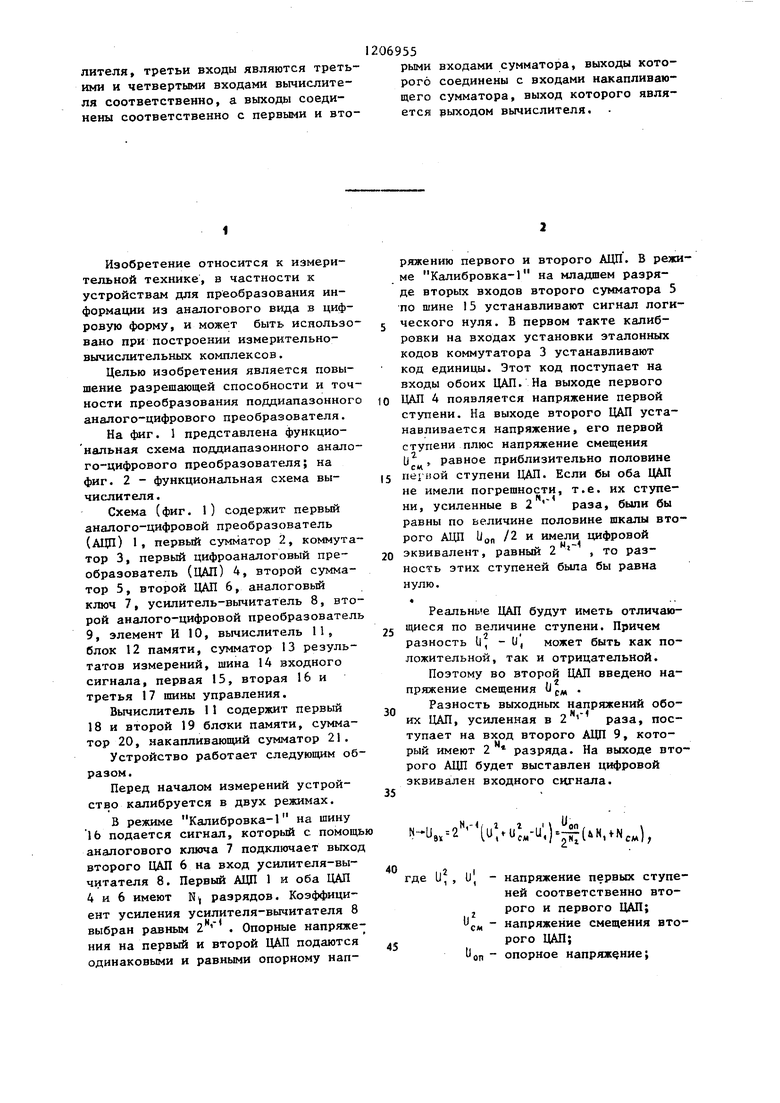

На фиг. 1 представлена функцио- нальная схема подциапазонного аналого-цифрового преобразоват€;ля; на фиг. 2 - функциональная схема вычислителя .

Схема (фиг. 1) содержит первый аналого-цифровой преобразователь (АГЩ) 1, первый сумматор 2, коммутатор 3, первый цифроаналоговый преобразователь (ЦАП) 4, второй сумматор 5, второй ЦАП 6, аналоговый ключ 7, усилитель-вычитатель 8, второй аналого-цифровой преобразователь 9, элемент И 10, вычислитель 11, блок 12 памяти, сумматор 13 результатов измерений, шина 14 входного сигнала, первая 15, вторая 16 и третья 17 шины управления.

Вычислитель 11 содержит первый 18 и второй 19 блоки памяти, сумматор 20, накапливающий сумматор 21.

Устройство работает следующим образом.

Перед началом измерений устройство калибруется в двух режимах.

В реткиме Калибровка-1 на шину 16 подается сигнал, котор1 1й с. помощь аналогового ключа 7 подключает выход второго ЦАП 6 на вход усилителя-вы- читателя 8. Первый АЦП 1 и оба ЦАП 4 и 6 имеют N разрядов. Коэффициент усиления усилителя-вычитателя 8 выбран равным . Опорные напряжения на первый и второй ЦАП подаются одинаковыми и равными опорному нап1206955

рыми входами сумматора, выходы которого соединены с входами накапливающего сумматора, выход которого является выходом вычислителя.

ряжению первого и второго АЦП. В режиме Калибровка-1 на младшем разряде вторых входов второго сумматора 5 по шине I5 устанавливают сигнал логического нуля. В первом такте калибровки на входах установки эталонных кодов коммутатора 3 устанавливают код единицы. Этот код поступает на входы обоих ЦАП. На выходе первого

ЦАП 4 появляется напряжение первой ступени. На выходе второго ЦАП устанавливается напряжение, его первой ступени плюс напряжение смещения и , равное приблизительно половине

С W

nei ой ступени ЦАП. Если бы оба ЦАП не имели погрешности, т.е. их ступени, усиленные в 2 раза, были бы равны по величине половине шкалы второго АЦП iJon /2 и имели цифровой

эквивалент, равный 2 , то разность этих ступеней была бы равна нулю.

Реальные ЦАП будут иметь отличаю- щиеся по величине ступени. Причем разность Ij, - и , может быть как положительной, так и отрицательной.

Поэтому во второй ЦАП введено напряжение смещения 0 . Разность выходных напряжений обоих ЦАП, усиленная в раза, поступает на вход второго АЦП 9, который имеют 2 разряда. На выходе второго АЦП будет выставлен цифровой

зквивален входного сигнала.

-b,. AHuVuL-u ,).(.N..N,J,

и,, и, - напряжение первых ступеней соответственно вто- J рого и первого ЦАП; с„ - напряжение смещения нто45

и

рого ЦАП; on опорное напряжение;

AN, цифровой эквивалент раз . ности напряжения первых

ступеней обоих ЦАП; N с;ц - цифровой эквивалент нап

ряжения смещения . Полученное число 4.N, t N д, записывается в первую ячейку памяти блока 18 памяти вычислителя II. Во втором такте Калибровки-1 на входы обоих ЦАП поступает код двойки. На выходе второго АЦП будет код разности вторьгх ступеней ЦАП и напряжение смещения U N -1 4- N р . Этот код запи- сьшают во вторую ячейку памяти бло,- ка 18. Так последовательно измеряют и записывают разности напряжений всех ступеней обоих ЦАП. В ц -ой ячейке памяти будет число, которое можно представлять как

,N „ 4N,.N ,-N,,,,,,

где N р - значение старшего разряд

второго АЦП;

соответственно разность между идеальной ступенью ЦАП, вторая должна соответствовать N БГОРОГО АЦП, и реальным значением ступеней обоих ЦАП соответственно.

Если бы оба ЦАП были бы идеально линейны и коэффициент усиления усилителя 8 был бы равен 2 , то очевидно, что

,

Во втором режиме калибровки Ка- либровка-2 на вход младшего разряда второго сумматора 5 подается 1 а на второй вход элемента И 10 - сигнал запрета. При подаче эталонных кодов на входы обоих ЦАП напряжение на выходе второго ЦАП больше напряжения на выходе первого ЦАП на величину одной, следующей по порядку, ступени ЦАП плюс напряжение смещения и . Разность этих напряжений больше половины шкалы второго АЦП и его старший разряд срабатывает. Полученный код на выходе второго АЦП равен коду соответствующей ступени второго ЦАП и его напряжения смещения

,,p/liAN N

см

12069554

Эти числа записываются последовательно в ячейки памяти второго блока И 19 памяти вычислителя 1I. Одновременно этот результат поступает 5 на вход сумматора 20, на другой вход которого подается код, записанный в аналогичной ячейке памяти лока 18. На выходе сумматора форьй руется разность этих чисел. 10

,,p/2t.N;,

т.е. цифровой эквивалент, соответствующий ступени первого ЦАП, с погрешностью, определяемой только вторым

АЦП. В первом такте Калибр-2 цифровой эквивалент первой ступени подается на вход накапливающего сумматора 21, где запоминается и с выхо- да которого код записывается в первую ячейку памяти блока 12. Во втором такте Калибр-2 на выходе накапливающего сумматора будет сумма первых двух ступеней

25

2N

cT..,

Этот результат записывается во вторую ячейку памяти блока 12 памяти, Так, последовательно в блоке 12 памяти записываются цифровые эквиваленты всех значений напряжений на выходе первого ЦАП.

В режиме измерений на вход усили- теля-вьгчитателя подают измеряемое

напряжение, а второй ЦАП отключают. На второй вход элемента И 10 подают сигнал разрешения. Первый N, раз- рядный АЦП выдает грубый эквивалент измеряемого напряжения. Этот код подается на вход первого ЦАП и в виде напряжения смещения поступает.на в.торой вход усилителя-вычитат еля 8. Разность входного напряжения и напряжения с выхода первого ЦАП, усиле

но в 2 раза, измеряется вторым АЦП 9. При этом, если напряжение на входе второго АЦП превосходит половину его шкалы, т.е. старший разряд в единице, то эта единица через первый сумматор 2 увеличивает выход первого ЦАП 4 на одну ступень. Тем самым на выходе второго АЦП цифровой эквивалент входного напряжения всегда меньше половины его шкалы. Таким

образом, осуществляется цифровая коррекция входного кода первого АЦП.

На адресные входы блока 12 памяти поступает код с выхода первого сумматора 2 через коммутатор 3. На выходе блока памяти при этом будет выставлен код, соответствующий истиииоь1у цифровому эквивапеиту напряжения на выходе ЦАП 4. Этот код суммирует-

ся с выходным кодом второго АЦП 9 в сумматоре 13 результатов измерений. Код на выходе сумматора. 13- цифровой эквивалент измеряемой величины.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2399156C1 |

| Электроразведочная станция | 1987 |

|

SU1469489A1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Устройство для измерения объемной скорости внешнего дыхания | 1989 |

|

SU1623611A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

| Режекторный фильтр | 1986 |

|

SU1417180A2 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

входы управ/гени/

инф. ffxoffb/

ВНИИПИ , Заказ 8734/59 Тираж 818 Подписное

Филиал ШШ Патент, г.Ужгород, ул.Проектная, 4

| Аналого-цифровой преобразователь | 1978 |

|

SU748863A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР (, 809543, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-01-23—Публикация

1984-07-23—Подача