1

изобретение относится к автоматике и вычислительной технике и может использоваться в аппаратуре передачи данных, функционирующей с кодами системы остаточных классов.

Целью изобретения является повышение достоверности передаваемой информации за счет определения искаженого вычета oi; числа А (с,, У, ,.., р) до начала перевода числа в позиционную систему счисления путем анализа качества входных сигналов , которыми передаются вычеты, стирания искаженного и осуществления перевода числа в позиционную систему в диапазоне представления без основания PJ , соответствующего искаженному вычету , .

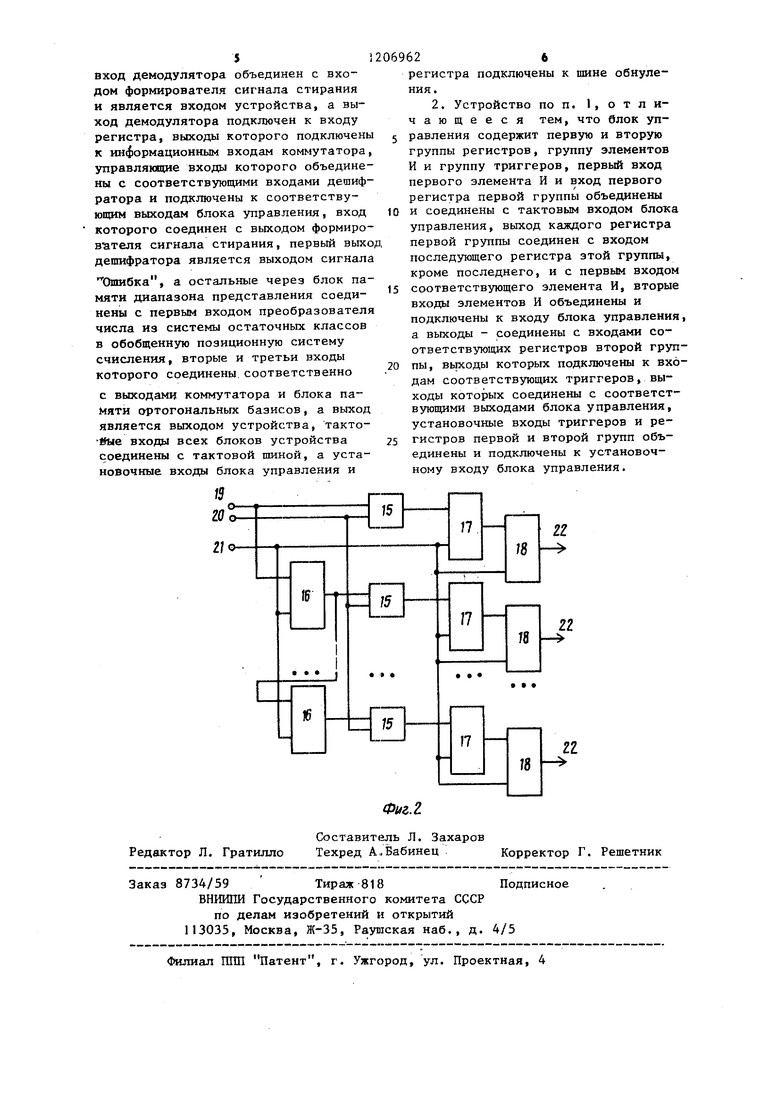

На фиг. 1 представлена функциональная схема устройства; на фиг.2 функциональная схема блока управления.

Устройство (фиг. ) содержит формирователь 1 сигнала стирания, демодулятор 2, регистр 3, коммутатор 4, преобразователь 5 числа из системы остаточных классов в обобщенную позиционную сист€;му, блок 6 управления, дешифратор 7, блок 8 памяти диапазона представления, блок 9 памяти ортогональных базисов, вход 10 устройства,, выход 1 ,, тактовую шину 12, шину I3 обнуления и вьпсод 14 сигнала Ошибка.

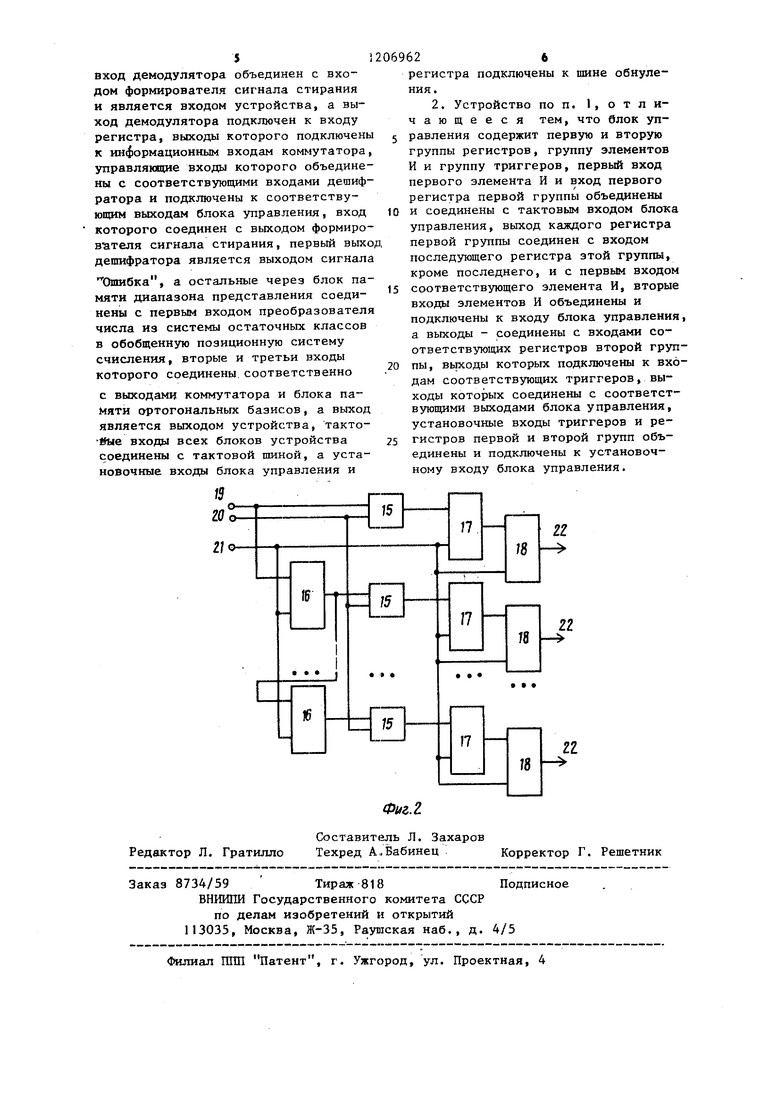

Блок 6 управления (фиг. 2) содержит группу элементов И 15, первую группу регистров 16,, вторую группу регистров 17, группу триггеров 18, тактовый вход 19, вход 20, установочный вход 21 и выходы 22 блока 6 управления.

Устройство для коррекции ошибок в информации, представленной в системе остаточных классов, работает следующим образом.

Принимаемый из канала связи сигнал соответствующий одному из разрядов числа А (л, , «г п )

поступает с входа 10 на демодулятор 2 и формирователь 1 сигнала стирания, в котором происходят контроль и оценка параметров сигнала Ч вырабатьшается сигнал стирания О в случае выхода параметров сигнала за допустимые границы. С демодлятора 2 код проверяемого числа поступает на регистр 3, с выходов которого значения (Х, -ы, вычетов

069622

поступают на коммутатор 4. Если входные сигналы устройства не были иска жены, то с выхода формирователя .1 сигнала стирания сигнал 1 посту- 5 пает на вход блока 6 управления, с выходов которого поступают сигналы 1, каждый из которых разрешает коммутатору 4 коммутацию параллельного двоичного кода «, (i 1, п) вы- 10 чета. В случае искажения входного сигнала с формирователя 1 сигнала стирания сигнал О поступает на блок 6 управления, который выдает на коммутатор 4 сигнал О для ком- (5 мутации oi вычета, которому соответствует искаженный сигнал.

Блок 6 управления работает следующим образом. При наличии на входе 20 сигнала 1 тактовые импульсы

20 через первый элемент И 15 поступают в соответствующий регистр 17 и продвигаются в нем, в результате чего через К, тактов на выходе соответствующего триггера 18 появится сигнал

25 1. Тактовые импульсы поступают также в последовательно соединенные регистры 16 первой группы, которые имеют разрядность , соответственно. Через К( тактов 30 на. выходе первого регистра 16 появится сигнал 1, через К + К тактов сигнал 1 появится на выводе

следующего регистра 16, а через

п-

L .21 Ki тактов сигнал появится

ЭС т

на выходе последнего регистра 16. При наличии сигнала 1 на входе 19 и на выходах регистров 16 тактовые импульсы через соответствукицие элементы И 15 поступают в регистры 17 второй группы разрядностью К, соответственно и через число тактов, равное их разрядности, установят триггеры 18 в единичное состояние, на выходах 22 которых появятся единичные сигналы. В случае появления на входе 20 сигнала О тактовые импульсы не будут проходить через элементы И 15, в результате чего на одном из выходов 22 сигнал 1

40

45

50

будет отсутствовать.

Подачей на вход 21 сигнала 1 все элементы блока 6 управления устанавливаются в нулевое, состояние. Сигналы коммутации с блока 6 управ- 55 ления поступают на дешифратор 7, который в случае поступления на его входы более одного сигнала О вьщает сигнал Ошибка по выходу 14.

в остальных случаях на блок 8 памяти поступает код для считывания диапазона представления без основания Р. , соответствующего искаженному вычету . С выходов коммутатора 4 вычеты «I - oi „ (значение искаженного вычета о(, 0) поступают на преобразователь 5 числа из системы остаточных классов в обобщенную позиционную систему,- на который подаютсй значения ортогональных базисов (i 1, п) с блока 9 памяти ортогональных базисов и значение диапазона представления Р; с блока 8 памяти диапазона представления. Вычисление значения числа А происходит по формуле А (),В , + «.Bj + ... +(у„В„ -б Р,- , где 9 О, 1, 21, при котором число А t Р, .

Все элементы устройства подключены к шине 12 тактовых импульсов.

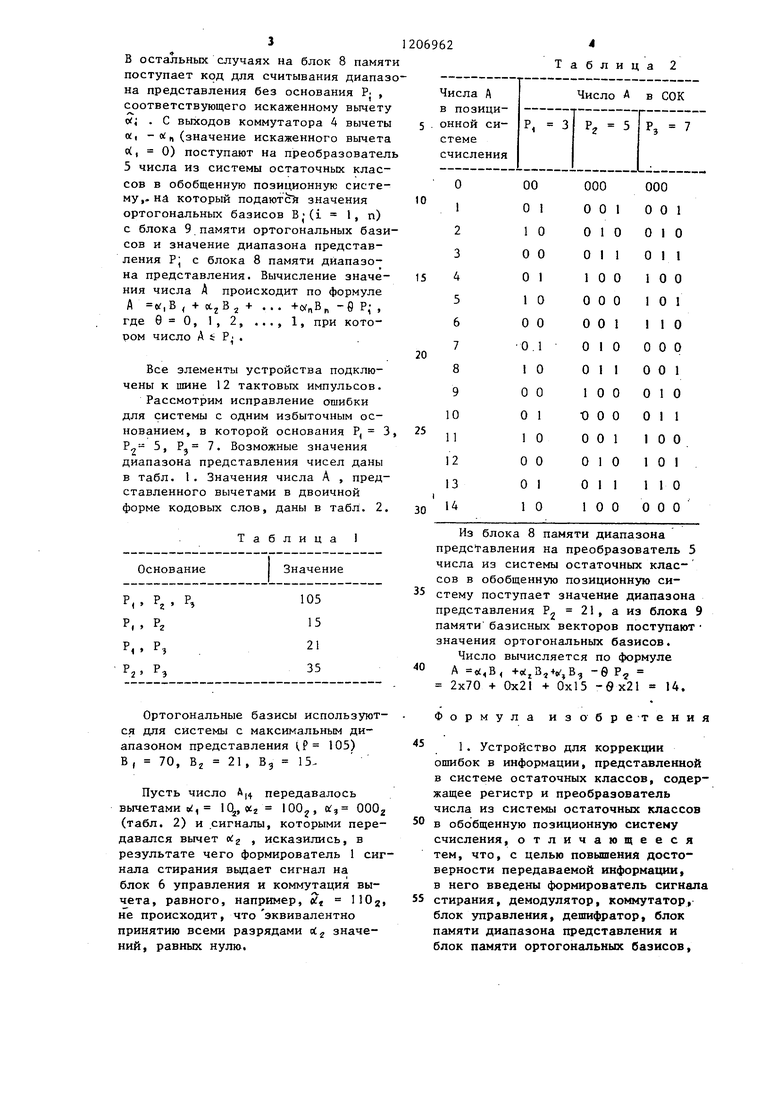

Рассмотрим исправление ошибки для системы с одним избыточным основанием, в которой основания Р, 3 5, PJ 7. Возможные значения диапазона представления чисел даны в табл. 1. Значения числа А , представленного вычетами в двоичной форме кодовых слов, даны в табл. 2.

Таблица 1

Основание

Значение

Ортогональные базисы используются для системы с максимальным диапазоном представления (,Р 105)

В,

70, Вг 21, В, 15.

Пусть число Л| передавалось вычетами 0, 10,j, oi;2 100, 0, 0000 (табл. 2) и .сигналы, которыми передавался вычет tt-z , исказились, в результате чего формирователь 1 сигнала стирания выдает сигнал на блок 6 управления и коммутация вычета, равного, например, I Oj, не происходит, что эквивалентно принятию всеми разрядами tt значений, равных нулю.

1206962

10

15

20

25

30

Из блока 8 памяти диапазона представления на преобразователь 5 числа из системы остаточных клас- сов в обобщенную позиционную систему поступает значение диапазона представления Р 21, а из блока 9 памяти базисных векторов поступают значения ортогональных базисов.

Число вычисляется по формуле А «(В +(x:jB,jV,B, -0 Р, 2x70 + 0x21 + 0x15 -9x21 14.

Формула изобретения

1. Устройство для коррекции ошибок в информации, представленной в системе остаточных классов, содержащее регистр и преобразователь числа из системы остаточных классов в обобщенную позиционную систему счисления, отличающееся тем, что, с целью повышения достоверности передаваемой информации, в него введены фop шpoвaтeль сигнала стирания, демодулятор, коммутатор, блок управления, дешифратор, блок памяти диапазона представления и блок памяти ортогональных базисов.

вход демодулятора объединен с входом формирователя сигнала стирания и является входом устройства, а выход демодулятора подключен к входу регистра, выходы которого подключены к информационным входам коммутатора управляющие входы которого объединены с соответствующими входами дешифратора и подключены к соответствующим выходам блока управления, вход которого соединен с выходом формиро- в ателя сигнала стирания, первый выхо дешифратора является выходом сигнала

Ошибка, а остальные через блок памяти диапазона представления соединены с первым входом преобразователя числа из системы остаточных классов в обобщенную позиционную систему счисления, вторые и третьи входы которого соединены.соответственно

с выходами коммутатора и блока памяти ортогональных базисов, а выход является выходом устройства, такто- йые входы всех блоков устройства соединены с тактовой шиной, а установочные входы блока управления и

13

201

2/0Редактор Л. Гратилло

Фиг.г

Составнтадь Л. Захаров

Техред А,.Бабинец Корректор Г. Решетник

Заказ 8734/59 Тираж 818Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал 1ШП Патент, г. Ужгород, ул. Проектная, 4

0

5

регистра подключены к шине обнуления.

2. Устройство по п. 1, о т л и- чающееся тем, что блок управления содержит первую и вторую группы регистров, группу элементов И и группу триггеров, первый вход первого элемента И и вход первого регистра первой группы объединены и соединены с тактовым входом блока управления, выход каждого регистра первой группы соединен с входом последующего регистра этой группы, кроме последнего, и с первым входом соответствующего элемента И, вторые входы элементов И объединены и подключены к входу блока управления, а выходы - соединены с входами соответствующих регистров второй группы, вьтоды которых подключены к входам соответствующих триггеров, выходы которых соединены с соответствующими выходами блока управления, установочные входы триггеров и регистров первой и второй групп объединены и подключены к установочному входу блока управления.

Л

22

18

17

Г8

22

Л

19

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1569996A1 |

| Устройство для перевода чисел из системы остаточных классов и расширения оснований | 2020 |

|

RU2744815C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С ПЕРЕСЧЕТОМ ОРТОГОНАЛЬНЫХ БАЗИСОВ | 2005 |

|

RU2298873C1 |

| УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ НА ОСНОВЕ ИНТЕРВАЛЬНО-ПОЗИЦИОННЫХ ХАРАКТЕРИСТИК | 2014 |

|

RU2557444C1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ РАСШИРЕНИЯ КОРТЕЖА ЧИСЛОВОЙ СИСТЕМЫ ВЫЧЕТОВ | 2003 |

|

RU2256226C2 |

| АППАРАТУРА РАДИОСВЯЗИ С ОРТОГОНАЛЬНЫМ ЧАСТОТНЫМ МУЛЬТИПЛЕКСИРОВАНИЕМ | 2005 |

|

RU2297721C2 |

| Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок | 1991 |

|

SU1797119A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться в аппаратуре передачи данных, функционирующей с кодами системы остаточных классов. Цель изобретения - повышение достоверности передаваемой информации. Устройство содержит формирователь I сигнала стирания, демодулятор 2, регистр 3, коммутатор 4, преобразователь 5 числа из системы остаточных классов в обобщенную позиционную систему, блок 6 управления, состоящий из группы элементов 1.5 И, двух групп регистров 16 и 17 и группы триггеров 18, а также дешифратор 7 , блок 8 памяти диапазона представления, блок 9 памяти ортогрналь- (з ных базисов, вход 10, выход 11, так товую шину 12, шину 13 обнуления и выход 14 сигнала Ошибка. 1 з.п. ф-лы, 2 ил.

| Акушский И.Я., Юдицкий Д.И | |||

| Машинная арифметика в остаточных классах | |||

| М.: Советское радио, 1968, с | |||

| Деревобетонный каток | 1916 |

|

SU351A1 |

| Устройство для обнаружения ошибокВ иНфОРМАции, пРЕдСТАВлЕННОй B СиСТЕМЕОСТАТОчНыХ КлАССОВ | 1979 |

|

SU798846A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-23—Публикация

1984-06-05—Подача