ел

О5 СО О Ј О

Изобретение относится к вычислительной технике и предназначено для применения в цифровых вычислительных машинах и устройствах обмена информа- j ции, а также для повышения достоверности в системах передачи данных.

Целью изобретения является сокращение аппаратурных затрат.

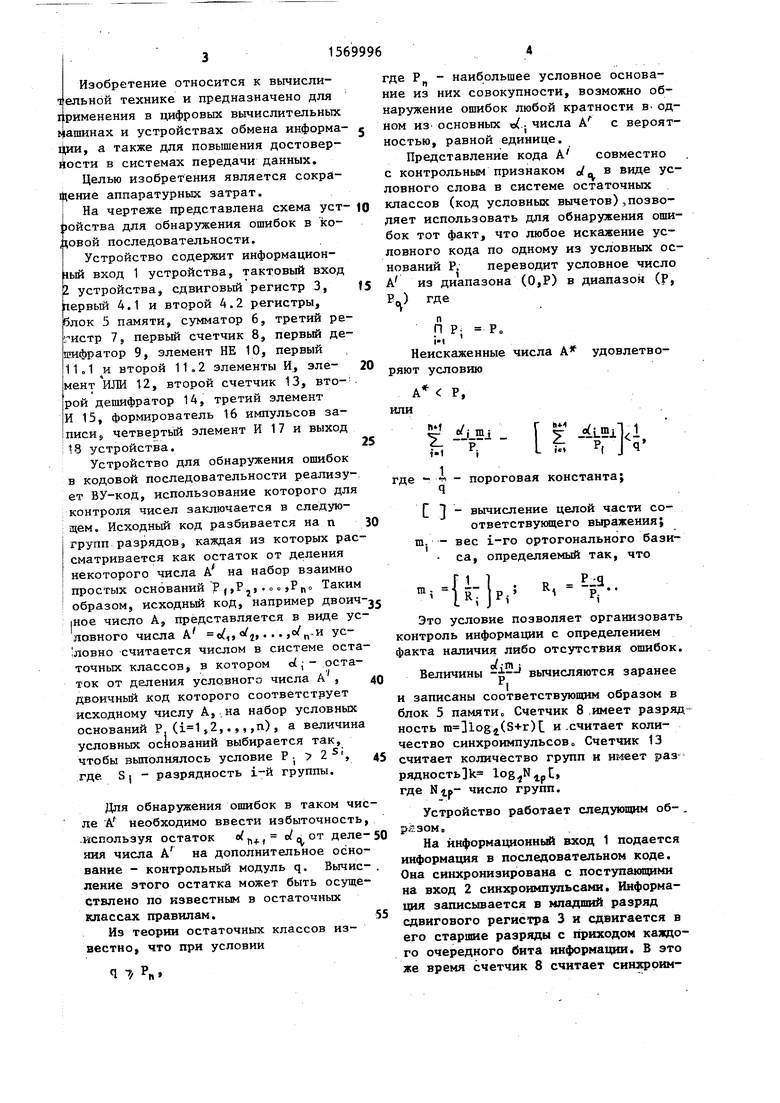

На чертеже представлена схема уст- Ю ройства для обнаружения ошибок в кодовой последовательности.

Устройство содержит информационный вход 1 устройства, тактовый вход 2 устройства, сдвиговый регистр 3, 15 первый 4.1 и второй 4.2 регистры, блок 5 памяти, сумматор 6, третий ре- истр 7, первый счетчик 8, первый де- атфратор 9, элемент НЕ 10, первый 11.1 и второй 11.2 элементы И, эле- 20 мент ИЛИ t2, второй счетчик 13, вто- рой дешифратор 14, третий элемент И 15, формирователь 16 импульсов записи, четвертый элемент И 17 и выход 18 устройства.25

Устройство для обнаружения ошибок в кодовой последовательности реализует ВУ-код, использование которого для контроля чисел заключается в следующем. Исходный код разбивается на п 30 групп разрядов, каждая из которых рассматривается как остаток от деления некоторого числа А на набор взаимно простых оснований Р fP , . „. ,Р„о Таким образом, исходный код, например двоич- iHoe число А, представляется в виде условного числа А /,, о/2,.. . ,с/п и ус- ловно считается числом в системе остаточных классов, в котором о(, - остаток от деления условного числа А1, д двоичный код которого соответструет исходному числу А, на набор условных оснований Р (,2,.,,,п), а величина условных оснований выбирается так, чтобы выполнялось условие Р. 2Sl, 4 где. S| - разрядность i-й группы.

Для обнаружения ошибок в таком числе А необходимо ввести избыточность, используя остаток °(ь-и о,от деле-5 ния числа А на дополнительное основание - контрольный модуль q. Вычис- . ление этого остатка может быть осуществлено по известным в остаточных классах правилам.5

Из теории остаточных классов известно, что при условии

П Р„,

где Р„ - наибольшее условное основание из них совокупности, возможно обнаружение ошибок любой кратности в одном из основных d. числа Ал с вероятностью, равной единице.

Представление кода А совместно с контрольным признаком J в виде условного слова в системе остаточных классов (код условных вычетов),позволяет использовать для обнаружения ошибок тот факт, что любое искажение условного кода по одному из условных оснований Р. переводит условное число А из диапазона (0,Р) в диапазон (Р, Р) где

п

ПР; i-i

Р.

Неискаженные числа А удовлетворяют условию

А Р, или

JJ®i

D

Р.

Ј

I & р, JV

1

- пороговая константа;

3 вычисление целой части соответствующего выражения; - вес 1-го ортогонального базиса, определяемый так, что

га

-1М . й

р.а

V

Это условие позволяет организовать контроль информации с определением факта наличия либо отсутствия ошибок.

Величины -Ј- вычисляются заранее

1 и записаны соответствующим образом в

блок 5 памятио Счетчик 8 имеет разрядность (S+r){. и .считает количество синхроимпульсов о Счетчик 13 считает количество групп и имеет раз - рядность к log4Nlpt, где N tp- число групп.

Устройство работает следующим об- . рлзом.

На информационный вход 1 подается информация в последовательном коде. Она синхронизирована с поступающими на вход 2 синхроимпульсами Информация записывается в младший разряд сдвигового регистра 3 и сдвигается в его старшие разряды с приходом каждого очередного бита информации. В это же время счетчик 8 считает синхроим

5 1

пульсы и выдает результат в двоичной форме на вход дешифратора 9. С приходом первого синхроимпульса с первого выхода дешифратора 9 выдается команд на считывание из блока 5 памяти информации, находящейся по адресу, который определяет состояния регистров 4.1 и 4.2 и счетчика 13, с второго - команда записи информации в регистр 7 с выхода сумматора 6, причем формирователь 16 импульсов записи обеспечивает такую длительность сигнала записи в регистр 7, при которой не проиходит многократное суммирование и запись его результатов в регистр 7, с третьего - команда установки в нуль регистра 4.2 и разрешение на считывание информации о результатах контроля информации в преаыдущем такге со знакового -(старшего) разряда регистр 7, которая подается на один из входов элемента И 17.

На выходе элемента И 17, т.е. на выходе 18 устройства, присутствует О, так как в тот момент в знаковом разряде регистра 7 записан О. Описан такт работы устройства при приеме первой группы. Сама группа в это время накапливается в сдвиговом регистре 3„ С приходом S-ro синхроимпульса сигнал с S-ro выхода дешифратора 9 поступает на вход элемента И 15. Так как дешифратор 14 находится в нулевом состоянии (сигнал на его первом выходе), то на элементе И 15 вырабатывается сигнал установки в О регистра 7. Кроме того, с S-ro выход дешифратора 9 на элемент ИЛИ 12 подается единичный сигнал.На второй вход эт го элемента воздействует единичный сигнал, поступающий с элемента НЕ 10, так как на его вход с выхода дешифратора 14 подается О (в сдвиговом регистре накапливается последняя группа) . При совпадении двух единиц на входах элемента И 11„2 на его выходе появляется 1, которая, проходя через элемент ИЛИ 12, сбрасывает в О счетчик 8, увеличивает показания счет чика 13, разрешает запись битов первой группы из сдвигового регистра 3 в регистр 4.1„ При этом формируется адрес выборки для блока 5 памяти из номера,группы в двоичном коде, кодовой комбинации группы в регистре 4„1 и нулей в регистре ,4 „ 2, подается запрет считывания знакового разряда ре- гистоа 7 на элемент И 17„

хроимпульса на

Далее в сдвиговом регистре 3 начинает формироваться вторая группа. С приходом первого бита второй группы с первого выхода дешифратора 9 по сформированному адресу выбирается информация из блока 5 памяти. Эта информация подается на вход первого слагаемого сумматора 6 и складывается с числом, находящимся на входе второго слагаемого этого сумматора 6, которое записано в регистре 7. Полученная сум-; ма записывается в регистр 7 по едкл . ному сигналу с третьего выхода дешиф ратора 9, в которое он устанавлил.. ся с приходом третьего синхроимпульса. В этом такте считывание знакового разряда и обнуления регистра 7 не производится Далее с приходом остальных групп все операции повторяются В первом рабочем такте из блока 5 памяти выбирается число

Л --- - - Р, q

где о/ - остаток по первому основанию.

представленный в двоичной форме и пе

редаваемой по каналам связи,

в остальных тактах из блока 5 памяти

выбирается

импуль

Р;

хроимпульса на

При обработке последней группы на последнем выходе дешифратора 14 устанавливается единица , Теперь на входе элемента И 11.2 устанавливается нуль, полученный с выхода элемента НЕ 10, а на выходе элемента И 11„1 устанавливается 1м, С приходом S+r-ro синвходе элемента 11.1

появляется еще одна 1. В результате на выходе этого элемента появляется 1, которая разрешает запись информации, регистр 4.2 обнуляет счетчик 13;и, проходя через элемент ИЛИ 12, разрешает запись в регистр 4.1 остальной части остатка по контрольному основанию и обнуляет счетчик 8. Тогда на адресном входе блока 5 памяти формируется адрес S+r битов остатка по контрольному основанию и номер группы.

хроимпульса на

После этого начинает приниматься следующий блок данных. С приходом первого бита этого блока по сформированhlj;

Р гк

го - суммирование в сумматоре, третьего - обнуления регистра 4.2, считываному адресу выбирается o( второние информации со знакового разряда регистра 7, S-ro - обнуление регистра 7. Устройство готово к обработке нового блока данных. Появление на выходе 18 1 свидетельствует о наличии ошибки в обработанном блоке данных.

Формула изобретения

Устройство для обнаружения ошибок в кодовой последовательности, содержащее первый, второй и третий регистры, блок памяти, сумматор, первый и второй счетчики, первый и второй де- шифраторы, элемент НЕ, первый и второй элементы И и элемент ИЛИ, причем тактовый вход устройства соединен со счетным входом первого счетчика, выход которого соединен с входом первого дешифратора, выход блока памяти соединен с входом первого слагаемого сумматора, выход которого соединен с информационным входом третьего регистра, выходы разрядов которого соединены с входами разрядов второго слагаемого сумматора, выходы разрядов нго- рого счетчика соединены с входами разрядов второго дешифратора, выход первого элемента И соединен с первым входом элемента ИЛИ, выход элемента НЕ соединен с первым входом второго элемента И, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит сдвиго- вый регистр, третий и четвертый элементы И, формирователь импульсов записи, причем информационный и тактовый входы устройства соединены соответственно с входом младшего разряда и с входом разрешения сдвига сдвигового регистра, выходы с первого по S-й разрядов (S - максимальное количество двоичных разрядов, необходимое для представления остатка по рабочему основанию) и выходы с (S-H)-ro по

0

|$ 2Q 2530 -35 до 45

(S+r)-ft (S+r - количество двоичных разрядов, необходимое для представления остатка по контрольному основанию) разрядов которого соединены соответственно с входами разрядов информационных входов первого и второго регистров, выходы разрядов которых и выходы разрядов второго счетчика соединены соответственно с входами разрядов адресного входа блока памяти, вход разрешения считывания которого соединен с первым выходом первого дешифратора, второй выход которого через формирователь импульсов записи соединен с входом разрешения записи третьего регистра, вход установки в О которого соединен с выходом третьего элемента И, первый вход которого соединен с первым выходом второго дешифратора и с первым входом четвертого элемента И, выход которого является выходом устройства, третий выход первого дешифратора соединен с входом установки в О второго регистра и с вторым входом четвертого элемента И, третий вход которого соединен с выходом старшего разряда третьего регистра, S-й выход первого дешифратора соединен с вторым входом третьего элемента И и с вторым входом второго элемента И, выход которого соединен с втр- вторым входом элемента ИЛИ, выход которого соединен с входом разрешения записи первого регистра, со счетным входом второго счетчика и с входом установки в О первого счетчика, (S+ +г)-й выход первого дешифратора соединен с первым входом первого элемента И, выход которого соединен с входом установки в О второго счетчика и с входом разрешения записи второго регистра, последний выход второго дешифратора соединен с вторьм входом первого элемента И и с входом элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для извлечения корня п-й степени | 1979 |

|

SU883898A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для вычитания | 1987 |

|

SU1418703A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Цифровой фильтр | 1982 |

|

SU1059670A1 |

Изобретение относится к вычислительной технике и предназначено для применения в цифровых устройствах обработки, хранения и передачи данных, а также в устройствах повышения достоверности в системах передачи данных. Целью изобретения является сокращение аппаратурных затрат. Устройство для обнаружения ошибок в кодовой последовательности содержит сдвиговый регистр 3, регистры 4.1, 4.2 и 7, блок 5 памяти, сумматор 6, счетчики 8 и 13, дешифраторы 9 и 14, элемент НЕ 10, элементы И 11.1, 11.2, 15 и 17, элемент ИЛИ 12 и формирователь 16 импульсов записи с соответствующими связями. В устройстве признак ошибки вырабатывается после анализа знака разности принимаемого числа, представленного в коде условных вычетов, и пороговой константы, вычисляемой заранее. При возникновении ошибки в одном из остатков принятое число выходит за границу диапазона, при этом в знаковом рязряде сумматора 6 вырабатывается "1", в противном случае - "0". Таким образом ошибка обнаруживается. 1 ил.

| Устройство для обнаружения ошибок в системе остаточных классов | 1986 |

|

SU1399743A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-20—Подача