11

Изобретение относи1 ся к области управления производственными процессами и может быть использовано в дискретных системах управления, например, в угольной и горнорудной промышленности (управление шахтным рельсовым транспортом, водоотливными установками и т.д.).

Целью изобретения является упрощение устройства, что приведет и к повышению его надежности.

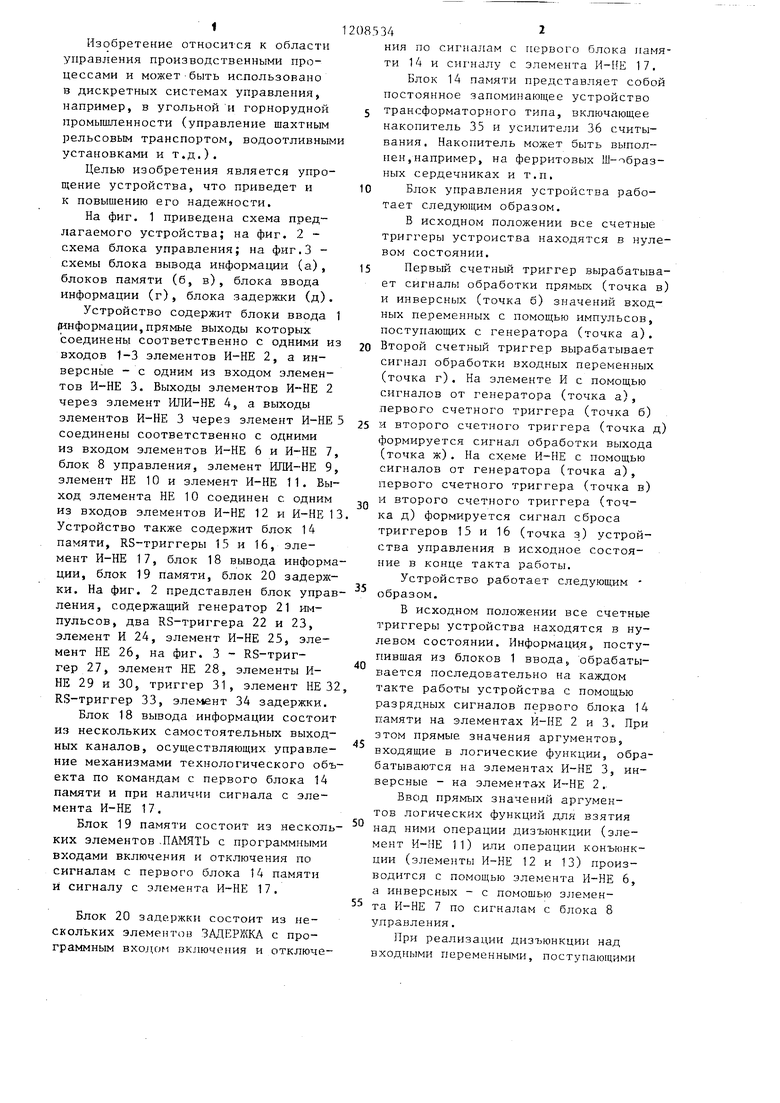

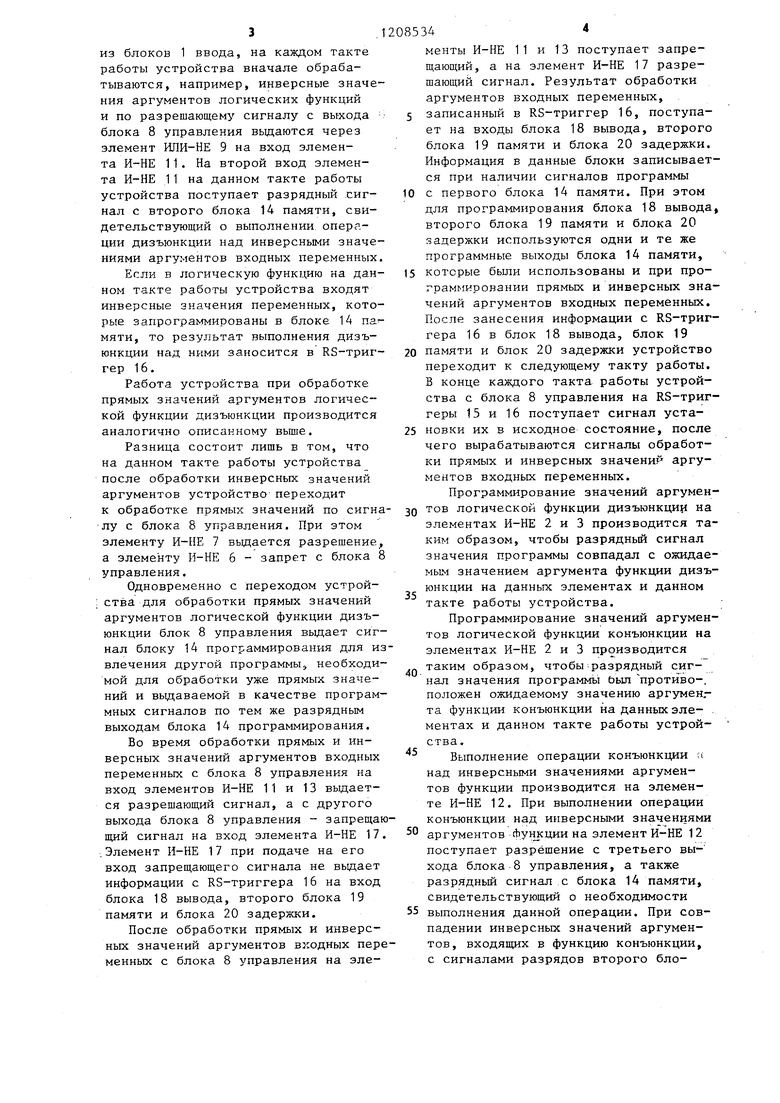

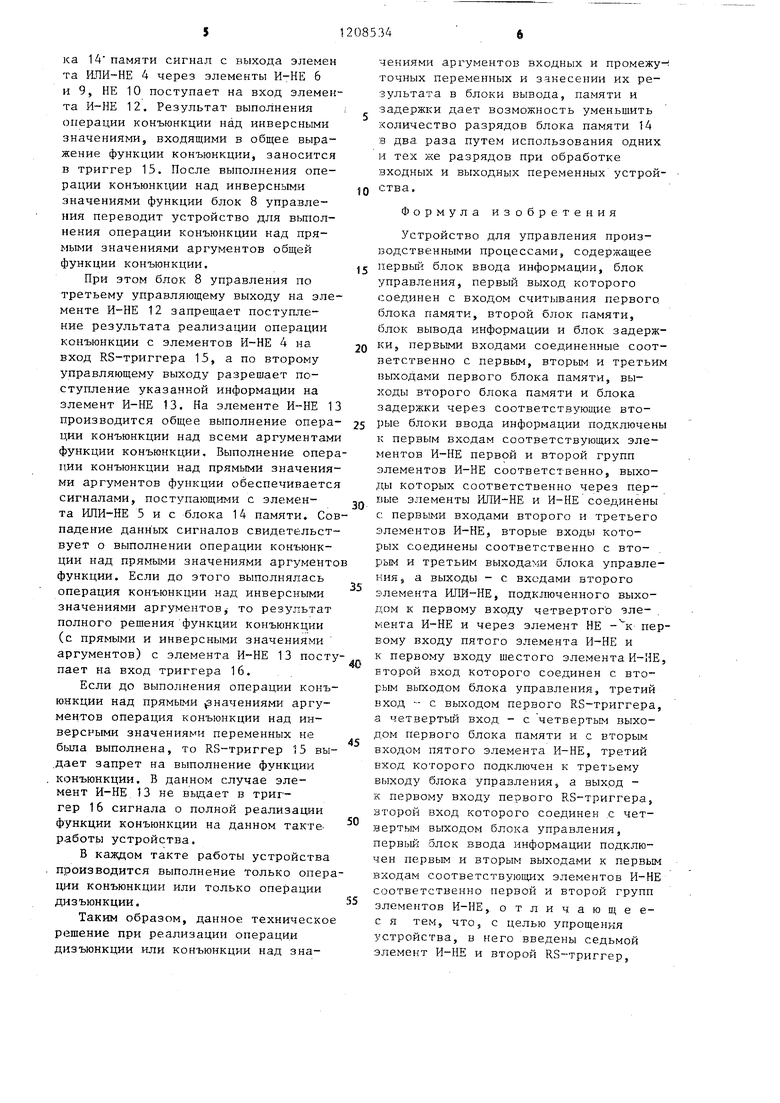

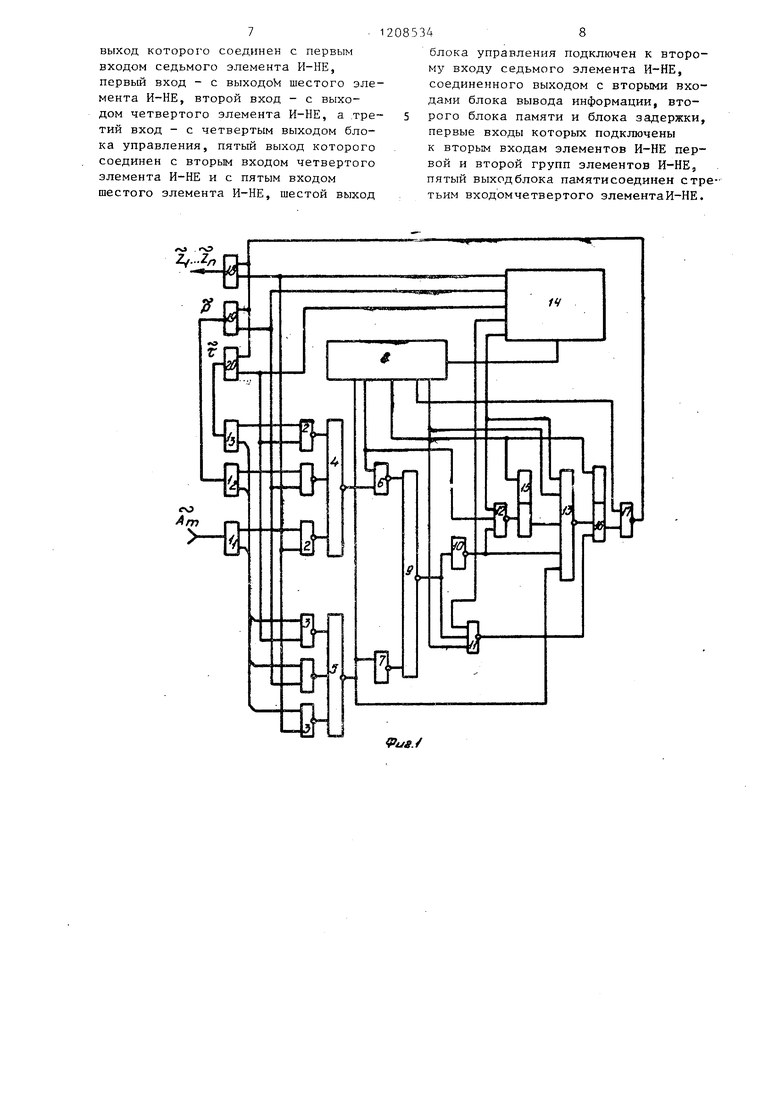

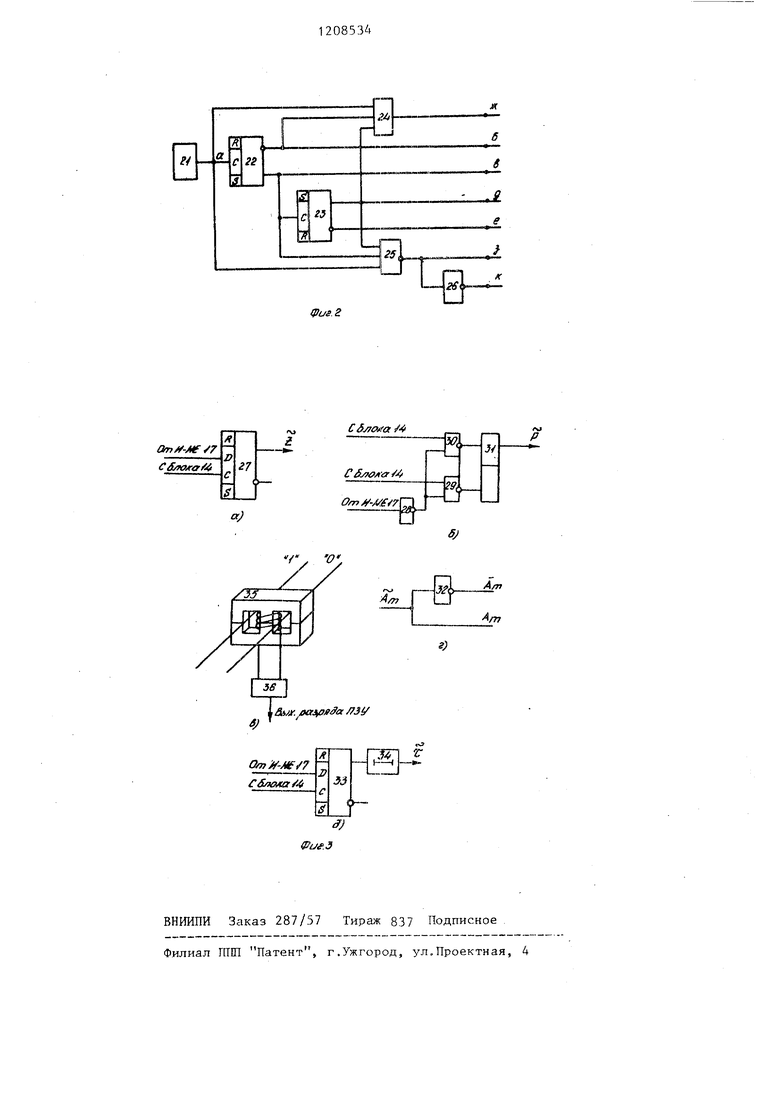

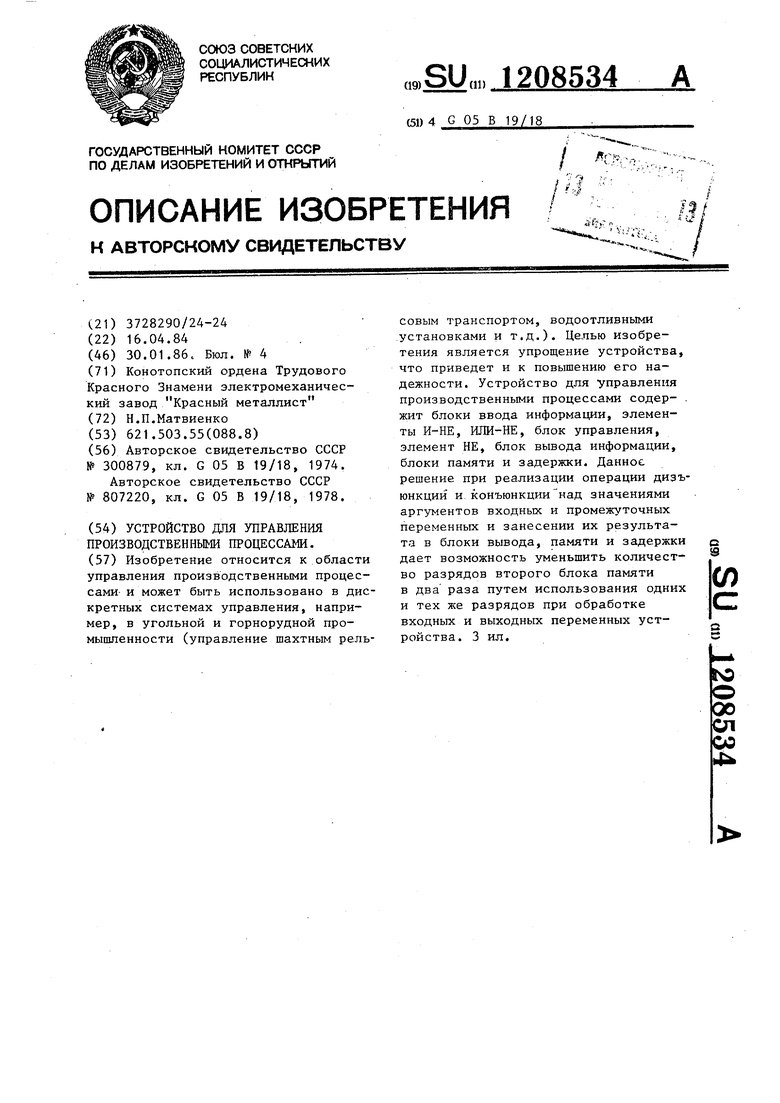

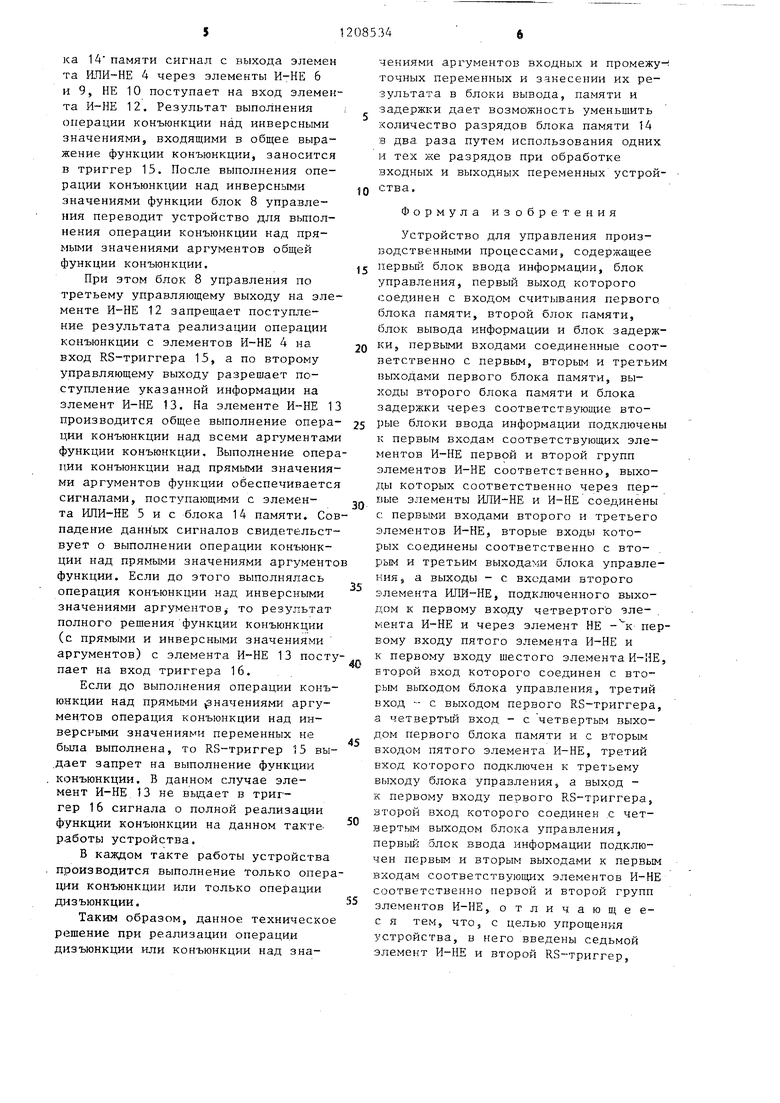

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - схема блока управления; на фиг.З - схемы блока вывода информации (а), блоков памяти (б, в), блока ввода информации (г), блока задержки (д).

Устройство содержит блоки ввода 1 (информации,прямые выходы которых соединены соответственно с одними из входов 1-3 элементов И-НЕ 2, а инверсные - с одним из входом элементов И-НЕ 3, Выходы элементов И-НЕ 2 через элемент ИЛИ-НЕ 4, а выходы элементов И-НЕ 3 через элемент И-НЕ 5 соединены соответственно с одними из входом элементов И-НЕ 6 и И-НЕ 7, блок 8 управления, элемент И1Ш-НЕ 9, элемент НЕ 10 и элемент И-НЕ 11. Выход элемента НЕ 10 соединен с одним из входов элементов И-НЕ 12 и И-НЕ 13 Устройство также содержит блок 14 памяти, RS-триггеры 15 и 16, элемент И-НЕ 17, блок 18 вывода информации, блок 19 памяти, блок 20 задержки. На фиг. 2 представлен блок управления, содержащий генератор 21 пульсов, два RS-триггера 22 и 23, элемент И 24, элемент И-НЕ 25, элемент НЕ 26, на фиг. 3 - RS-триг- гер 27, элемент НЕ 28, элементы И- НЕ 29 и 30, триггер 31, элемент НЕ 32 RS-триггер 33, элемент 34 задержки.

Блок 18 вывода информации состоит из нескольких самостоятельных выходных каналов, осуществляющих управление механизмами технологического объекта по командам с первого блока 14 памяти и при наличии сигнала с элемента И-НЕ 17.

Блок 19 памяти состоит из нескольких элементов.ПАМЯТЬ с программными входами включения и отключения по сигналам с первого блока 14 памяти и сигналу с элемента И-НЕ 17,

Блок 20 задержки состоит из нескольких элементов ЗАДЕРЖКА с программным BXOJIOM включения и отключе

342

ния по сигналам с первого блока памяти 14 и сигналу с элемента И-НЕ 17.

Блок 14 памяти представляет собой постоянное запоминающее устройство трансформаторного типа, включающее накопитель 35 и усилители 36 считывания. Накопитель может быть выполнен, например, на ферритовых Ш-образ- ных сердечниках и т.п.

Блок управления устройства работает следующим образом.

В исходном положении все счетные триггеры устройства находятся в нулевом состоянии.

Первый счетный триггер вырабатывает сигналы обработки прямых (точка в) и инверсных (точка б) значений входных переменных с помощью импульсов, поступающих с генератора (точка а). Второй счетный триггер вырабатывает сигнал обработки входных переменных (точка г). На элементе И с помощью сигналов от генератора (точка а), первого счетного триггера (точка б) и второго счетного триггера (точка д) формируется сигнал обработки выхода (точка ж). На схеме И-НЕ с помощью сигналов от генератора (точка а), первого счетного триггера (точка в) и второго счетного триггера (точка д) формируется сигнал сброса триггеров 15 и 16 (точка з) устройства управления в исходное состояние з конце такта работы.

Устройство работает следующим образом.

В исходном положении все счетные триггеры устройства находятся в нулевом состоянии. Информация, поступившая из блоков 1 ввода, обрабатывается последовательно на каждом такте работы устройства с помощью разрядных сигналов первого блока 14 памяти на элементах И-НЕ 2 и 3. При этом прямые значения аргументов, входящие в логические функции, обрабатываются на элементах И-НЕ 3, инверсные - на элементах И-НЕ 2 .Ввод прямых значений аргументов логических функций для взятия над ними операции дизъюнкции (элемент И-НЕ 11) или операции коньюнк- ции (элементы И-НЕ 12 и 13) производится с помощью элемента И-НЕ 6, а инверсных - с помошью элемента И-НЕ 7 по сигналам с блока 8 управления.

При реализации дизъюнкции над входными переменными, поступающими

3.

из блоков 1 ввода, на каждом такте работы устройства вначале обрабатываются, например, инверсные значения аргументов логических функций и по разрешающему сигналу с вы-хода блока 8 управления выдаются через элемент ИЛИ-НЕ 9 на вход элемента И-НЕ 11. На второй вход элемента И-НЕ 11 на данном такте работы устройства поступает разрядный сигнал с второго блока 14 памяти, свидетельствующий о выполнении операции дизъюнкции над инверсными значениями аргументов входных переменных.

Если в логическую функцию на данном такте работы устройства входят инверсные значения переменных, которые запрограммированы в блоке 14 памяти, то результат выполнения дизъюнкции над ними заносится в RS-триг- гер 16.

Работа устройства при обработке прямых значений аргументов логической функции дизъюнкции производится аналогично описанному выше.

Разница состоит лишь в том, что на данном такте работы устройства после обработки инверсных значений аргументов устройство переходит к обработке прямых значений по сигна лу с блока 8 управления. При этом элементу И-НЕ 7 выдается разрешение а элементу 6 - запрет с блока 8 управления.

Одновременно с переходом устройства для обработки прямых значений аргументов логической функции дизъюнкции блок 8 управления вьщает сигнал блоку 14 программирования для из влечения другой программы, необходимой для обработки уже прямых значений и вьщаваемой в качестве программных сигналов по тем же разрядным выходам блока 14 программирования.

Во время обработки прямых и инверсных значений аргументов входных переменных с блока 8 управления на вход элементов И-НЕ 11 и 13 выдается разрешающий сигнал, а с другого выхода блока 8 управления - запрещающий сигнал на вход элемента И-НЕ 17. .Элемент И-НЕ 17 при подаче на его вход запрещающего сигнала не выдает информации с RS-триггера 16 на вход блока 18 вывода, второго блока 19 памяти и блока 20 задержки.

После обработки прямых и инверсных значений аргументов входных переменных с блока 8 управления на эле08534

менты И-НЕ 11 и 13 поступает запрещающий, а на элемент И-НЕ 17 разрешающий сигнал. Результат обработки аргументов входных переменных,

5 записанный в RS-триггер 16, поступает на входы блока 18 вывода, второго блока 19 памяти и блока 20 задержки. Информация в данные блоки записывается при наличии сигналов программы

10 с первого блока 14 памяти. При этом для программирования блока 18 вывода, второго блока 19 памяти и блока 20 задержки используются одни и те же программные выходы блока 14 памяти,

15 которые были использованы и при программировании прямых и инверсных значений аргументов входных переменных. После занесения информации с RS-триггера 16 в блок 18 вывода, блок 19

20 памяти и блок 20 задержки устройство переходит к следующему такту работы. В конце каждого такта работы устройства с блока 8 управления на RS-триг- геры 15 и 16 поступает сигнал уста25 новки их в исходное состояние, после чего вырабатываются сигналы обработки прямых и инверсных значений аргументов входньк переменных.

Программирование значений аргумен- 30 го логической функции дизъюнкции на элементах И-НЕ 2 и 3 производится таким образом, чтобы разрядньй сигнал значения программы совпадал с ожидаемым значением аргумента функции дизъюнкции на данных элементах и данном такте работы устройства.

Программирование значений аргументов логической функции конъюнкции на элементах И-НЕ 2 и 3 производится таким образом, чтобы разрядный сигнал значения программы Ььш Ъротиво-. положен ожидаемому значению аргумен,- та функции конъюнкции на данных эле- . ментах и данном такте работы устройства.

Выполнение операции конъюнкции а над инверсными значениями аргументов функции производится на элементе И-НЕ 12. При выполнении операции конъюнкции над инверсными значениями

аргументов функции на элемент и -НЕ 12 поступает разрешение с третьего выхода блока 8 управления, а также разрядный сигнал с блока 14 памяти, свидетельствующий о необходимости

55 выполнения данной операции. При совпадении инверсных значений аргументов, входящих в функцию конъюнкции, с сигналами разрядов второго бло35

40

ка 14 памяти сигнал с выхода элемен та ИЛИ-НЕ 4 через элементы И-НЕ 6 и 9, НЕ 10 поступает на вход элемента И-НЕ 12. Результат выполнения операции конъюнкции над инверсными значениями, входящими в общее выражение функции конъюнкции, заносится в триггер 15. После выполнения операции конъюнкции над инверсными значениями функции блок 8 управления переводит устройство для выполнения операции конъюнкции над прямыми значениями аргументов общей функции конъюнкции.

При этом блок 8 управления по третьему управляющему выходу на элементе И-НЕ 12 запрещает поступление результата реализации операции конъюнкции с элементов И-НЕ 4 на вход RS-триггера 15, а по второму управляющему выходу разрешает поступление указанной информации на элемент И-НЕ 13. На элементе И-НЕ 13 производится общее выполнение операции конъюнкции над всеми аргументами функции конъюнкции. Выполнение опера пин конъюнкции над прямыми значениями аргументов функции обеспечивается сигналами, поступающими с элемента ИЛИ-НЕ 5 и с блока 14 памяти. Совпадение данн ых сигналов свидетельствует о выполнении операции конъюнкции над прямыми значениями аргументо функции. Если до этого выполнялась операция конъюнкции над инверсными значениями аргументов то результат полного решения функции конъюнкции (с прямыми и инверсными значениями аргументов) с элемента И-НЕ 13 поступает на вход триггера 16.

Если до выполнения операции конъюнкции над прямыми значениями аргументов операция конъюнкции над инверсными значениями переменных не была выполнена, то RS-триггер 15 вы- .дает запрет на выполнение функции конъюнкции. В данном случае элемент И-НЕ.13 не выдает в триггер 16 сигнала о полной реализации функции конъюнкции на данном такте- работы устройства.

В каждом такте работы устройства производится выполнение только операции конъюнкции или только операции дизъюнкции.

Таким образом, данное техническое решение при реализации операции дизъюнкции или конъюнкции над знаO

5

чениями аргументов входных и промежу-f точных переменных и занесении их результата в блоки вывода, памяти и задержки дает возможность уменьшить количество разрядов блока памяти 14 в два раза путем использования одних и тех же разрядов при обработке входных и выходных переменных устройства.

Формула изобретения

Устройство для управления производственными процессами, содержащее первый блок ввода информации, блок управления, первый выход которого соединен с входом считывания первого, блока памяти, второй блок памяти, блок вывода информации и блок задерж- Q ки, первыми входами соединенные соответственно с первьм, вторым и третьим выходами первого блока памяти, выходы второго блока памяти и блока задержки через соответствующие вторые блоки ввода информации подключены к первым входам соответствующих элементов И-НЕ первой и второй групп элементов И-НЕ соответственно, выходы которых соответственно через первые элементы ИЛИ-НЕ и И-НЕ соединены с первыми входами второго и третьего элементов И-НЕ, вторые входы которых соединены соответственно с вторым и третьим выходами блока управле5

ния J а выходы - с входами второго элемента ИЯй-НЕ, подключенного выходом к первому входу четвертого эле- . мента И-НЕ и через элемент НЕ первому входу пятого элемента И-НЕ и к: первому входу шестого элемента И-ИЕ, второй вход которого соединен с вторым выходом блока управления, третий вход - с выходом первого RS-триггера, а четвертый вход - с четвертым выходом первого блока памяти и с вторым входом пятого элемента И-НЕ, третий вход которого подключен к третьему выходу блока управления, а вых.од - к первому входу первого RS-триггера, второй вход которого соединен .с четвертым выходом блока управления, первый блок ввода информации подключен первым и вторым выходами к первым входам соответствую цих элементов И-НЕ соответственно первой и второй групп элементов И-НЕ, отличающее- с я тем, что, с целью упрощения устройства, в него введены седьмой элемент И-НЕ и второй RS-триггер,

7

выход KOTopoi o соед.инен с первым входом седьмого элемента И-НЕ, первый вход - с выxoдok шестого эле мента И-НЕ, второй вход - с выходом четвертого элемента И-НЕ, а тре тий вход - с четвертым выходом блока управления, пятый выход которого соединен с вторым входом четвертого элемента И-НЕ и с пятым входом шестого элемента И-НЕ, шестой выход

2085348

блока управления подключен к второму входу седьмого элемента И-НЕ, соединенного выходом с вторыми входами блока вывода информации, вто- 5 рого блока памяти и блока задержки, первые входы которых подключены к вторым входам элементов И-НЕ первой и второй групп элементов И-НЕ, пятый выходблока памятисоедииен с третьим входомчетвертого элементаИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления производ-СТВЕННыМи пРОцЕССАМи | 1978 |

|

SU807220A1 |

| Устройство для управления производственными процессами | 1984 |

|

SU1254438A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для автоматического управления производственными процессами | 1974 |

|

SU547727A1 |

| Устройство для определения значений булевых функций | 1990 |

|

SU1805462A1 |

| Устройство для определения значений булевых функций | 1987 |

|

SU1508204A1 |

| Устройство для определения значений буле-ВыХ фуНКций | 1979 |

|

SU840882A1 |

| Устройство для определения значений булевых функций | 1982 |

|

SU1037240A1 |

| Устройство для вычисления булевых функций | 1986 |

|

SU1372319A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

Изобретение относится к области управления производственными процессами- и может быть использовано в дискретных системах управления, например, в угольной и горнорудной промышленности (управление шахтным рельсовым транспортом, водоотливными установками и т.д.). Целью изобретения является упрощение устройства, что приведет и к повышению его надежности. Устройство для управления производственными процессами содер- . жит блоки ввода информации, элементы И-НЕ, ИЛИ-НЕ, блок управления, элемент НЕ, блок вывода информации, блоки памяти и задержки. Данное решение при реализации операции дизъюнкций и конъюнкции над значениями аргументов входных и промежуточных переменных и занесении их результата в блоки вывода, памяти и задержки дает возможность уменьшить количество разрядов второго блока памяти в два раза путем использования одних и тех же разрядов при обработке входных и выходных переменных устройства. 3 ил. Q ® (Л с

ЛЛ .

Lia.f

гб

г

27

/4

«41

p

ю

.

S)

Om V-Mftf

S3

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ПРОИЗВОДСТВЕННЫМИ ПРОЦЕССАМИ | 0 |

|

SU300879A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для управления производ-СТВЕННыМи пРОцЕССАМи | 1978 |

|

SU807220A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-01-30—Публикация

1984-04-16—Подача